Abstract

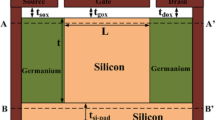

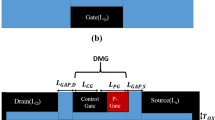

In this paper, we have proposed a device and named it dual electrode doping-less TFET (DEDLTFET), in which electrodes on top and bottom of source and drain are considered to enhance the ON state current and Analog performances. The charge plasma technique is used to generate electron’s and hole’s clouding depending upon their respective work functions at top and bottom of source/drain electrode. Band-to-band-tunneling rate is similar on both sides of source-channel junctions, which increases ON state current. The analog performance parameters of DEDLTFET are investigated and using device simulation the demonstrated characteristics are compared with doping-less (DLTFET) and the conventional doped double gate TFET (DGTFET), such as transconductance \((\hbox {g}_\mathrm{m})\), transconductance to drain current ratio \((\hbox {g}_\mathrm{m}/\hbox {I}_\mathrm{D})\), output-conductance (g\(_{d})\), output resistance \((\hbox {r}_\mathrm{d})\), early voltage \((\hbox {V}_\mathrm{EA})\), intrinsic gain \((\hbox {A}_\mathrm{V})\), total gate capacitance \((\hbox {C}_\mathrm{gg})\) and unity gain frequency \((\hbox {f}_\mathrm{T})\). From the simulation results, it is observed that DEDLTFET has significantly improved analog performance as compared to DGTFET and DLTFET.

Similar content being viewed by others

References

Koswatta, S.O., Lundstrom, M.S., Nikonov, D.E.: Performance comparison between p-i-n tunneling transistors and conventional MOSFETs. IEEE Trans. Electron. Devices 56(3), 456–465 (2009)

Colinge, J.P., Lee, C.W., Afzalian, A., Akhavan, N.D., Yan, R., Ferain, I., Razavi, P., O’Neill, B., Blake, A., White, M., Kelleher, A.M., McCarthy, B., Murphy, R.: Nanowire transistors without junctions. Nat. Nanotechnol. 5(3), 225–229 (2010)

Bhuwalka, K.K., Schulze, J., Eisele, I.: Scaling the vertical tunnel FET with tunnel bandgap modulation and gate work function engineering. IEEE Trans. Electron. Devices 52(5), 909–917 (2005)

Nirschl, T., Henzler, S., Fischer, J., Fulde, M., Bargagli-Stoffi, A., Sterkel, M., Sedlmeir, J., Weber, C., Heinrich, R., Schaper, U., Einfeld, J., Neubert, R., Feldmann, U., Stahrenberg, K., Ruderer, E., Georgakos, G., Huber, A., Kakoschke, R., Hansch, W., Schmitt-Landsiedel, D.: Scaling properties of the tunneling field effect transistor (TFET): device and circuit. Solid-State Electron. 50(1), 44–51 (2006)

Choi, W.Y., Park, B.G., Lee, J.D.: Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron. Device Lett. 28(8), 743–745 (2007)

Boucart, K., Ionescu, A.M.: Length scaling of the double gate tunnel FET with a high-k gate dielectric. Solid-State Electron. 21(11–12), 1500–1507 (2007)

Jagadesh Kumar, M., Janardhanan, Sindhu: Doping-less tunnel field effect transistor: design and investigation. IEEE Trans. Electron. Devices 60(10), 3285–3290 (2013)

Rahi, S.B., Ghosh, B., Asthana, P.: A simulation-based proposed high-k heterostructure AlGaAs/Si junctionless n-type tunnel FET. J. Semicond. 35(11), 114005–114015 (2014)

Ghosh, B., Akram, M.W.: Junctionless tunnel field effect transistor. IEEE Electron. Device Lett. 34(5), 584–586 (2013)

Jhaveri, R., Nagavarapu, V., Woo, J.C.S.: Effect of pocket doping and annealing schemes on the source-pocket tunnel field-effect transistor. IEEE Trans. Electron. Devices 58(1), 80–86 (2011)

Patel, Nayan, Ramesha, A., Mahapatra, Santanu: Drive current boosting of n-type tunnel FET with strained SiGe layer at source. Microelectron. J. 39, 1671–1677 (2008)

Damrongplasit, N., Shin, C., Kim, S.H., Liu, T.J.K.: Study of random dopant fluctuation effects in germanium-source tunnel FETs. IEEE Trans. Electron. Devices 58(10), 3541–3548 (2011)

Leung, G., Chui, C.O.: Stochastic variability in silicon doublegate lateral tunnel field-effect transistors. IEEE Trans. Electron. Devices 60(1), 84–91 (2013)

Hueting, R.J.E., Rajasekharan, B., Salm, C., Schmitz, J.: The charge plasma P-N diode. IEEE Electron. Device Lett. 29(12), 1367–1369 (2008)

Boucart, K., Ionescu, A.M.: Double gate tunnel FET with high-k gate dielectric. IEEE Trans. Electron. Devices 54(7), 1725–1733 (2007)

Omura, Y., Horiguchi, S., Tabe, M., Kishi, K.: Quantum-mechanical effects on the threshold voltage of ultrathin-SOI nMOSFETs. IEEE Trans. Electron. Devices 14(12), 569–571 (1993)

Rajasekharan, B., Hueting, R.J.E., Salm, C., van Hemert, T., Wolters, R.A.M., Schmitz, J.: Fabrication and characterization of the charge-plasma diode. IEEE Electron. Device Lett. 31(6), 528–530 (2010)

ATLAS User Manual: Device Simulation Software: Silvaco Int. Santa Clara (2012)

Luisier, M., Klimeck, G.: Simulation of nanowire tunneling transistors: from the Wentzel-Kramers-Brillouin approximation to full-band phonon-assisted tunneling. J. Appl. Phys. 107, 084507 (2010)

Sze, S.M.: Physics of Semiconductor Devices, 3rd edn. Wiley, New York (2008)

Ilatikhameneh, H., Klimeck, G., Appenzeller, J., Rahman, R.: Scaling theory of electrically doped 2D transistors. IEEE Electron. Device Lett. 36(7), 726–728 (2015)

Ilatikhameneh, H., Ameen, T.A., Klimeck, G., Appenzeller, J., Rahman, R.: Dielectric engineered tunnel field-effect transistor. IEEE Electron. Device Lett. doi:10.1109/LED.2015.2474147

Narang, R., Saxena, M., Gupta, R.S., Gupta, M.: Effect of Temperature and Gate Stack on the Linearity and Analog Performance of Double Gate Tunnel FET. Springer, Berlin Heidelberg (2011)

Kilchytska, V., Neve, A., Vancaillie, L., Levacq, D., Adriaensen, S., van Meer, H., de Meyer, K., Raynaud, C., Dehan, M., Raskin, J.P., Flandre, D.: Influence of device engineering on the analog and RF performances of SOI MOSFETs. IEEE Trans. Electron. Devices 50(3), 577–588 (2003)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Anand, S., Amin, S.I. & Sarin, R.K. Analog performance investigation of dual electrode based doping-less tunnel FET. J Comput Electron 15, 94–103 (2016). https://doi.org/10.1007/s10825-015-0771-4

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-015-0771-4