Abstract

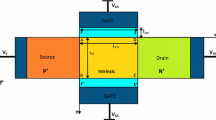

In this paper, we present a physics based semi-analytical model for channel potential of symmetric double gate tunnel field effect transistor (TFET). The analytical results are compared with TCAD Sentaurus simulated data. We have used a fitting parameter \(\lambda \), which represents the screening length (or Debye length) of the device, in this work this fitting parameter is studied with the help of rigorous simulations. This fitting parameter will determine the I–V characteristics of the TFET device, therefore we also tried to show its behavior with changes in applied gate and drain voltages. To show the robustness of our model the results with variations in channel length and film thickness are also presented with simulated results. This model gives the RMS residual error within 0.8–5.0 % and asymptotic standard error for \(\lambda \) within 0–4.0 % and works well for \(L_{g}\le 150\) nm and \(T_{si}\ge 8\) nm.

Similar content being viewed by others

References

Koswatta, S.O., Lundstrom, M.S., Nikonov, D.E.: Performance comparison between p-i-n tunneling transistors and conventional MOSFETs. IEEE Trans. Electron. Devices 56(3), 456–465 (2009)

The international technology roadmap for semiconductors (ITRS-2013): Electronic research devices (2013). http://www.itrs.net/ITRS%201999-2014%20Mtgs,20Presentations%20&%20Links/2013ITRS/Summary2013.htm

Zhang, Q., Seabaugh, A.: Can the interband tunnel FET outperform Si CMOS?. Device research conference pp. 73–74 (2008)

Tura, A., Woo, J.: Performance comparison of silicon steep subthreshold FETs. IEEE Trans. Electron. Devices 57(6), 1362–1368 (2010)

Singh, J., Ramakrishnan, K., Mookerjea, S., Datta, S., Vijaykrishnan, N., Pradhan, D.: A novel Si-tunnel FET based SRAM design for ultra low-power 0.3V VDD applications. Design automation conference (ASP-DAC) pp. 181–186 (2010)

Mookerjea, S., Mohata, D., Mayer, T., Narayanan, V., Datta, S.: Temperature dependent I-V characteristics of a vertical In0.53Ga0.47As tunnel FET. IEEE Electron. Device Lett. 31(6), 564–566 (2010)

Born, M., Bhuwalka, K., Schindler, M., Ubelein, U., Schmidt, M., Sulima, T., Eisele, I.: Tunnel FET: a CMOS device for high temperature applications. Proceedings of the 25th international conference on microelectronics (MIEL 2006) pp. 14–17 (2006)

Schlosser, M., Bhuwalka, K.K., Sauter, M., Zilbauer, T., Sulima, T., Eisele, I.: Fringing-induced drain current improvement in the tunnel field-effect transistor with high-k gate dielectrics. IEEE Trans. Electron. Devices 56(1), 100–108 (2009)

Boucart, K., Ionescu, A.: Double-gate tunnel FET with high-k gate dielectric. IEEE Trans. Electron. Devices 54(7), 1725–1733 (2007)

Bardon, M., Neves, H., Puers, R., Hoof, C.: Pseudo-two-dimensional model for double-gate tunnel FETs considering the junctions depletion regions. IEEE Trans. Electron. Devices 57, 827–834 (2010)

Anghel, C., Gupta, A., Amara, A., Vladimirescu, A.: 30nm Tunnnel FET with improved performance and reduced ambipolar current. IEEE Trans. Electron. Devices 58(6), 1649–1654 (2011)

Yadav, M., Bulusu, A., Dasgupta, S.: Two dimensional analytical modeling for asymmetric 3t and 4t double gate tunnel fet in sub-threshold region: potential and electric field. Microelectron J 44(12), 1251–1259 (2013)

Sentaurus TCAD manual (2013)

Taur, Y.: An analytical solution to a double-gate MOSFET with undoped body. IEEE Electron. Device Lett. 21(5), 245–247 (2000)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Yadav, M., Bulusu, A. & Dasgupta, S. Super-threshold semi analytical channel potential model for DG tunnel FET. J Comput Electron 14, 566–573 (2015). https://doi.org/10.1007/s10825-015-0679-z

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-015-0679-z