Abstract

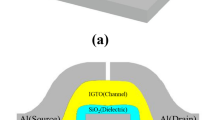

In this paper we numerically examine the electrical characteristics of surrounding-gate strained silicon nanowire field effect transistors (FETs) by changing the radius (RSiGe) of silicon-germanium (SiGe) wire. Due to the higher electron mobility, the n-type FETs with strained silicon channel films do enhance driving capability (∼8% increment on the drain current) in comparison with the pure Si one. The leakage current and transfer characteristics, the threshold-voltage (V t ), the drain induced barrier height lowering (DIBL), and the gate capacitance (C G ) are estimated with respect to different gate length (L G ), gate bias (V G ), and RSiGe. For short channel effects, such as V t roll-off and DIBL, the surrounding-gate strained silicon nanowire FET sustains similar characteristics with the pure Si one.

Similar content being viewed by others

References

B.H. Lee et al., “Performance enhancement on sub-70 nm strained silicon SOI MOSFETs on ultra-thin thermally mixed strained silicon/SiGe on insulator (TM-SGOI) substrate with raised S/D,” Tech. Dig. IEDM 946 (2002).

H.M. Nayfeh et al., “Influence of high channel doping on the inversion layer electron mobility in strained silicon n-MOSFETs,” IEEE Elec. Dev. Lett., 24, 248 (2003).

J. Welser et al., “NMOS and PMOS transistors fabricated in strained silicon/relaxed silicon-germanium structures,” Tech. Dig. IEDM 1000 (1992).

M. Rashed et al., “Simulation of electron transport in strained silicon on relaxed Si1−xGex substrates,” in Proc. Biennial University/Government/Industry Microelec. Symp. (1995) vol. 168.

J.R. Hwang et al., “Performance of 70 nm strained-silicon CMOS devices,” Dig. Tech. 2003 Symp. VLSI Tech., 103 (2003).

L. Huang et al., “Electron and hole mobility enhancement in strained SOI by wafer bonding,” IEEE Trans. Elec. Dev., 49, 1566 (2002).

C. Fenouillet-Beranger et al., “Requirements for ultra-thin-film devices and new materials for the CMOS roadmap,” Solid-State Elec., 48, 961 (2004).

M. Enciso Aguilar et al., “Strained Si HFETs for microwave applications: State-of-the-art and further approaches,” Solid-State Elec., 48, 1443 (2004).

F.-L. Yang et al., “Strained FIP-SOI (finFET/FD/PD-SOI) for sub-65 nm CMOS scaling,” in Dig. Tech. 2003 Symp. VLSI Tech. (2003) p. 137.

K. Rim et al., “Fabrication and analysis of deep submicron strained-Si n-MOSFET’s,” IEEE Trans. Elec. Dev., 47, 1406 (2000).

F.-L. Yang et al., “25 nm CMOS Omega FETs,” Tech. Dig. IEDM, 255 (2002).

H. Wakabayashi et al., “Sub-10-nm planar-bulk-CMOS devices using lateral junction control,” Tech. Dig. IEDM S20P7 (2003).

S.N. Balaban et al., “Quantum transport in a cylindrical sub-0.1 μm silicon-based MOSFET,” Solid-State Elec., 46, 435 (2002).

R. Venugopal et al., “Simulating quantum transport in nanoscale transistors: Real versus mode-space approaches,” J. App. Phys., 92, 3730 (2002).

J. Wang et al., “Does source-to-drain tunneling limit the ultimate scaling of MOSFETs?,” Tech. Dig. IEDM, 707 (2002).

A. Svizhenko et al., “Role of scattering in nanotransistors,” IEEE Trans. Elec. Dev., 50, 1459 (2003).

H. Kawaura et al., “Observation of source-to-drain direct tunneling current in 8 nm gate electrically variable shallow junction metal-oxide-semiconductor field-effect transistors,” Appl. Phys. Lett., 76, 3810 (2000).

A. Schenk et al., “2D Analysis of source-to-drain tunneling in decananometer MOSFETs with the density-gradient model,” in Tech. Proc. Int. Conf. Modeling and Simulation of Microsystems 552 (2002).

A. Asenov et al., “The use of quantum potentials for confinement in semiconductor devices,” in Tech. Proc. Int. Conf. Modeling and Simulation of Microsystems 490 (2002).

Y. Li et al., “A Practical implementation of parallel dynamic load balancing for adaptive computing in VLSI device simulation,” Engineering with Computers, 18, 124 (2002).

Y. Li et al., “A two-dimensional quantum transport simulation of nanoscale double-gate MOSFETs using parallel adaptive technique,” IEICE Trans. Information and Systems, E87-D, 1751 (2004).

T.-W. Tang et al., “Discretization scheme for the density-gradient equation and effect of boundary conditions,” J. Comput. Elec., 1, 389 (2002).

C.-S. Tang et al., “Simulation of electrical characteristics of surrounding- and omega-shaped-gate nanowire FinFETs,” Proc. IEEE Conf. Nanotech. 281 (2004).

K. Matsuda, “Phonon scattering effects on temperature dependence of conductivity in strained silicon,” J. Comput. Elec., 1, 425 (2002).

G. Kaiblinger-Grujin et al., “A universal low-field electron mobility model for semiconductor device simulation,” in Tech. Proc. Int. Conf. Modeling and Simulation of Microsystems 70 (1998).

A.R. Brown et al., “Intrinsic fluctuations in sub 10-nm double-gate MOSFETs introduced by discreteness of charge and matter,” IEEE Trans. Nanotech., 1, 195 (2002).

A. Asenov et al., “Quantum mechanical and transport aspects of resolving discrete charges in nano-CMOS device simulation,” in Proc. IEEE Conf. Nanotech. 334 (2004).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Li, Y., Lee, JW. & Chou, HM. Silicon-Germanium Structure in Surrounding-Gate Strained Silicon Nanowire Field Effect Transistors. J Comput Electron 3, 251–255 (2004). https://doi.org/10.1007/s10825-004-7056-7

Issue Date:

DOI: https://doi.org/10.1007/s10825-004-7056-7