Abstract

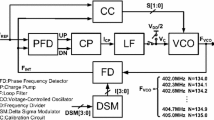

This paper presents a 3rd-order self-biased phase-locked loop (PLL) with adaptive fast-locking scheme for serialize/deserialize (SerDes) interfaces. In order to obtain short and almost equal power-up latency in a wide range of reference frequencies, a fast-locking circuit block including 2 switched-capacitor frequency-to-voltage (F–V) converters and an adaptive discharger is proposed to speed up the power-up process. Additionally, the current in the charge pump (CP) of the traditional self-biased PLL tends to be influenced by the kick-back noise from the voltage-controlled oscillator (VCO). In order to reduce the jitter resulted from the VCO kick-back noise, an additional bias generator is inserted between the original bias generator and the VCO to isolate the bias signals for the CP and the VCO. The simulated clock jitter under 100-mV, 1-MHz supply noise is 27 ps at an output frequency of 2 GHz, which is much lower than that of the traditional counterpart. The presented PLL is integrated in a SerDes interface chip fabricated in a 0.25-μm standard CMOS technology. Measurement results show that the presented PLL achieves a power-up latency of 4–6.5 μs in the output frequency range of 200 MHz–2 GHz, and the peak-to-peak data jitter of the SerDes chip is 110 ps at a data rate of 2.5 Gbps. The presented PLL consumes 217 mW under a 2.5-V power supply, and the block area is 350 × 600 μm2.

Similar content being viewed by others

References

Lee, S.-H., Tran, D., Ali, T., Catli, B., Zhang, H., Zhang, W., Abdul-Latif, M., Huang, Z., Li, G., Ahmadi, M. R., & Momtaz, A. (2014). A 23 mW/lane 1.2–6.8 Gb/s multi-standard transceiver in 28 nm CMOS. In IEEE Asian Solid-State Circuits Conference, A-SSCC 2014 (pp. 105–108).

Barnes, R. K., Wee, T. T., Oshima, M. M., Moore, C. E., Kennedy, R. R., & Gilsdorf, M. J. (2006). A versatile 90-nm CMOS charge-pump PLL for SerDes transmitter clocking. IEEE Journal of Solid-State Circuits, 41(8), 1894–1907.

Balan, V., Oluwole, O., Kodani, G., Zhong, C., Dadi, R., Amin, A., et al. (2014). A 15–22 Gbps serial link in 28 nm CMOS with direct DFE. IEEE Journal of Solid-State Circuits, 49(12), 3104–3115.

Chang, K.-Y. K., Wei, J., Huang, C., Li, Y., Donnelly, K., Horowitz, M., et al. (2003). A 0.4-4-Gb/s CMOS quad transceiver cell using on-chip regulated dual-loop PLLs. IEEE Journal of Solid-State Circuits, 38(5), 747–754.

Maneatis, J. G. (1996). Low-jitter process-independent DLL and PLL based on self-biased techniques. IEEE Journal of Solid-State Circuits, 31(11), 1723–1732.

Maneatis, J. G., Kim, J., McClatchie, I., Maxey, J., & Shankaradas, M. (2003). Self-biased high-bandwidth low-jitter 1-to-4096 multiplier clock generator PLL. IEEE Journal of Solid-State Circuits, 38(11), 1795–1803.

Maneatis, J. G., & Horowitz, M. A. (1993). Precise delay generation using coupled oscillators. IEEE Journal of Solid-State Circuits, 28(12), 1273–1282.

Fayneh, E., & Knoll, E. (2001). Third-order self-biased phase-locked loop for low jitter applications. U.S. Patent 6329882 B1.

Abbasi, S., Perrigo, M. E., & Price, C. (2003). Self-bias and differential structure based PLL with fast lockup circuit and current range calibration for process variation. U.S. Patent 6646512 B2.

Lim, C., H., & Wong, L. (2005). Method and apparatus for fast lock acquisition in self-biased phase locked loops. U.S. Patent 6919769 B2.

Gardner, Floyd M. (2005). Phaselock techniques. Hoboken, NJ: Wiley.

Acknowledgments

This work was supported by the No. 58 Institute of China Electronic Technology Group Corporation, and co-supported by the NSFC of China under contract of 61474092, and the Science and Technology Project of Shaanxi Province (2014K05-14).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Zhang, H., Du, X., Zhang, Y. et al. A low-jitter third-order self-biased PLL with adaptive fast-locking scheme for SerDes interfaces. Analog Integr Circ Sig Process 85, 311–321 (2015). https://doi.org/10.1007/s10470-015-0615-y

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-015-0615-y