Abstract

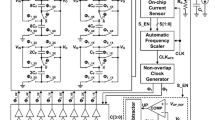

This paper presents a 2:1 low power switched-capacitor DC–DC converter designed in \(180\) nm Standard CMOS technology. The converter operates from \(1.8\) V input and delivers a \(0.8\) V power supply with \(50\) mA load current. Simplicity and power efficiency improvement is the main goal of this design. The achieved efficiency of the converter is more than \(80\,\%\). Also, high power efficiency, high current delivery, small size, low output voltage ripples are some main properties of the proposed DC–DC converters. The converter occupies about an area of \(1\) mm\(^2\). Besides, switching frequency of the switched-capacitor DC-DC converter has been increased to reduce output voltage ripples. Maximum output voltage ripple is about \(21\) mV. Power saving in gate driver stage is the method used in this design to improve the power efficiency. Also, a little changes applied in non-overlapping clock signal generator to gain a better power efficiency. During the design procedure, the main power loss sources have been explained and their solutions have been presented.

Similar content being viewed by others

References

Balogh, L. (2001). Design and application guide for high speed mosfet gate drive circuits. Texas Instruments/Unitrode Corporation, Power Supply Design Seminar, SEM.

Bochenek, M. (2012). Development of radiation resistant cmos integrated circuits for the power distribution system un the upgraded atlas semiconductor tracker. Ph.D. Thesis, AGH University of Science and Technology.

Castro, P., Silveira, F., Eirea, G. (2012). Modular architecture for ultra low power switched-capacitor dc–dc converters. In 2012 IEEE 55th International Midwest Symposium on Circuits and Systems (MWSCAS) (pp. 1036–1039).

Choi, Y., Jeon, H., Kim, Y.B. (2013). A switched-capacitor dc-dc converter using delta-sigma digital pulse frequency modulation control method. In 2013 IEEE 56th International Midwest Symposium on Circuits and Systems (MWSCAS) (pp. 356–359).

Forestiere, G. (2014). Ultra-low power circuits for power management. Master’s thesis, KTH Information and Communication Technology, Stockholm, Sweden.

Haq, F.U. (2011). Low power switched capacitor dc-dc converters for low power transceiver applications. Master’s thesis, Tampere University of Technology.

Jung, I.S., Kim, Y.B., Choi, M. (2011). The novel switched-capacitor dc-dc converter for fast response time and reduced ripple. In 2011 IEEE 54th International Midwest Symposium on Circuits and Systems (MWSCAS) (pp. 1–4).

Ma, M. (2003). Design of high efficiency step-down switched capacitor dc/dc converter. Master’s thesis, Oregon State University.

Ngo, K., Webster, R. (1992). Steady-state analysis and design of a switched-capacitor dc–dc converter. In 23rd Annual IEEE Power Electronics Specialists Conference, 1992. PESC’92 Record (pp. 378–385).

Qian, J., & Zhao, L. (2006). Circuit design and power loss analysis of a synchronous switching charger with integerated mosfets for li-ion batteries. Technical Report, Texas Instruments.

Sclocchi, M. Switching power supply design: Discontinuous mode flyback converter. Technical Report, National Semiconductor.

Su, L., Ma, D., & Brokaw, A. P. (2010). Design and analysis of monolithic step-down sc power converter with subthreshold dpwm control for self-powered wireless sensors. IEEE Transactions on Circuits and Systems I: Regular Papers, 57(1), 280–290.

Wang, L. (2013). Design of integrated voltage-mode controlled dc–dc buck converter.

Xu, M., Sun, J., Lee, F.C. (2006). Voltage divider and its application in the two-stage power architecture. In Twenty-First Annual IEEE Applied Power Electronics Conference and Exposition, 2006. APEC’06. (p. 7).

Acknowledgments

The authors would like to thank Mr. Saeed Ghiasi, Mrs. Jafarnejad and Mrs. Sheikholeslami for their helpful supports and feedbacks.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Rikhtegar Ghiasi, R., Sahafi, A., Sobhi Geshlaghi, J. et al. A 2:1 switched-capacitor DC–DC converter for low power circuits. Analog Integr Circ Sig Process 84, 215–222 (2015). https://doi.org/10.1007/s10470-015-0551-x

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-015-0551-x