Abstract

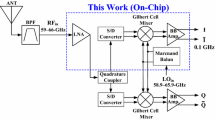

This paper presents a wireless receiver front-end intended for cellular applications implemented in a 65 nm CMOS technology. The circuit features a low noise amplifier (LNA), quadrature passive mixers, and a frequency divider generating 25 % duty cycle quadrature local oscillator (LO) signals. A complementary common-gate LNA is used, and to meet the stringent linearity requirements it employs positive feedback with transistors biased in the sub-threshold region, resulting in cancellation of the third order non-linearity. The mixers are also linearized, using a baseband to LO bootstrap circuit. Measurements of the front-end show about 3.5 dB improvement in out-of-band IIP3 at optimum bias of the positive feedback devices in the LNA, resulting in an out-of-band IIP3 of 10 dBm. With a frequency range from 0.7 to 3 GHz the receiver front-end covers most important cellular bands, with an input return loss above 9 dB and a voltage gain exceeding 16 dB for all bias settings. The circuit consumes 4.38 mA from a 1.5 V supply.

Similar content being viewed by others

References

Allstot, D. J., Xiaoyong, L., & Shekhar, S. (2004). Design considerations for CMOS low-noise-amplifiers. Radio Frequency Integrated Circuits (RFIC) symposium, 2004. Digest of Papers, 2004 IEEE, pp. 97–100.

Borremans, J., Mandal, G., Debaillie, B., Giannini, V., & Craninckx, J. (2010). A sub-3 dB NF voltage-sampling front-end with +18 dBm IIP3 and +; 2 dBm blocker compression point. Proceedings of the ESSCIRC, 2010, pp. 402–405.

Brederlow, R., Weber, W., Sauerer, J., Donnay, S., Wambacq, P., & Vertregt, M. (2001). A mixed-signal design roadmap. IEEE Design & Test of Computers, 18(6), 34–46.

Fei, L. (2005). Broadband technology frequency divider design strategies, RF Design, 28, 18–29 (2005).

Fatin, G. Z., Koozehkanani, Z. D., & Sjöland, H. (2010). A technique for improving gain and noise figure of common-gate wideband LNAs. Analog Integrated Circuits and Signal Processing, 65, 239–244

Yuan, J., Karlsson, I., & Svensson, C. (1987). A true single-phase-clock dynamic CMOS circuit technique. IEEE Journal of Solid-State Circuits, 22, 899–901.

Xiaoyong, L., Shekhar, S., & Allstot, D. J. (2005). Gm-boosted common-gate LNA and differential colpitts VCO/QVCO in 0.18-μm CMOS. IEEE Journal of Solid-State Circuits, 40, 2609–2619

Liscidini, A., Martini, G., Mastantuono, D., & Castello, R. (2008). Analysis and design of configurable LNAs in feedback common-gate topologies. IEEE Transactions on Circuits and Systems II: Express Briefs, 55, 733–737

Mirzaei, A., Chen, X., Yazdi, A., Chiu, J., Leete, J., & Darabi, H. (2009). A frequency translation technique for SAW-less 3G receivers. Symposium on VLSI Circuits, 2009, pp. 280–281.

Mirzaei, A., Darabi, H., Leete, J. C., & Yuyu, C. (2010). Analysis and optimization of direct-conversion receivers with 25% duty-cycle current-driven passive mixers. IEEE Transactions on Circuits and Systems I: Regular Papers, 57, 2353–2366.

Nejdel, A., Törmänen, M., & Sjöland, H. (2011). A linearized 1.6–5 GHz low noise amplifier using positive feedback in 65 nm CMOS. NORCHIP 2011, pp. 1–4

Tillman, F., & Sjoland, H. (2003). A bootstrapping technique to improve the linearity of CMOS passive mixers. Symposium on VLSI Circuits, Digest of Technical Papers, 2003, pp. 221–222.

Voltti, M., Koivi, T., & Tiiliharju, E. (2007). Comparison of active and passive mixers, circuit theory and design, 2007. 18th European Conference on ECCTD 2007, pp. 890–893.

Woo, S., Kim, W., Lee, C.-H., Lim, K., & Laskar, J. (2009). A 3.6 mW differential common-gate CMOS LNA with positive-negative feedback. IEEE International Solid-State Circuits Conference—Digest of Technical Papers, 2009. ISSCC 2009, pp. 218–219, 219a

Yue, C. P., & Wong, S. S. (1997). On-chip spiral inductors with patterned ground shields for Si-based RF IC’s. Symposium on VLSI Circuits, Digest of Technical Papers, 1997, pp. 85–86.

Heng, Z., & Sänchez-Sinencio, E. (2011). Linearization techniques for CMOS low noise amplifiers: A tutorial. IEEE Transactions on Circuits and Systems I: Regular Papers, 58, 22–36.

Zhuo, W., Li, X., Shekhar, S., Embabi, S. H. K., de Gyvez, J. P., & Allstot, D. J. (2005). A capacitor cross-coupled common-gate low-noise amplifier. Circuits and Systems II: Express Briefs, 52, 875–879.

Acknowledgments

The authors would like to thank the Swedish Foundation for Strategic Research for funding the Digitally Assisted Radio Evolution project, and the other researchers in the Analog RF group at Lund University for fruitful discussions.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Nejdel, A., Törmänen, M. & Sjöland, H. A 0.7 to 3 GHz wireless receiver front end in 65-nm CMOS with an LNA linearized by positive feedback. Analog Integr Circ Sig Process 74, 49–57 (2013). https://doi.org/10.1007/s10470-012-9962-0

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-012-9962-0