Abstract

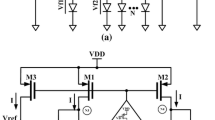

A low power voltage reference generator operating with a supply voltage ranging from 1.6 to 3.6 V has been implemented in a 90-nm standard CMOS technology. The reference is based on MOSFETs that are biased in the weak inversion region to consume nanowatts of power and uses no resistors. The maximum supply current at 3.6 V and at 125°C is 173 nA. It provides a 771 mV voltage reference. A temperature coefficient of 7.5 ppm/°C is achieved at best and 39.5 ppm/°C on average, in a range from −40 to 125°C, as the combined effect of a suppression of the temperature dependence of mobility and the compensation of the threshold voltage temperature variation. Several process parameters affect the performance of the proposed voltage reference circuit, so a process adjustment aimed at correcting errors in the reference voltage caused by these variations is dealt with. The total block area is 0.03 mm2.

Similar content being viewed by others

References

Bravaix, A., Goguenheim, D., Revil, N., Vincent, E., Varrot, M., & Mortini, P. (1999). Analysis of high temperature effects on performances and hot-carrier degradation in DC/AC stressed 0.35 μm n-MOSFET’s. Microelectronics Reliability, 39(1), 35–44.

Leung, K. N., & Mok, P. K. T. (2002). A sub-1-V 15 ppm/°C CMOS bandgap voltage reference without requiring low threshold voltage device. IEEE Journal of Solid-State Circuits, 37, 526–530.

Tanaka, H., Nakagome, Y., Etoh, J., Yamasaki, E., Aoki, M., & Miyazawa, K. (1994). Sub-1V dynamic reference voltage generator for battery-operated DRAMs. IEEE Journal of Solid-State Circuits, 29(4), 448–453.

Vittoz, A., & Neyroud, O. (1979). A low-voltage CMOS bandgap reference. IEEE Journal of Solid-State Circuits, 14(3), 573–577.

Giustolisi, G. et al. (2003). A low-voltage low-power voltage reference based on subthreshold MOSFETs. IEEE Journal of Solid-State Circuits, 38, 151–154.

Vittoz, E., & Fellrath, J. (1977). CMOS analog circuits based on weak inversion operation. IEEE Journal of Solid-State Circuits, SC-12, 224–231.

De Vita, G., & Iannaccone, G. (2005). An ultra-low-power, temperature compensated voltage reference generator. In Proceedings of CICC (pp. 751–754).

Leung, K. N., & Mok, P. K. T. (2003). A CMOS voltage reference based on weighted Vgs for CMOS low-dropout linear regulators. IEEE Journal of Solid-State Circuits, 38(1), 146–150.

Banba, H. et al. (1999). A CMOS bandgap reference circuit with sub-1V operation. IEEE Journal of Solid-State Circuits, 34, 670–674.

Tsividis, Y. (1999). Operation and modeling of the MOS transistor (2nd ed., p. 190). New York, USA: MacGraw Hill.

Taur, Y., & Ning, T. H. (1998). Fundamentals of modern VLSI devices (p. 131). Cambridge: Cambridge University Press.

Oguey, H., & Aebischer, D. (1997). CMOS current reference without resistance. IEEE Journal of Solid-State Circuits, 32(7), 1132–1135.

Camacho-Galeano, E. M., Galup-Montoro, C., & Schneider, M. C. (2005). A 2-nW 1.1-V self-biased current reference in CMOS technology. IEEE Transactions on Circuits and Systems II, 52(2), 333–336.

Swanson, R. M., & Meindl, J. D. (1972). Ion-implanted complementary MOS transistor in low-voltage circuits. IEEE Journal of Solid-State Circuits, SC-7, 146–153.

Nissinen, I., & Sawan, M. (2003). A 900 mV 25 μW High PSRR CMOS voltage reference dedicated to implantable micro-devices. IEEE International Symposium on Circuits and Systems, 1, 373–376.

Hu, Y., & Kostamovaara, J. (2004). A low voltage CMOS constant current voltage reference circuit. IEEE International Symposium on Circuits and Systems, 1, 381–384.

De Vita, G., Iannaccone, G., & Andreani, P. (2006). A 300 nW, 12 ppm/°C voltage reference in a digital 0.35 μmCMOS process. In Symposium on VLSI circuits, digest of technical papers (pp. 81–82). Honolulu, HI.

Arora, N. (1993). MOSFET models for VLSI circuit simulation (p. 221). New York: Springer.

Mizuno, K., Ohta, N., Kitagawa, F., & Nagase, H. (1998). Analog CMOS integrated circuits for high-temperature operation with leakage current compensation. High temperature electronics conferences, HITEC, p. 41.

Razavi, B. (2001). Design of analog CMOS integrated circuits (pp. 463–465). New York: McGraw Hill.

Ueno, K., Hirose, T., Asai, T., & Amemiya, Y. (2009). A 300 nW, 15 ppm/°C, 20 ppm/V CMOS voltage reference circuit consisting of subthreshold MOSFETs. IEEE Journal of Solid-State Circuits, 44(7), 2047–2054.

De Vita, G., & Iannaccone, G. (2007). A Sub-1-V, 10 ppm/°C, nanopower voltage reference generator. IEEE Journal of Solid-State Circuits, 42(7), 1536–1542.

Ma, H., & Zhou, F. (2009). A sub-1 V 115 nA 0.35 μm CMOS voltage reference for ultra low-power applications. In Proceedings of IEEE of the ASIC, ASICON ‘09. IEEE 8th International Conference on ASIC (pp. 1074–1077).

Acknowledgments

The author would like to thank STMicroelectronics Rousset, E. Kussener, H. Barthelemy, W. Rahajandraibe, L. Girardeau and Y. Bert for their help, fruitful discussions, and encouragement.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Samir, A., Kussener, E., Rahajandraibe, W. et al. A sub-1-V, high precision, ultra low-power, process trimmable, resistorless voltage reference with low cost 90-nm standard CMOS technology. Analog Integr Circ Sig Process 73, 693–706 (2012). https://doi.org/10.1007/s10470-012-9852-5

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-012-9852-5