Abstract

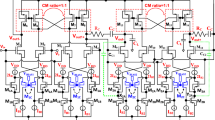

This paper presents a modified design method for linear transconductor circuit in 130 nm CMOS technology to improve linearity, robustness against process induced threshold voltage variability and reduce harmonic distortion. Source follower in the adaptively biased differential pair (ABDP) linear transconductor circuit is replaced with flipped voltage follower to improve the efficiency of the tail current source, which is connected to a conventional differential pair. The simulation results show the performance of the modified circuit also has better speed, noise performance and common mode rejection ratio compared to the ABDP circuit.

Similar content being viewed by others

References

Sengupta, S. (2005). Adaptively biased linear transconductor. IEEE Transaction on Circuits and Systems (1 regular papers), 52(11), 2369–2375.

Sanchez-Sinencio, E., & Silva, J. (2000). CMOS transconductance amplifiers, architectures and active filters: A tutorial, Proc. Proceedings of the IEE Circuits Devices and Systems, 147(1), 3–12.

Krummenacher, F., & Joehl, N. (1998). A 4-MHz CMOS continuous-time filter with on-chip automatic tuning. IEEE Journal of Solid-State Circuits, 23(3), 750–758.

Czarnul, Z., & Tagaki, S. (1990). Design of linear tunable CMOS differential transconductor cells. Electronics Letters, 26(21), 1809–1810.

Ismail, A. M., & Soliman, A. M. (2000). Novel CMOS wide-linear-range transconductor amplifier. IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications, 47(8), 1248–1253.

Nedungadi, A., & Viswanathan, T. (1984). Design of linear CMOS transconductance elements. IEEE Transactions on Circuits and Systems, CAS-31(10), 891–894.

Kuo, K. C., & Leuciuc, A. (2001). A linear MOS transconductor using source degeneration and adaptive biasing. IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, 48(10), 937–943.

Wang, Z., & Guggenbuhl, W. (1990). A voltage-controllable linear MOS transconductor using bias offset technique. IEEE Journal of Solid-State Circuits, 25(1), 315–317.

Seevinck, E., & Wassenaar, R. F. (1987). A versatile CMOS linear transconductor/square-law function circuit. IEEE Journal of Solid-State Circuits, SC-22(3), 366–377.

Ramírez-Angulo, J., Carvajal, R. G., Torralba, A., Galan, J., Vega-Leal, A. P., & Tombs, J. (2005). The flipped voltage follower: A useful cell for low voltage low-power circuit design. IEEE Transaction on Circuits and systems (1 regular papers), 52(7), 1276–1290.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Ajayan, K.R., Bhat, N. Linear transconductor with flipped voltage follower in 130 nm CMOS. Analog Integr Circ Sig Process 63, 321–327 (2010). https://doi.org/10.1007/s10470-009-9396-5

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-009-9396-5