Abstract

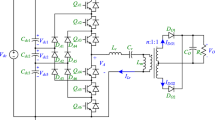

A significant improvement of the light load conversion efficiency in integrated CMOS DC–DC converters using pulse-width modulation (PWM) at constant switching frequencies above 1 MHz can be obtained by implementing dynamic width controlling (DWC) of the power transistors. The parallel implementation of DWC uses equally sized power cells, each containing the power transistor and its gate driver stages. The power cells are connected together in a parallel arrangement to limit the propagation delays and to avoid the transmission gates used in serial implementations. Due to this, higher switching frequencies can be realized. Advanced simulations were performed with Cadence Spectre combined with Mathematica to investigate the conversion efficiency improvement potential offered by DWC. With DWC, an absolute increase of the light load conversion efficiency as high as 29% can be achieved for switching frequencies in the range 1–10 MHz. Further, a conversion efficiency higher than 80% can be provided over roughly two decades of load current for a DC–DC converter operating at a switching frequency of 10 MHz. Experimental results obtained from a synchronous buck converter designed in a 0.18 μm CMOS technology and switched at 2 MHz in continuous conduction mode (CCM) have demonstrated an improvement of the light-load conversion efficiency of about 25%.

Similar content being viewed by others

References

Hazucha, P., Schrom, G., Hahn, J., Bloechel, B., Hack, P., Dermer, G., et al. (2005). A 233 MHz 80–87% efficient four-phase DC–DC converter utilizing air-core inductors on package. IEEE Journal of Solid-State Circuits, 40(4), 838–845.

Guckenberger, D., & Kornegay, K. (2003). Integrated DC–DC converter design for improved WCDMA power amplifier efficiency in SiGe BiCMOS technology, in International Symposium on Low Power Electronics and Design, ISLPED 2003, pp. 449–454, August 25–27, 2003.

Williams, R.K., Grabowski, W., Cowell, A., Darwish, M., & Berwick, J. (1997). The dual-gate W-switched power MOSFET: A new concept for improving light load efficiency in DC/DC converters, in IEEE International Symposium on Power Semiconductor Devices and IC’s, ISPSD 1997, pp. 193–196, May 26–29, 1997.

Huang, H.-W., Ho, H.-H., Chien, C.-C., Chen, K.-H., Ma, G.-K., & Kuo, S.-Y. (2006). Fast transient DC–DC converter with on-chip compensated error amplifier, in 32nd European Solid-State Circuits Conference, ESSCIRC 2006, pp. 324–327, September 2006.

Trescases, O., Ng, W. T., Nishio, H., Edo, M., & Kawashima, T. (2006). A digitally controlled DC–DC converter module with a segmented output stage for optimized efficiency, in IEEE International Symposium on Power Semiconductor Devices and IC’s, ISPSD 2006, pp. 1–4, June 4–8, 2006.

Lee, H.-C., Chang, K.-T., Chen, K.-H., & Chen, W. T. (2005). Power saving of a dynamic width controller for a monolithic current-mode CMOS DC–DC converter, in 5th International Workshop on System-on-Chip for Real-Time Applications, pp. 352–357, July 20–24, 2005.

Musunuri, S., & Chapman, P. L. (2005). Improvement of light-load efficiency using width-switching scheme for CMOS transistors. IEEE Power Electronics Letters, 3(3), 105–110.

Chen, K.-H., Chien, C.-C., Hsu, C.-H., & Huang, L.-R. (2007). Optimum power-saving method for power MOSFET width of DC/DC converters. IET Circuits, Devices & Systems, 1(1), 57–62.

Acknowledgments

The authors thank E. Deumens and P. Malisse from IMEC, A. Ostmann, E. Jung and M. Schneider-Ramelow from Fraunhofer IZM.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Lorentz, V.R.H., Berberich, S.E., März, M. et al. Light-load efficiency increase in high-frequency integrated DC–DC converters by parallel dynamic width controlling. Analog Integr Circ Sig Process 62, 1–8 (2010). https://doi.org/10.1007/s10470-009-9323-9

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-009-9323-9