Abstract

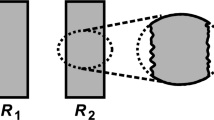

This paper describes the design and implementation of a low-power current-mode logarithmic analog-to-digital converter (ADC) for an ISFET-based \(p\!H\) digital readout system. The system comprises a front-end ISFET-based \(p\!H\) readout circuit and a succeeding logarithmic ADC to produce a digital output signal which is linearly related to the input \(p\!H\) variation. The front-end \(p\!H\) readout circuit is realized using a subthreshold ISFET/REFET differential pair with a current-mode translinear multiplier/divider circuit. The logarithmic ADC is realized using the cyclic architecture and current-mode circuit techniques to achieve low power dissipation. High-accuracy current sample-and-hold circuit based on the regulated-cascode switched-current memory cell and low-power high-resolution current comparator are proposed for the ADC realization. All circuits were designed to operate with a single 1-V power supply voltage, and were simulated with process parameters from a 0.18-\(\mu \)m CMOS technology. The power dissipation of the front-end \(p\!H\) readout circuit and the logarithmic ADC is 20 and 330 nW, respectively. The front-end \(p\!H\) readout circuit can produce an output current range of 0.1–300 nA which is logarithmically corresponded to the input \(p\!H\) range of 4–10. The logarithmic ADC operates with 1-kS/s sampling rate and achieves the integral nonlinearity error of \(\pm 0.8\) LSB, the effective number of bits of 5.95, and 37.6-dB of signal-to-noise-distortion ratio with 100-nA full-scale input range.

Similar content being viewed by others

References

N. Bako, A. Baric, A low-power fully differential 9-bit C-2C cyclic ADC, in 20th European Conference on Circuit Theory and Design. IEEE 20th European Conference on Circuit Theory and Design, pp. 576–579 (2011)

J. Bausells, J. Carrabina, A. Errachid, A. Merlos, Ion-sensitive field-effect transistors fabricated in a commercial CMOS technology. Sens. Actuators B 57(1–3), 56–62 (1999)

S. Cantarano, G.V. Pallottino, Logarithmic analog-to-digital converters: a survey. IEEE Trans. Instrum. Meas. 22(3), 201–213 (1973)

P. Crippa, C. Turchetti, M. Conti, A statistical methodology for the design of high-performance CMOS current-steering digital-to-analog converters. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 21(4), 377–394 (2002)

R. Dominguez-Castro, A. Rodriguez-Vazquez, F. Medeiro, J. Huertas, High resolution CMOS current comparators. in Eighteenth European Solid-State Circuits Conference, 1992. ESSCIRC ’92. pp. 242–245 (1992)

M. El Sharkawy, P. Georgiou, C. Toumazou, A silicon pancreatic islet for the treatment of diabetes, in Proceedings of 2010 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 3136–3139 (2010)

A. Errachid, J. Bausells, N. Jaffrezic-Renault, A simple REFET for pH detection in differential mode. Sens. Actuators B 60(1), 43–48 (1999)

P. Georgiou, C. Toumazou, A silicon pancreatic beta cell for diabetes. IEEE Trans. Biomed. Circuits Syst. 1(1), 39–49 (2007)

P. Georgiou, C. Toumazou, ISFET characteristics in CMOS and their application to weak inversion operation. Sens. Actuators B 143(1), 211–217 (2009)

J. Guilherme, J. Franca, New CMOS logarithmic A/D converters employing pipeline and algorithmic architectures, in 1995 IEEE International Symposium on Circuits and Systems, 1995. ISCAS ’95, vol. 1, pp. 529–532 (1995)

J. Guilherme, J. Vital, J. Franca, New logarithmic two-step flash A/D converter with digital error correction for MOS technology, in Proceedings of the 38th Midwest Symposium on Circuits and Systems, vol. 2, pp. 881–884 (1995)

J. Guilherme, J. Vital, J. Franca, A CMOS logarithmic pipeline A/D converter with a dynamic range of 80 dB, in 9th International Conference on Electronics, Circuits and Systems, vol. 1, pp. 193–196 (2002)

P. Hammond, D. Ali, D. Cumming, Design of a single-chip pH sensor using a conventional 0.6-\(\mu \)m CMOS process. IEEE Sens. J. 4(6), 706–712 (2004)

Y.C. Huang, T.C. Lee, A 0.02-mm\(^2\) 9-bit 50-MS/s cyclic ADC in 90-nm digital CMOS technology. IEEE J. Solid State Circuits 45(3), 610–619 (2010)

C.G. Jakobson, M. Feinsod, Y. Nemirovsky, Low frequency noise and drift in ion sensitive field effect transistors. Sens. Actuators B 68(1–3), 134–139 (2000)

M. Judy, A. Sodagar, R. Lotfi, A nonlinear signal-specific ADC for efficient neural recording, in 2010 IEEE Biomedical Circuits and Systems Conference (BioCAS), pp. 17–20 (2010)

C.H. Lee, H.I. Seo, Y.C. Lee, B.W. Cho, H. Jeong, B.K. Sohn, All solid type ISFET glucose sensor with fast response and high sensitivity characteristics. Sens. Actuators B 64(1–3), 37–41 (2000)

J. Lee, J. Kang, S. Park, J. Seo, J. Anders, J. Guilherme, M. Flynn, A 2.5 mW 80 dB DR 36 dB SNDR 22 MS/s logarithmic pipeline ADC. IEEE J. Solid State Circuits 44(10), 2755–2765 (2009)

J. Lee, H.G. Rhew, D. Kipke, M. Flynn, A 64 channel programmable closed-loop neurostimulator with 8 channel neural amplifier and logarithmic ADC. IEEE J Solid State Circuits 45(9), 1935–1945 (2010)

J. Mahattanakul, Logarithmic data converter suitable for hearing aid applications. Electron. Lett. 41(7), 394–396 (2005)

S. Martinoia, G. Massobrio, A behavioral macromodel of the ISFET in SPICE. Sens. Actuators B 62(3), 182–189 (2000)

K.Y. Park, S.B. Choi, M. Lee, B.K. Sohn, S.Y. Choi, ISFET glucose sensor system with fast recovery characteristics by employing electrolysis. Sens. Actuators B 83(1–3), 90–97 (2002)

M. Pelgrom, A.C.J. Duinmaijer, A. Welbers, Matching properties of MOS transistors. IEEE J. Solid State Circuits 24(5), 1433–1439 (1989)

A. Rodriguez-Vazquez, R. Dominguez-Castro, F. Medeiro, M. Delgado-Restituto, High resolution CMOS current comparators: design and applications to current-mode function generation. Analog Integr. Circuits Signal Process. 7(2), 149–165 (1995)

J.M. Rothberg, W. Hinz, T.M. Rearick, J. Schultz, W. Mileski, M. Davey, J.H. Leamon, K. Johnson, M.J. Milgrew, M. Edwards, J. Hoon, J.F. Simons, D. Marran, J.W. Myers, J.F. Davidson, A. Branting, J.R. Nobile, B.P. Puc, D. Light, T.A. Clark, M. Huber, J.T. Branciforte, I.B. Stoner, S.E. Cawley, M. Lyons, Y. Fu, N. Homer, M. Sedova, X. Miao, B. Reed, J. Sabina, E. Feierstein, M. Schorn, M. Alanjary, E. Dimalanta, D. Dressman, R. Kasinskas, T. Sokolsky, J.A. Fidanza, E. Namsaraev, K.J. McKernan, A. Williams, G.T. Roth, J. Bustillo, An integrated semiconductor device enabling non-optical genome sequencing. Nature 475(7356), 348–352 (2011)

T. Serrano-Gotarredona, B. Linares-Barranco, A. Andreou, A general translinear principle for subthreshold MOS transistors. IEEE Trans. Circuits Syst. I 46(5), 607–616 (1999)

L. Shepherd, C. Toumazou, Weak inversion ISFETs for ultra-low power biochemical sensing and real-time analysis. Sens. Actuators B 107(1), 468–473 (2005)

S. Sirimasakul, A. Thanachayanont, W. Jeamsaksiri, Low-power current-mode logarithmic pipeline analog-to-digital converter for ISFET based pH sensor, in 9th International Symposium on Communications and Information Technology. ISCIT 2009, pp. 1340–1343 (2009)

J.J. Sit, R. Sarpeshkar, A micropower logarithmic A/D with offset and temperature compensation. IEEE J. Solid State Circuits 39(2), 308–319 (2004)

R.L. Smith, D.C. Scott, An integrated sensor for electrochemical measurements. IEEE Trans. Biomed. Eng. 33(2), 83–90 (1986)

B.K. Sohn, B.W. Cho, C.S. Kim, D.H. Kwon, ISFET glucose and sucrose sensors by using platinum electrode and photo-crosslinkable polymers. Sens. Actuators B 41(1–3), 7–11 (1997)

A. Thanachayanont, S. Sirimasakul, Ultra-low-power differential ISFET/REFET readout circuit. ETRI J. 31(2), 243–245 (2009)

C. Toumazou, P. Georgiou, Piet bergveld - 40 years of ISFET technology: from neuronal sensing to DNA sequencing. Electron. Lett. 47(26), S7–S12 (2011)

C. Toumazou, J. Hughes, D. Pattullo, Regulated cascode switched-current memory cell. Electron. Lett. 26(5), 303–305 (1990)

C. Toumazou, L.M. Shepherd, S.C. Reed, G.I. Chen, A. Patel, D.M. Garner, C.J.A. Wang, C.P. Ou, K. Amin-Desai, P. Athanasiou, H. Bai, I.M.Q. Brizido, B. Caldwell, D. Coomber-Alford, P. Georgiou, K.S. Jordan, J.C. Joyce, M. La Mura, D. Morley, S. Sathyavruthan, S. Temelso, R.E. Thomas, L. Zhang, Simultaneous DNA amplification and detection using a pH-sensing semiconductor system. Nat. Methods 10(7), 641–646 (2013)

C. Toumazou, T.S.L.K. Thay, P. Georgiou, A new era of semiconductor genetics using ion-sensitive field-effect transistors: the gene-sensitive integrated cell. Philos. Trans. Ser. A Math. Phys. Eng. Sci. 372(2012), 20130,112 (2014)

H. Traff, Novel approach to high speed CMOS current comparators. Electron. Lett. 28(3), 310–312 (1992)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Thanachayanont, A. A 1-V, 330-nW, 6-Bit Current-Mode Logarithmic Cyclic ADC for ISFET-Based \(p\!H\) Digital Readout System. Circuits Syst Signal Process 34, 1405–1429 (2015). https://doi.org/10.1007/s00034-014-9908-0

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-014-9908-0