Abstract

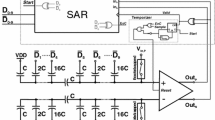

This paper presents a 10 bit charge redistribution successive approximation analog-to-digital converter (ADC) for integrated digitally controlled DC–DC converters. A timing efficient implementation of a window function is proposed, where only a reduced input range is converted. A redundant search is applied to overcome the speed limitation of the analog components. The window mode enables further speed enhancement without an increase of clock frequency and power consumption. Position of the set-point and size of the window is digitally adjustable every conversion. Fabricated in 28 nm low-power CMOS technology the ADC occupies only 110 × 85 µm2. In full range mode a conversion rate of 16 MS/s is achieved and in window mode 26.7 MS/s, respectively. With a measured total power consumption of 710 µW and 9.1 bit ENOB a FOM of 81 fJ/conv-step is reached. A large input range with constant resolution, highly linear characteristic, and high robustness to PVT variations together make this ADC an advantageous alternative to delay line or ring oscillator based window ADCs. The highly digital nature of the proposed architecture allows implementation in modern sub-100 nm CMOS technologies.

Similar content being viewed by others

References

Li, H.-Q., Wang, S.-L., Gao, Y., Song, Y. & Geng, L. (2012). A flash window ADC for DVS-enabled digital controlled DC–DC converters. In: Proceedings of the IEEE 11th international conference on solid-state and integrated circuit technology (ICSICT), Oct 2012 (pp. 1–3). IEEE

Jonsson, B. (2010). A survey of A/D-converter performance evolution. In: Proceedings of the 17th IEEE international conference on electronics, circuits, and systems (ICECS), 2010 (pp. 766–769). IEEE

Daniels, J., Dehaene, W., Steyaert, M., & Wiesbauer, A. (2010). A 0.02 mm2 65 nm CMOS 30 MHz BW all-digital differential VCO-based ADC with 64 B SNDR. In: Proceedings of the IEEE symposium on VLSI circuits (VLSIC), June 2010 (pp. 155–156). IEEE

Shen, S. Xie, S., & Ng, W. T. (2012). A power and area efficient 65 nm CMOS delay line ADC for on-chip voltage sensing. In: Proceedings of the IEEE international conference on electron devices and solid state circuit (EDSSC), Dec 2012 (pp. 1–4). IEEE

Haenzsche, S., Höppner, S., Ellguth, G., & Schüffny, R. (2014). A 12 bit 4 MS/s SAR ADC with configurable redundancy in 28 nm CMOS technology. IEEE Transactions on Circuits and Systems II: Express Briefs, 61(11), 835–839.

Yoshioka, K., Shikata, A., Sekimoto, R., Kuroda, T., & Ishikuro, H. (2013). A 0.0058 mm2 7.0 ENOB 24 MS/s 17fJ/conv. threshold configuring SAR ADC with source voltage shifting and interpolation technique. In: Proceedings of the symposium on VLSI circuits (VLSIC), June 2013 (pp. C266–C267).

Harpe, P., Zhang, Y., Dolmans, G., Philips, K., & de Groot, H. (2012). A 7-to-10b 0-to-4 MS/s flexible SAR ADC with 6.5-to-16fJ/conversion-step. In: Proceedings of the IEEE international solid-state circuits conference digest of technical papers (ISSCC), Feb 2012 (pp. 472–474). IEEE

Foong, H., Tan, M., & Zheng, Y. (2012). A 0.8-µW window SAR ADC with offset cancellation for digital DC–DC converters. Analog Integrated Circuits and Signal Processing, 70(1), 133–139.

Haenzsche, S., Höppner, S., & Schüffny, R. (2014). A 10 bit 16 MS/s redundant SAR ADC with flexible window function for a digitally controlled DC–DC converter in 28 nm CMOS. In: NORCHIP, Oct 2014 (pp. 1–4).

Sekimoto, R., Shikata, A., Kuroda, T., & Ishikuro, H. (2011). A 40 nm 50S/s-8MS/s ultra low voltage SAR ADC with timing optimized asynchronous clock generator. In: Proceedings of the ESSCIRC (ESSCIRC), Sept. 2011 (pp. 471–474).

Yuan, C., & Lam, Y. (2013). A 281-nW 43.3 fJ/conversion-step 8-ENOB 25-kS/s asynchronous SAR ADC in 65 nm CMOS for biomedical applications. In: Proceedings of the IEEE international symposium on circuits and systems (ISCAS), May 2013, (pp. 622–625). IEEE

Arian, A., Saberi, M., Hosseini-Khayat, S., Lotfi, R., & Leblebici, Y. (2012). A 10-bit 50-MS/s redundant SAR ADC with split capacitive-array DAC. Analog Integrated Circuits and Signal Processing, 71(3), 583–589.

Kuttner, F. (2002). A 1.2 V 10 b 20 MSample/s non-binary successive approximation ADC in 0.13 µm CMOS. In: Proceedings of the IEEE international solid-state circuits conference, digest of technical papers, ISSCC, 2002 (vol. 1, pp. 176–177). IEEE

Hesener, M., Eichler, T., Hanneberg, A., Herbison, D., Kuttner, F., & Wenske, H. (2007). A 14 b 40 MS/s redundant SAR ADC with 480 MHz clock in 0.13 µm CMOS. In: Proceedings of the IEEE international solid-state circuits conference, ISSCC, digest of technical papers, Feb. 2007 (pp. 248–600). IEEE

Anderson, T. O. (1972). Optimum control logic for successive approximation analog-to-digital converters. Computer Design, 11(7), 81–86.

Cliquennois, S., Donida, A., Malcovati, P., Baschirotto, A., & Nagari, A. (2012). A 65-nm, 1-A buck converter with multi-function SAR-ADC-based CCM/PSK digital control loop. IEEE Journal of Solid-State Circuits, 47(7), 1546–1556.

Malki, B., Yamamoto, T., Verbruggen, B., Wambacq, P., & Craninckx, J. (2012). A 70 dB DR 10 b 0-to-80 MS/s current-integrating SAR ADC with adaptive dynamic range. In: Proceedings of the IEEE international solid-state circuits conference digest of technical papers (ISSCC), Feb 2012 (pp. 470–472). IEEE

Höppner, S., Haenzsche, S., Ellguth, G., Walter, D., Eisenreich, H., & Schüffny, R. (2013). A fast-locking ADPLL with instantaneous restart capability in 28-nm CMOS technology. IEEE Transactions on Circuits and Systems II: Express Briefs, 60(11), 741–745.

Höppner, S., Haenzsche, S., Scholze, S., & Schüffny, R. (2015). An all-digital PWM generator with 62.5ps resolution in 28nm CMOS technology. In: Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), May 2015.

Shin, S.-K., You, Y.-S., Lee, S.-H., Moon, K.-H., Kim, J.-W., Brooks, L., & Lee, H.-S. (2008). A fully-differential zero-crossing-based 1.2 V 10 b 26 MS/s pipelined ADC in 65 nm CMOS. In: Proceedings of the IEEE symposium on VLSI circuits, June 2008 (pp. 218–219). IEEE

Acknowledgments

This work was funded by the Leading-Edge Cluster ’Cool Silicon’ and the Center for Advancing Electronics Dresden, which are sponsored by the Federal Ministry of Education and Research (BMBF), Germany.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Haenzsche, S., Höppner, S. & Schüffny, R. A 10 bit 16-to-26 MS/s flexible window SAR ADC for digitally controlled DC–DC converters in 28 nm CMOS. Analog Integr Circ Sig Process 84, 421–431 (2015). https://doi.org/10.1007/s10470-015-0591-2

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-015-0591-2