Abstract

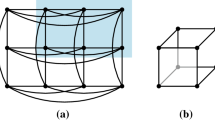

Regular arrays of processing elements in VLSI have proved to be suitable for high-speed execution of many matrix operations. To execute an arbitrary computational algorithm on such processing arrays, it has been suggested mapping the given algorithm directly onto a regular array. The computational algorithm is represented by a data-flow graph whose nodes are to be mapped onto processors in the VLSI array.

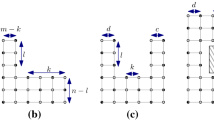

This study examines the complexity of mapping data-flow graphs onto square and hexagonal arrays of processors. We specifically consider the problem of routing data from processors in a given (source) sequence to another (target) sequence.

We show that under certain conditions, the above problem is equivalent to the one of finding a minimum-diameter cyclic arrangement. The complexity of the latter problem is analyzed and upper and lower bounds on the number of intermediate rows of processors (between the source and target rows) are derived.

Similar content being viewed by others

References

Fisher, A. L.et al., Design of the PSC: A Programmable Systolic Chip,Proc. Third Caltech Conf. on VLSI, March 1983, pp. 287–302.

Kung, S. Y., On Supercomputing with Systolic/Wavefront Array Processors,Proc. IEEE, Vol. 72, July 1984, pp. 867–884.

Li, G., and Wah, B. W., The Design of Optimal Systolic Arrays,IEEE Trans. Comput., Vol. C-34, January 1985, pp. 66–77.

Bokhari, S. H., On the Mapping Problem,IEEE Trans. Comput., Vol. C-30, March 1981, pp. 207–214.

Koren, I., and Silberman, G. M., A Direct Mapping of Algorithms onto VLSI Processing Arrays Based on the Data Flow Approach,Proc. 12th International Conf. on Parallel Processing, August 1983, pp. 335–337.

Special issue on Data Flow Systems,IEEE Comput., Vol. 15, No. 2, February 1982.

Koren, I., and Peled, I., The Concept and Implementation of Data-Driven Processor Arrays,IEEE Comput., Vol. 20, No. 7, July 1987, pp. 102–103.

Mendelson, B., and Silberman, G. M., Mapping Data Flow Programs on a VLSI Array of Processors,Proc. 14th International Symp. on Computer Architecture, Pittsburgh, PA, June 1987, pp. 72–80.

Ackerman, W. B., and Dennis, J. B., VAL—A Value-Oriented Algorithmic Language; Preliminary Reference Manual, Technical Report MIT/LCS/TR-218, Laboratory for Computer Science, Massachusetts Institute of Technology, Cambridge, MA, 1974.

Mizraian, A., Channel Routing in VLSI,Proc. 16th Annual ACM Symp. on Theory of Computing, 1984, pp. 101–107.

Preparata, F. P., and Lipski, W., Optimal Three-Layer Channel Routing,IEEE Trans. Comput., Vol. C-33, 1984, pp. 427–437.

Atallah, M. J., and Hambrusch, S. E., Optimal Rotation Problems in Channel Routing,IEEE Trans. Comput., Vol. C-35, September 1986, pp. 843–847.

Savage, J. E., Heuristics in the SLAP Layout System,Proc. International Conf. on Computer Design (ICCD), Port Chester, New York, October 1983, pp. 637–640.

Knuth, D. E.,The Art of Computer Programming, Vol. 3, Addison-Wesley, Reading, MA, 1973, Section 5.3.4.

Erdös, P., Linial, N., and Moran, S., Extremal Problems on Permutations under Cyclic Equivalence,Discrete Math., Vol. 64, No. 1, 1987, pp. 1–13.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Erdös, P., Koren, I., Moran, S. et al. Minimum-diameter cyclic arrangements in mapping data-flow graphs onto VLSI arrays. Math. Systems Theory 21, 85–98 (1988). https://doi.org/10.1007/BF02088008

Received:

Revised:

Issue Date:

DOI: https://doi.org/10.1007/BF02088008