Abstract

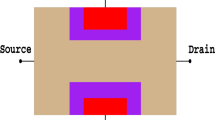

With respect to semiconductor industry, Complementary metal oxide semiconductor is considered to be successful because of integration in Integrated Circuits (ICs). As transistor size is shrinked exponentially, there is an exponential increase in number of transistors on a chip. This potential of increase in number of transistors on chip is achieved by scaling of Metal oxide semiconductor field effect transistor (MOSFET). With scaling, the characteristics of devices are also degraded. Several advanced MOSFETs like Multigate transistors (Double gate, triple gate, Gate all around), Junctionless transistors and Tunnel FETs are proposed recently. These are thought to aid Moore’s law and scaling of transistors to next decade and continue improvement in computer performance. This paper presents 2D ATLAS simulation of high-K gate dielectric engineered Double gate metal oxide field effect transistor (DGMOSFET). The performance parameters for bulk MOSFET is poor as the transistors on integrated circuit is increasing. Therefore various challenges are invoked in nanometer scale. The new devices to control these challenges is needed and thus a non planar multigate structures are emerged. These structures have shown considerably better performance in nanometer scale. The surface potential for different dielectric materials for a fixed channel length and variation of surface potential for different channel lengths in a fixed dielectric materials is shown. In similar way the electron concentration along the length of channel is shown. The \(I_{DS}\) versus \(V_{DS}\) graphs are also shown for different materials. The electrical characteristics of proposed device is shown in this paper. The proposed device has shown very good \(I_{ON}\), \(I_{OFF}\) and \(I_{ON}/I_{OFF}\) ratio.

Similar content being viewed by others

References

I. Ferain, C. Colinge, J. Colinge, Multigate transistors as the future of classical metal-oxide-semiconductor field-effect transistors. Nature 479, 310–316 (2011)

K. Girija Sravani, K. Guha, K. Srinivasa Rao ( 2018) An investigation on capacitance modeling of step strcture RF MEMS perforated shunt switch, in Proceedings of International Conference on 2018 IEEE Electron Device Kolkata Conference, EDKCON 2018, pp. 302–311

K. Srinivasa Rao, S. Sravya, G.S.K. Varma, K. Girija Sravani, Design of low actuation voltage RF MEMS capacitive switch using serpentine flexure and rectangular perforations. J. Adv. Res. Dyn. Control Syst. 10(2), 523–528 (2018)

K. Rao, L.N. Srinivasa, K. Thalluri, K. Guha, Sravani K. Girija (2018) Fabrication and characterization of capacitive RF MEMS perforated switch. IEEE Access 77519–77528

K. Girija Sravani, K. Srinivasa Rao, Analysis of RF MEMS shunt capacitive switch with uniform and non-uniform meanders. Microsyst. Technol. 24(2), 1309–1315 (2018)

J. Sateesh, K. Girija Sravani, R. Akshay Kumar, K. Guha, K. Srinivasa Rao, Design and flow analysis of MEMS based piezo-electric micro pump. Microsyst. Technol. 24(3), 1609–1614 (2018)

K. Girija Sravani, K. Guha, K.L. Baishnab, G. Shanti, K.S. Srinivasa Rao (2018) Design of low pull-in voltage and high isolation of step structure capacitive RF MEMS switch for satellite applications, in Proceedings of international conference on 2018 IEEE electron device Kolkata Conference, EDKCON 2018, pp. 312–322

A. Samal, S.L. Tripathi, S.K. Mohapatra, A journey from bulk MOSFET to 3 nm and beyond. Trans. Electr. Electron. Mater. 21, 443–455 (2020)

R.H. Dennard, F.H. Gaensslen, V.L. Rideout, E. Bassous, A.R. LeBlanc, IEEE J. Solid-State Circuits 9, 256 (1974)

V.M. Pathak, G. Saini, A graded channel dual-material gate junctionless MOSFET for analog applications. Proced. Comput. Sci. 125, 825–831 (2018)

N. Mendiratta, S. Tripathi, A review on performance comparison of advanced MOSFET structures below 45 nm technology node. J. Semicond. 41, 061401 (2020)

Y. Uemoto, E. Fujii, F. Emoto, A. Nakamura, K. Senda, A high-voltage polysilicon TFT with multigate structures. IEEE Trans. Electron Dev. 38(1), 95–100 (1991)

Yang.Ji-Woon, J. G. Fossum, , On the feasibility of nanoscale triple-gate CMOS transistors. IEEE Trans. Electron Dev. 52(6), 1159–1164 (2005)

K. Castellani-Coulie, D. Munteanu, J.L. Autran, V. Ferlet-Cavrois, P. Paillet, J. Baggio, Analysis of 45-nm multi-gate transistors behavior under heavy ion irradiation by 3-D device simulation. IEEE Trans. Nucl. Sci. 53(6), 3265–3270 (2006)

A. Sarkar, A.K. Das, S. De, C.K. Sarkar, Effect of gate engineering in double-gate MOSFETs for analog/RF applications. Microelectron. J. 43(11), 873–882 (2012)

J. Yuan, J.C.S. Woo, Tunable work function in fully nickel-silicided polysilicon gates for metal gate MOSFET applications. IEEE Electron. Device Lett. 26, 87–89 (2005)

B.-W. Hwang, J.-W. Yang, S.-H. Lee, Explicit analytical current-voltage model for double-gate junctionless transistors. IEEE Trans. Electron. Dev. Inst. Electr. Electron. Eng. 62(1), 171–177 (2015)

B. Ho, X. Sun, C. Shin, T.K. Liu, Design optimization of multigate bulk MOSFETs. IEEE Trans. Electron Devices 60(1), 28–33 (2013)

R. Maity, N.P. Maity, K. Srinivasa Rao, K. Guha, S. Baishya, A new compact analytical model of nanoelectromechanical systems-based capacitive micromachined ultrasonic transducers for pulse echo imaging. J. Comput. Electron. 17(3), 1334–1342 (2018)

M. Sonali, K. Aravind, G. Keerthika, K. Srinivasa Rao, Design and electromechanical analysis of RF MEMS switch for low actuation voltage. J. Adv. Res. Dyn. Control Syst. 10(2), 357–362 (2018)

K. Girija Sravani, K. Guha, K. Srinivasa Rao, Analysis on selection of beam material for novel step structured RF-MEMS switch used for satellite communication applications. Trans. Electr. Electron. Mater. 19(6), 467–474 (2018)

K. Vijaya Prasad, P.V.V. Kishore, O. Srinivasa Rao, Skeleton based view invariant human action recognition using convolutional neural networks. Int. J. Recent Technol. Eng. 8(2), 4860–4867 (2019)

K. Girija Sravani, K. Guha, K. Srinivasa Rao, Design and analysis of serpentine flexure based RF MEMS switch for high isolation with low pull-in voltage. Trans. Electr. Electron. Mater. 20(2), 154–164 (2019)

T.N. Kolanti, S. Vemu, R.K. Vobulapuram, S.R. Karumuri, Modeling of CMS-based nonuniform interconnects using FDTD technique. Int. J. Circuit Theory Appl. 47(1), 43–54 (2019)

G.R.K. Prasad, P.S. Srinivas Babu, N. Siddaiah, K. Srinivasa Rao, Design and simulation of MEMS based sensor for early detection of PD, in 2016 International Conference on Electrical, Electronics, Communication, Computer and Optimization Techniques, ICEECCOT 2016, pp. 366–371 (2017)

R. Bose, J.N. Roy, 2D Surface potential and mobility modelling of doped/undoped symmetric double gate MOSFET. IET Circuits Devices Syst. 13(5), 571–575 (2019)

Atlas user’s manual, Silvaco, Santa Clara (CA, USA, 2016)

A. Sirohi, C. Sahu, J. Singh, Analog/RF performance investigation of dopingless FET for ultra-low power applications. IEEE Access 7, 141810–141816 (2019)

F. Horst, A. Farokhnejad, Q. Zhao, B. Iñíguez, A. Kloes, 2-D physics-based compact DC modeling of double-gate tunnel-FETs. IEEE Trans. Electron Devices 66(1), 132–138 (2019)

F. Djeffal, H. Ferhati, T. Bentrcia, Improved analog and RF performances of gate-all-around junctionless MOSFET with drain and source extensions. Superlattices Microstruct. 90, 132–40 (2016)

S.S. Zaman, P. Kumar, M.P. Sarma, A. Ray, G. Trivedi, Design and simulation of SF-FinFET and SD-FinFET and their performance in analog, RF and digital applications, in 2017 IEEE International Symposium on Nanoelectronic and Information Systems (iNIS). Bhopal, India, pp. 200–205 (2017)

S.K. Dargar, V.M. Srivastava, Design of double-gate tri-active layer channel based IGZO thin-film transistor for improved performance of ultra-low-power RFID rectifier. IEEE Access 8, 194652–194662 (2020)

K.S. Singh, S. Kumar, K. Nigam, Impact of interface trap charges on analog/RF and linearity performances of dual-material gate-oxide-stack double-gate TFET. IEEE Trans. Device Mater. Reliab. 20(2), 404–412 (2020)

G.S. Sivaram, S. Chakraborty, R. Das, A. Dasgupta, A. Kundu, C.K. Sarkar, Impact of lateral straggle on the analog/RF performance of asymmetric gate stack double gate MOSFET. Superlattices Microstruct. 97, 477–88 (2016)

Acknowledgements

The authors would like to thank Department of ECE, National Institute of Technology Silchar and Mizoram University, for providing the necessary computational resources.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Aditya, M., Rao, K.S. Design and Performance Analysis of Advanced MOSFET Structures. Trans. Electr. Electron. Mater. 23, 219–227 (2022). https://doi.org/10.1007/s42341-021-00338-9

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s42341-021-00338-9