Abstract

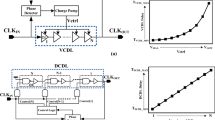

This paper presents a new anti-boundary switching fine-resolution digital delay-locked loop (DLL) for high speed memory systems. The proposed digital DLL uses a new phase-interpolator (PI)-based digitally controlled delay line structure with overlapping period to eliminate the boundary switching problem in conventional digital DLLs, achieving high delay resolution and low jitter characteristics. In addition, by applying the phase inversion scheme and the variable successive approximation register algorithm, the proposed digital DLL achieves a fast locking time of less than 114 cycles and has a wide operating frequency range of 125 MHz–2.7 GHz without producing any harmonic lock problem. Fabricated in a 0.13-µm CMOS process, the proposed digital DLL achieves a fine delay resolution of around 2.0 ps and the measured peak-to-peak output clock jitter is only 8.75 ps at 2.7 GHz. The proposed digital DLL occupies an active area of only 0.05 mm2 and dissipates 8.6 mW of power from a 1.2 V supply at 2.0 GHz.

Similar content being viewed by others

References

Kang, H., et al. (2012). Process variation tolerant all-digital 90° phase shift DLL for DDR3 interface. IEEE Transactions on Circuits and Systems I: Regular Papers, 59, 2186–2196.

Jung, D., et al. (2015). All-digital fast-locking delay-locked loop using a cyclic-locking loop for DRAM. IEEE Transactions on Circuits and Systems II: Express Briefs, 62, 1023–1027.

Sohn, K., et al. (2006). A 1.2 V 30 nm 3.2 Gb/s/pin 4 Gb DDR4 SDRAM with dual-error detection and PVT-tolerant data-fetch scheme. IEEE Journal of Solid-State Circuits, 48, 168–177.

Lim, J., et al. (2016). A delay locked loop with a feedback edge combiner of duty-cycle corrector with a 20%–80% input duty cycle for SDRAMs. IEEE Transactions on Circuits and Systems II: Express Briefs, 63, 141–145.

Park, D., Park, G., & Kim, K. (2017). A 0.15 to 2.2 GHz all-digital delay-locked loop. In 15th IEEE international new circuits and systems conference (NEWCAS) 2017 (pp. 261–264).

Lee, Hyun-Woo, et al. (2014). Survey and analysis of delay-locked loops used in DRAM interfaces. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 22, 701–711.

Han, S., & Kim, J. (2012). A high-resolution wide-range dual-loop digital delay-locked loop using a hybrid search algorithm. In IEEE Asian solid state circuits conference (A-SSCC) (pp. 293–296).

Yang, R., et al. (2007). A 40–550 MHz harmonic-free all-digital delay-locked loop using a variable SAR algorithm. IEEE Journal of Solid-State Circuits, 42, 361–373.

Kwak, J-T., et al. (2003). A low cost high performance register-controlled digital DLL for 1 Gbps x32 DDR SDRAM. In Symposium on VLSI circuits, digest of technical papers (pp 283–284).

Yun, Won-Joo, et al. (2011). A 3.57 Gb/s/pin low jitter all-digital DLL with dual DCC circuit for GDDR3 DRAM in 54-nm CMOS technology. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 19, 1718–1722.

Han, S., Kim, T., & Kim, J. (2013). A 0.1–1.5 GHz all-digital phase inversion delay-locked loop. In IEEE Asian solid state circuits conference (A-SSCC) (pp. 341–344).

“Main memory: DDR4 & DDR5 SDRAM” https://www.jedec.org/category/technology-focus-area/main-memory-ddr3-ddr4-sdram.

Acknowledgements

This work was supported by the KIAT grant funded by the Korean government (MOTIE: Ministry of Trade, Industry and Energy, HRD Program for Software-SoC convergence. No. N0001883). The EDA tools were supported by IDEC.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Kim, J. An anti-boundary switching fine-resolution digital delay-locked loop. Analog Integr Circ Sig Process 96, 445–454 (2018). https://doi.org/10.1007/s10470-018-1206-5

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-018-1206-5