Abstract

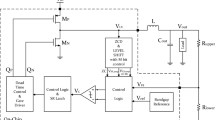

In present-day integrated digital circuits are become attractive choice for the DC–DC buck converters. This paper proposes a novel approach of CMOS DC–DC buck converter with double-chain digital pulse width modulation (PWM) for ultra-low power applications. The proposed digital PWM architecture consists of double delay lines which is to reduce power consumption and improves ripple voltage with the resolution. An algorithm is proposed that describes the operation of digital PWM. The double chain digital PWM is implemented and analyzed in cadence platform using commercial 180 nm TSMC design kit. The promising results reveals that the power consumption is reduces up to 1.16 µW with occupies less area under the operating frequency of 100 kHz. The DC–DC buck converter with proposed PWM achieves peak efficiency of 92.6% including a load current range of 4–10 mA. This proposed digital PWM method demonstrates its ability to minimize the ripple voltage by 49% and enables to DC–DC converter for compose in a compact chip area as compared to conventional converters. Measured and Simulated power efficiency are made good agreement with each other.

Similar content being viewed by others

References

Alippi, C., & Galperti, C. (2008). An adaptive system for optimal solar energy harvesting in wireless sensor networks node. IEEE Transactions on Circuits and Systems, 55, 1742–1750.

Li, Q. (2012). A fully-integrated buck converter design and implementation for on-chip power supplies. Journal of Computers, 5, 1270–1277.

Sizikov, G., Kolodny, A., Fridman, E. G., & Zelikson, M. (2010). Efficiency optimization of integrated DC–DC buck converters. In 17th International Conference on Electronics, Circuits and Systems (pp. 1208–1211).

Wang, A., & Chandrakasan, A. (2005). A 180-mV subthreshold FFT processor using a minimum energy design methodology. IEEE Journal of Solid-State Circuits, 40, 310–319.

Ramadass, Y., & Chandrakasan, A. (2008). Minimum energy tracking loop with embedded DC–DC converter enabling ultra-low voltage operation down to 250-mV in 65 nm CMOS. IEEE Journal of Solid-State Circuits, 43, 256–265.

Fan, S., Wang, K., & Geng, L. (2010). Design and implementation of mixed signal boost converter with a novel multi-phase clock DPWM. IEICE Electronics Express, 7, 1091–1097.

Wang, H., Hu, X., Wang, S., Zhao, G., & Luo, D. (2013). A 5 MHz integrated digital DC–DC converter with a delay line ADC and ∑-∆ DPWM. IEICE Electronics Express, 10, 1–12.

Wang, W. W., Shen, Z. H., Tan, X., Yan, N., & Min, H. (2011). Improved delay line based digital PWM for DC–DC converters. Electronics Letters, 47, 562–564.

Zhang, X., Chen, P., Okuma, Y., Ishida, K., Ryu, Y., Watanabe, K., et al. (2014). A 0.6 V Input CCM/DCM operating digital buck converter in 40 nm CMOS. IEEE Journal Solid-State Circuits, 49, 2377–2386.

Zhang, X., Chen, P., Ryu, Y., Ishida, K., Okuma, Y., Watanabe, K., Sakurai, T., & Takamiya, M. (2012). A 0.45 V input on-chip gate boosted (OGB) buck converter in 40 nm CMOS with more than 90% efficiency in load range from 2 to 50 μW. In IEEE Symposium on VLSI Circuits, (pp. 194–195).

Chen, P., Wu, C., & Lin, K. (2016). A 50 nW-to-10 mW output power tri-mode digital buck converter with self-tracking zero current detection for photovoltaic energy harvesting. IEEE Journal of Solid-State Circuits, 51, 523–532.

Huand, C., & Chen, C. (2011). A fast and high efficiency with switch on demand modulator for wide load applications. IEICE Electronics Express, 12, 963–968.

Hauke, B. (2012). Basic calculation of a buck converter’s power stage. Texas Instruments Inc. Report, (pp. 1–7).

Acknowledgements

This work was supported by Inje University Grant 2016 and Human Resource Training Program for Regional Innovation and Creativity, through the Ministry of Education and National Research Foundation of Korea (NRF-2014H1C1A1066686).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Kumar, S., Choi, J. & Song, H. An ultra-low power CMOS DC–DC buck converter with double-chain digital PWM technique. Analog Integr Circ Sig Process 92, 141–149 (2017). https://doi.org/10.1007/s10470-017-0983-6

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-017-0983-6