Abstract

Within integrated circuit design, parasitic capacitance associated with the realisation of a resistor can limit circuit performance for certain applications, such as the analogue-to-digital converter. In this paper, a segmentation guarding layout technique is introduced that offers the circumvention of the parasitic capacitance of integrated resistors. The segmentation guarding technique is demonstrated on both diffusion and polysilicon integrated resistors.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Passive components, such as integrated resistors, are key elements of analogue and mixed-signal integrated circuit (IC) systems. The designed impedance of such resistors are dependent on the doping level, the resistivity of process material and the layout dimensions. The electrical parasitic reactance associated with an integrated resistor of a given geometry varies with temperature and voltage offset [1, 2]. The temperature changes the mobility of carriers, built-in potential and the depletion width of the resistor and substrate. Voltage variation causes the change of mobility and the depletion width of the resistor body. In order to characterise integrated resistors, models have been proposed and studied over several years; the equivalent circuits of both the diffusion and polysilicon resistor are shown in Fig. 1 [3,4,5,6]. The 3-terminal models, including two nodes and a substrate terminal, yield an accurate electrical behavioural model which may be used when the substrate under the resistor area is not connected to the reference ground (conventional two-terminal resistor models always bias the substrate to the ground) [1]. These models are lumped approximations; in reality, the capacitance is distributed along the length of the resistor.

The diffusion resistor and polysilicon resistor are commonly used in IC design. As shown in Fig. 1(a), the model of a diffusion resistor consists of contact resistances (R xa and R xb ), substrate resistance (R xt ), two p–n junction diode current sources (I ra and I rb ) and parasitic capacitances (C ja C jb and C jc ). Such capacitances are dominated by the depletion junction capacitance [1]. Figure 1(b) shows the equivalent circuits for a polysilicon resistor; its parasitic capacitance C is dominated by the poly-oxide capacitance [3].

The impedance of these types of integrated resistors is reduced by the capacitive parasitic current at high frequencies. This current is proportional to the charging potentials across such capacitances. A shielding voltage with equal potential mitigates the capacitive reactance as no charge flow results.

2 Proposed segmentation guarding technique

In the IC platform, ratios of the resistance of integrated resistors may be easily implemented by conventional methods, such as matching and dummy structure layout techniques. However, the frequency response of IC resistors with conventional layout is dominated by the parasitic capacitance at high frequencies.

The RF SPICE models of IC resistors, as given in Fig. 2, contain two types of parasitic capacitance; the stray capacitance of the resistor body (C p ) and resistor-to-substrate capacitance (C s ) [7].

For the simulation and analysis (Fig. 2), the input signal is applied at node 1 or 2 and the substrate is connected to ground (common terminal). The transfer function can be written as,

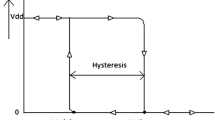

As the transfer function shows, the model has a pole and a zero in frequency domain. The zero is determined by the stray capacitance. The pole is controlled by both stray and resistor-to-substrate capacitance. In conventional IC design, C s is a few orders larger than C p . The approximate frequency response of the model is illustrated in Fig. 3. The usable frequency range of the IC resistor is dominated by the pole. However, to increase this frequency range, both C s and C p need to be mitigated.

The slope of the roll-off for the pole, as demonstrated in Eq. (1), is determined by both C s and C p . An accurate ratio of the resistors is the key of common circuit performances, such as the instrumentation amplifier. In Fig. 4(a), (b), the frequency response of two polysilicon resistors, one each for 1 and 10 MΩ are depicted. The resistors are standard-layout, according to the AMS 0.35 µm process [7]. The simulation curves in Fig. 4 are plotted by Cadence Virtuoso [8].

The pole (f P1 ) and zero (f Z1 ) frequency for the 1 MΩ resistor are approximately located at 50 MHz and 5 GHz. For the 10 MΩ resistor, its pole (f P10 ) and zero (f Z10 ) frequency are around 10 and 500 MHz.

The ratio of these two resistors, as shown in Fig. 4(c), decreases at approximately 10 MHz (f P10 ), which is determined by the 10 MΩ resistor due to its larger die area which brings about larger parasitic capacitance.

The derivative of resistor ratio is given in Fig. 4(d). It decreases between f P10 and f P1 , and is dominated by the 10 MΩ resistor. It then increases between f P1 and f Z10 , due to the impedance of both resistors reducing within this frequency range. When the frequency increases to 500 MHz (f Z1 ), the rate of increasing lowers as the impedance of the 1 MΩ resistor becomes constant. Eventually, as shown in Fig. 4(c), (d), if the frequency is higher than both zeros of the resistors, in this frequency range the impedance ratio is dominated by the parasitic capacitance (or the die area of the resistor), which is not same as the designed resistance ratio. Hence, it is necessary to mitigate the parasitic capacitance of the IC resistors, especially for the large die area devices.

The traditional guarding, or shielding, technique which applies a guarding potential equal to the voltage at one end terminal of the resistor, is a commonly used layout technique to reduce the effect of parasitic capacitance [9,10,11]. However, a closer guarding voltage, with regards to the potential at a point along the resistor’s length, will provide a better mitigation of the effect of parasitic capacitance.

This is most simply applied by providing the average of the terminals’ voltage as the guarding potential. In Fig. 5, a resistor R has two node voltages, V N1 and V N2 , and its shield is connected to V shield . Two node voltages, V N1′ and V N2′ , are the buffered voltages of V N1 and V N2 , respectively. Also, as shown in Fig. 5, the two segmentation resistors R a and R b are equal, and are used as a pair to ensure the shielding voltage V shield is the average of these buffered node voltages.

The voltage buffers are formed, as shown in Fig. 6, by low-noise two-stage Complementary Metal-Oxide Semiconductor (CMOS) operational amplifiers (OPAMPs) [12, 13]. In this study, the proposed circuits are targeted at IC implementation and simulated on the AMS 0.35 µm CMOS process [7]. The device geometries are given in Table 1.

Simple linear integration of the difference between the shield voltage and resistor voltage over length shows that the total charge on the parasitic capacitance is halved.

The precise bode plot of the OPAMP design is shown in Fig. 7. The frequency domain response of the OPAMP indicates that, it achieves circa a 58° phase margin and 5.4 dB gain margin. The bandwidth of the OPAMP is circa 3 kHz (3 dB).

The AC simulation of the voltage buffer is depicted in Fig. 8. It is able to track the input voltage up to 10 MHz which covers the frequency range of the simulated IC resistors.

For a large resistor, a more efficient Segmentation Guarding (SG) is employed by segmenting the long device into equal-length smaller resistors in series. A testbench is shown in Fig. 9, in which ‘Seg 1’, ‘Seg 2’, ‘Seg 4’ and ‘Seg 8’ indicate the number of target resistors employed. Each of the target resistors is guarded by a shield held at a potential tapped from a node providing the average voltage across that resistor.

The impedance of the IC resistors (Z in Eq. 2) is reduced by the current into the parasitic capacitance at high frequencies,

where, V in the input voltage, I r is the current into the resistance, I p is the current into the capacitance C p and I s is the current into the capacitance C s .

Without guarding, the current into stray capacitance (I p_no ) can be written as,

and, the current into the substrate capacitance (I s_no ) is,

where, n is the number of the potential SG resistor pairs.

When the SG is applied, the current into stray capacitance (I p_SG ) becomes,

and, the current into the substrate capacitance (I s_SG ) is,

Therefore, as the equations show above, the SG can effectively reduce the current into parasitic capacitance, so that the usable frequency range of IC resistors are increased.

Without guarding, the power consumption for the IC resistors, both diffusion and polysilicon resistor, is about 50 µW. When the SG technique is implemented, the power consumption increases to circa 460 µW. The power for each voltage buffer, formed by the OPAMP, is approximately 210 µW. The power consumption of the OPAMP can be reduced by decreasing the biasing current.

3 Results

The testing configurations are given in Table 2. For both diffusion and polysilicon resistors, a relatively high overall resistance of 80 MΩ is selected, consisting of eight 10 MΩ resistors in series. The area of the diffusion resistors is larger, as the bulk resistivity is lower than the polysilicon, which leads to greater parasitic capacitance. For the SG resistors, sixteen 1 kΩ polysilicon resistors are used, to provide corresponding shielding voltages for both the diffusion and polysilicon resistors under test. A ‘no guarding’ test is also implemented as the benchmark. The device geometries of the IC resistors are given in Table 3.

The proposed SG technique is implemented on the AMS 0.35 µm CMOS process [7]. P-type diffusion resistors are used, and the N-wells underneath the target resistors held at the shielding potentials. As given in Table 2, five tests are carried out with different numbers of segmentations. A 1 V AC voltage is applied across the total target resistance in all tests, the corresponding AC currents are depicted in Fig. 10(a). At lower frequencies, the current through the target diffusion resistors of all tests are approximately equal. As the frequency increases, especially above 10 kHz, the current of the ‘no guarding’ test increases significantly, which is caused by the parasitic capacitive reactance. The impedance of the parasitic junction capacitance decreases with the increasing of frequency. The current into the target resistor is dominated by the parasitic capacitance at high frequencies. When the SGs are applied, the rate of increase of AC current with frequency decreases with increasing number of segmentations. As shown in Fig. 10(b), the calculated impedance indicates that, with the SGs providing closer shielding voltages that track the distributed voltage along the length of the resistor, the parasitic capacitance of the target diffusion resistor is increasingly mitigated.

For the polysilicon resistor, the shielding voltages are also applied to the N-wells underneath the target resistors. As shown Fig. 11(a), the parasitic current generated by the capacitive reactance for the ‘no guarding’ test becomes noticeable when the frequency is above 500 Hz. The impedances of different tests are plotted in Fig. 11(b). It implies that the more SGs are implemented, the lesser the parasitic current; and, therefore, the more parasitic capacitance is circumvented.

A second on-chip testbench (TB) is implemented, as given in Fig. 12, an 80 MΩ polysilicon IC resistor is connected in series with a voltage buffer. The equivalent input impedance of the buffer is circa 42 GΩ [14]. The voltage across the resistor R ploly is detected and amplified by the instrumentation amplifier,

where, V in in the input voltage, V x is the node voltage and A ins is the gain of the instrumentation amplifier.

The experiment results are given in Fig. 13. The amplitude of the input signal is 100 mV, and the frequency is 1 kHz. The gain of the instrumentation amplifier is approximately 1.5 k. For the ‘no guarding’ test, as shown in Fig. 13(a), the output of the instrumentation amplifier is saturated. It is caused by the phase shift between V in and V x , which is determined by the capacitive reactance of the polysilicon resistor. When the SG technique (8 pairs of SG guarding resistors) is implemented, as shown in Fig. 13(b), the phase shift is significantly reduced, due to the effective circumvention of the parasitic capacitance.

An accurate measurement of the amplitude and phase difference for the IC resistor with different numbers of SG can be attained by implementing a suppression loop system [15].

4 Conclusion

A resistor segmentation layout guarding technique is demonstrated for IC implementation that offers better circumvention of parasitic capacitance than the conventional guarding technique. The key degree of freedom exploited is that a shield providing the average voltage, with respect to the end terminals’ potential across the resistors’ length offers a closer guarding voltage. The impedance of such resistors is dominated by the capacitive reactance at high frequencies. The usable frequency range of the IC resistor is limited by the large parasitic capacitance, using the conventional guarding technique.

By segmenting a long-length resistor into an increasing number of guarded devices, the die area of individual sub-devices is reduced. The parasitic capacitance of each smaller device, both stray capacitance of the resistor body and the resistor-to-substrate capacitance, is increasingly mitigated. This increases the usable frequency range of the integrated resistor. A concept-providing prototype is presented, and the simulated results indicate that a lower effective capacitive reactance of the integrated resistor is achieved by providing more SGs.

References

Booth, R., & McAndrew, C. (1997). A 3-terminal model for diffused and ion-implanted resistors. IEEE Transactions on Electron Devices, 44(5), 809–814.

Steinmann, P., Beach, E., Meinel, W., Chatterjee, A., Weiser, D., Bucksch, R., et al. (2010). Simple analytical model of the thermal resistance of resistors in integrated circuits. IEEE Transactions on Electron Devices, 57(5), 1029–1036.

Spessot, A., Molteni, M., Ventrice, D., & Fantini, P. (2010). A physics-based compact model for polysilicon resistors. IEEE Electron Device Letters, 31(11), 1251–1253.

Wilson, G., & Chan, P. K. (1993). Floating CMOS resistor. Electronic Letters, 29(3), 306–307.

Popa, C., & Manolescu, A. (2007). CMOS differential structure with improved linearity and increased frequency response. In 30th Edition Annual Semiconductors Conference (CAS) ), Sinaia, Romania (pp. 517–520).

Vavelidis, K., Tsividis, Y. P., Eynde, F. O., & Papananos, Y. (1997). Six-terminal MOSFET’s: Modelling and applications in highly linear, electronically tunable resistors. IEEE Journal of Solid-State Circuits, 32(1), 4–12.

Austria MicroSystem, ‘CMOS C35 process parameters’. (2015). Available at http://asic.ams.com/cgi-docs/ENG-182_rev8.pdf. Accessed 01 July 2015.

Virtuoso analog design environment. (2016). Available at https://www.cadence.com/custom-ic-analog-rf-design/circuit-design/virtuoso-analog-design-environment.html. Accessed 21 Feb 2017.

Hastings, A. (2005). “Art of analog layout”, the (2nd edition) (2nd ed.). United States: Pearson/Prentice Hall.

Michael, C., Abel, C., & Ismail, M. (1993). Statistical modeling for computer-aided design of MOS VLSI circuits. Bonn: Kluwer Academic Publishers.

Heineken, H. T., Khare, J. & d’Abreu, M. (1998). Manufacturability analysis of standard cell libraries. In Proceedings of IEEE 1998 Custom Integrated Circuit Conference, (pp. 321–324).

Wu, C., Chen, W., & Kuo, L. (2013). A CMOS power-efficient low-noise current-mode front-end amplifier for neural signal recording. IEEE Transactions on Biomedical Circuits and Systems, 7(2), 107–114.

Zhou, Z., & Warr, P. A. (2016). A high input impedance low noise integrated front-end amplifier for neural monitoring. IEEE Transactions on Biomedical Circuits and Systems, 10(6), 1079–1086.

Zhou, Z., & Warr, P. A. (2016). Back-gate current neutralisation feedback loop for high-input impedance neural FEAs. Electronics Letters, 52(19), 1586–1588.

Warr, P. A., & Bissonauth, N. (2010). Amplitude offset estimation by phase comparison in suppression loops. IEEE Transactions on Microwave Theory and Techniques, 58(7), 1742–1747.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

Open Access This article is distributed under the terms of the Creative Commons Attribution 4.0 International License (http://creativecommons.org/licenses/by/4.0/), which permits unrestricted use, distribution, and reproduction in any medium, provided you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made.

About this article

Cite this article

Zhou, Z., Warr, P. A segmentation layout guarding technique to mitigate parasitic capacitance of integrated resistors. Analog Integr Circ Sig Process 93, 237–243 (2017). https://doi.org/10.1007/s10470-017-0982-7

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-017-0982-7