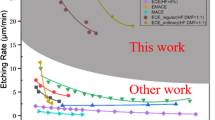

We used silicon molding and examined the protective layer on a silicon molded Peltier array. Both a large p-type array and n-type array were created with the protective layer. Because the conventional bismuth-antimony-telluride (BiSbTe) alloys react with XeF2 etching gas rapidly, we need to place the protective layer at the interface between the silicon and the thermoelectric material using the water vapor thermal oxidization method. As the xenon difluoride selective etching ratio of silicon and SiO2 is about 100:1, the protective layer is damaged if the removal ratio of silicon is high and the etching process time is long. Next we examined a new method involving both an anisotropic process using deep reactive ion etching (DRIE) and an isotropic process using XeF2 etching, and we formulated an etching process that causes no damage to the protective layer.

Similar content being viewed by others

References

K. Pettigrew, J. Kirshberg, K. Yerkes, D. Trebotich, and D.␣Liepmann, MEMS2001 (2001), p. 427.

J.P. Fleurial, G.J. Snyder, J.A. Herman, P.H. Giauque, W.M. Phillips, M.A. Ryan, P. Shakkottai, E.A. Kolawa, and M.A. Niclolet, Proceedings of the 18th International Conference on Thermoelectrics (1999), p. 294

H. Böttner, J. Nurnus, A. Gavrikov, G. Kühner, M. Jägle, C. Künzel, D. Eberhard, G. Plescher, A. Schubert, and K.H. Schlereth, J. Microelectromech. Syst. 13, 3, 414 (2004)

A. Shakouri and J.E. Bowers, Appl. Phys. Lett. 71, 1234 (1997).

J.F. Li, S. Tanaka, T. Umeki, S. Sugimoto, M. Esashi, and R. Watanabe, Sens. Actuators. A. 108, 97 (2003) doi:10.1016/S0924-4247(03)00369-8

P.R. Morrow, C.M. Park, S. Ramanathan, M.J. Kobrinsky, and M. Harmes, IEEE Electron Device Lett. 27, 335 (2006)

Acknowledgements

The authors thank Assistant Professor Shuji Tanaka at Tohoku University for his advice on the␣silicon molding method and Shinji Tanaka at␣the Advanced Materials Laboratories of Sony␣for his work on the TEM analysis and observations.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Tonosaki, M., Ishida, Y. & Ryoson, H. Effect of Protective Layer and Etch Process on Silicon Molded Micro Peltier Arrays. J. Electron. Mater. 38, 968–973 (2009). https://doi.org/10.1007/s11664-009-0671-0

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11664-009-0671-0