Abstract

In this paper, a flexible cascaded multilevel inverter is proposed with a wide operational range. The inverter can change its topology structure to operate in three modes by a bidirectional switch unit. The nine-level or five-level mode of the inverter is adopted to optimize the output waveform when the input power is low. To decrease power losses, the three-level mode of the inverter is adopted to reduce the number of active switch devices when the input power is high. The topology and modulation strategy of the proposed inverter are presented and analyzed. The total losses and current THD of the inverter are calculated. In addition, simulations and experiments are conducted. The obtained simulation and experimental results indicate the correctness and feasibility of the proposed inverter and its modulation strategy.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Nowadays, photovoltaic systems are becoming more popular due to their advantages in terms of unlimited reservation, pollution-free and convenient utilization [1]. As a core piece of equipment for photovoltaic systems, inverters play an important role in reducing output harmonics and improving system efficiency [2]. Compared with traditional two-level inverters, multilevel inverters are more suitable for PV systems due to their unique characteristics [3,4,5]. Multilevel inverters come with the benefits of reduced du/dt, reduced device voltage stress, improved output waveform quality and smaller filter inductance [6,7,8]. These benefits make it easier to meet the demands in photovoltaic applications.

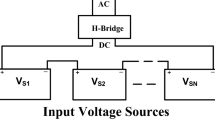

There are a few classics multilevel inverter topologies. These classes are the neutral point clamped topology (NPC) [9,10,11], the flying capacitor topology (FC) [12, 13], and the cascaded H-bridge topology (CHB) [14,15,16]. NPC inverters are widely used in photovoltaic systems due to their characteristics of low switch losses, and freedom from common-mode leakage current. However, all of the NPC inverters need to solve the problem of capacitor voltage balance on dc side. CHB inverters can heighten the voltage rank by series connections. However, CHB converters require multiple sets of isolated dc sources, which is a main drawback of this topology.

Topologies with the multilevel structure have good output characteristics due to their ability to produce staircase-like voltage waveforms. However, multilevel inverters exhibit an important limitation. For an increased number of output levels, they require many power switches, which increases the cost, control complexity and the losses of devices [17]. In photovoltaic applications, the output power of PV cells spans a wide range and varies greatly [18,19,20,21]. Due to the wide input range of inverters, the power levels of the power devices and filter inductor are selected from the maximum output power. This leads to high device cost, high losses and low system utilization.

There is a contradiction between achieving a wide operational range and reducing power losses [22, 23]. For the past few years, efforts have been directed to reduce the cost and losses in multilevel inverters, and many topologies have appeared. In [24] and [25], a T-type inverter with a significant reduction in the number of power devices was described. In addition, this topology can be applied to any number of voltage levels within the switch maximum voltage. The losses are decreased since higher voltage rated switches operate at the fundamental frequency in this topology. In [26], a multilevel inverter using the series/parallel conversion of dc voltage sources was proposed. When the capacitors are connected in series, the voltage of devices is reduced, as well as the total losses of the devices. In [27], a flying capacitor clamped inverter based on a switched-capacitor was proposed. Its modulation strategy reduced the losses of the switch devices by curtailing the switch frequency of certain switches. In [28], an H-bridge inverter with dc side switches was proposed and applied to a PV system. In this topology, the bridge arm switches operate at a low frequency, which reduces the switch losses. The above inverter topologies reduced losses by optimizing the topology structure. However, all of the switches are always under operating state, and the total losses are still large.

Considering the actual conditions in a PV system, the operational range of an inverter should be wide. Different output characteristics of an inverter are needed under different conditions. This paper proposes a cascaded multilevel inverter. Based on a wide operational range, the inverter can provide different output characteristics to adapt to different conditions. Using a bidirectional switch unit, the proposed inverter can change its topology structure to operate in three modes: nine-level mode, five-level mode and three-level mode. When the dc input power is low, the nine-level or five-level mode can provide more output levels to improve the quality of the output waveform. When the dc input power is high, the three-level mode can reduce the number of active switch devices to decrease the inverter losses.

This paper is organized as follows. Section 2 introduces the topology of a cascaded multi-mode inverter, and modulation methods of the three modes are described in detail. In addition, the capacitor voltage balance on the dc side is analyzed. Section 3 analyzes and calculates the losses and the current total harmonic distortion of the inverter during the three modes. Section 4 offers simulation and experimental results. Section 5 provides some conclusions for this paper.

2 Cascaded multimode inverter and its modulation strategy

2.1 Topology structure

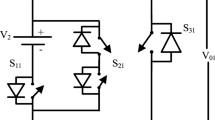

The topology of the proposed cascaded multilevel inverter is presented in Fig. 1a. It consists of twelve switches S1–S12, and a bidirectional switch unit S0. In addition, it also contains four clamping diodes D1–D4, four clamping capacitors C1–C4, and two dc voltage sources. By the bidirectional switch unit, the proposed inverter can change its topology structure to operate in three operation modes. According to different working conditions, different operation modes can be applied.

The three working modes are presented as follows. (1) Keep the bidirectional switch S0 off, and the topology is a cascaded nine-level inverter. This mode is called the nine-level mode, as shown in Fig. 1b. (2) Keep the bidirectional switch S0 off, keep the switches S1, S2, S7 and S8 on, and the topology is a cascaded five-level H-bridge inverter. This mode is called the five-level mode, as shown in Fig. 1(c). (3) Keep the bidirectional switch S0 as well as the switches S1, S2, S4, S7, S8 and S9 on. Meanwhile, keep switches S6 and S11 off. The topology becomes one H-bridge inverter composed of the switches S3, S5, S10 and S12. With the switches S1, S2, S4, S7 and S9 and the bidirectional switch S0 kept on, two dc sources are connected in parallel. This mode is called the three-level mode, as shown in Fig. 1d.

2.2 Modulation strategy

When the proposed inverter operates in the nine-level mode, the switches connected to the dc side (S1, S2, S7, S8) are controlled to output required waveforms, and the bridge arm switches (S3–S6, S9–S12) are controlled to change the polarity of output waveforms. Therefore, the dc side switches act at a high frequency while the bridge arm switches act at a low frequency. Taking the upper half of the topology as an example, the voltage of each capacitor is 0.5Udc. When S1 and S2 are switched on, the clamping capacitors C1 and C2 are in the discharge state, and the output voltage is Udc. When S1 is on and S2 is off, or when S1 is off and S2 is on, only one capacitor discharges. Thus, the output voltage is 0.5Udc. When both S1 and S2 are switched off, none of the capacitors discharge. Thus, the output voltage is 0.

The modulation strategy of the nine-level mode of the proposed inverter is shown in Fig. 2. It requires eight carriers (Tri1–Tri8) and one reference signal (Tref) to generate original waveforms. The amplitude of each carrier is 1, the frequency is the same, and the phase difference between adjacent carriers is 90°. Depending on modulation ratio M1, the amplitude of the reference signal Tref changes between 0 and 1. Eight sets of rectangular pulse signals are obtained by comparing the carriers and the reference signal, to control the dc side switches. In addition, the switches (S3–S6, S9–S12) are controlled by the reference signal polarity.

Moreover, the capacitors (C1–C4) clamp the dc voltage when the proposed inverter operates in the nine-level mode. The inverter can output a nine-level voltage when all the capacitor voltage is Udc/2. Thus, it is of great importance to keep the voltage balance of the capacitors. When the inverter outputs a voltage of ± Udc/2, ± Udc, ± 3Udc/2, only parts of the capacitors discharge. As a result, the capacitor voltage balance was broke. The key to achieving voltage balance is to make all of capacitors output the same energy in one cycle.

Figure 3 shows the discharge states of four capacitors, and the colored squares mean the discharge time of each capacitor. Since the carrier frequency is much higher than the modulation frequency, the reference signal in Fig. 3 can be seen as a horizontal line. The amplitude of the carriers is 1. When the reference signal is in the interval of [0, 0.25], the inverter outputs a voltage of 0 or Udc/2. As a result, there are 0 or 1 capacitor discharges at the same time, as shown in Fig. 3a. Similarly, when the reference signal is in the interval of [0.25, 0.5], there are 1 or 2 capacitors discharged at the same time, as shown in Fig. 3b. When the reference signal is in the interval of [0.5, 0.75], there are 2 or 3 capacitors discharged at the same time, as shown in Fig. 3c. In addition, when the reference signal is in the interval of [0.75, 1], there are 3 or 4 capacitors discharged at the same time, as shown in Fig. 3d. Therefore, whatever the value of the reference signal, four capacitors can take turns discharging, and the discharge times of all the capacitors are equal. As a result, each of the capacitors output the same energy, and voltage balance of capacitors is achieved under the carrier frequency. The number of voltage level changes when the modulation ratio M1 changes, and the capacitor voltages are always balanced. Compared with voltage balance strategies under the modulation frequency, the voltage balance strategy proposed in this paper has a smaller voltage ripple and a more stabilized voltage value. Thus, the quality of the output waveform is better.

When the proposed inverter operates in the five-level mode, the dc side switches (S1, S2, S7, S8) are kept on, and the bidirectional switch S0 is kept off. Then the topology of the proposed inverter changes into a cascaded H-bridge inverter.

The modulation strategy of the five-level mode of the proposed inverter is shown in Fig. 4a. Four carriers (Tri1, Tri3, Tri5, Tri7) and one reference signal (Tref) are required to generate original waveforms. The phase difference between adjacent carriers is 180°. Four sets of rectangular pulse signals are obtained by comparing the carriers and the reference signal, to control the bridge arm switches (S3–S6, S9–S12).

When the proposed inverter operates in the three-level mode, only four bridge arm switches (S3, S5, S10, S12,) participate in the modulation process. In addition, the topology changes into a three-level H-bridge inverter.

The modulation strategy of the three-level mode of the proposed inverter is shown in Fig. 4b. Two carriers (Tri1, Tri5,) and one reference signal (Tref) are required to generate original waveforms. Two sets of rectangular pulse signals are obtained by comparing the carriers and the reference signal, to control bridge arm switches (S3, S5, S10, S12).

3 Calculations and analysis of losses and current THD

As can be seen from the analysis in Sect. 2, the quality of output waveforms and the losses are quite different when the proposed inverter operates in different modes. In this section, the total losses and current THD of the proposed inverter are calculated and compared under the three modes.

3.1 Calculations of losses

The inverter losses mainly include the conduction losses, the switching losses and the losses of the filter inductor. Since a multilevel inverter has an advantage in terms of reducing the filter inductor, the losses of the inductor are ignored in this paper.

The conduction losses of the proposed inverter are derived first. The conduction losses of one MOSFET device can be approximately calculated as:

where UM is the conduction voltage drop of the MOSFET (V); RM is conduction resistance (Ω); and I is the current (A), which can be expressed as: I = Im*sin ωt.

Similarly, the conduction losses of one diode can be approximately calculated as:

where UD is conduction voltage drop of the diode (V); and RD is the conduction resistance of the diode (Ω).

The losses of the proposed inverter under the nine-level mode are analyzed first. The number of output levels changes as the modulation radio M1 varies from 0 to 1. When M1 ∈[0.75, 1], the inverter can output a nine-level voltage wave. Since the output waveforms of the inverter have periodic symmetry, the output characteristic can be analyzed in the interval of [0, π/2]. Depending on the voltage of a waveform, three angles are defined to differentiate the output voltage intervals. In a modulation cycle, when the voltage level reaches Udc/2 for the first time, the corresponding angle is defined as θ1. The definitions of θ2 and θ3 are similar to that of θ1. The three angles are defined as:

In the above four intervals, the duty cycles of the switches are different. The duty cycles D11–D14 in the four intervals are expressed as:

Moreover, in the four intervals above, the conduction losses are different when the inverter output voltage changes. To calculate the conduction losses, the number of conductive switch devices with different output voltages is analyzed, as shown in Table 1.

According to (1), (2), (4) and Table 1, the conduction losses of a MOSFET in the nine-level mode (Pcon_M9) and the conduction losses of a clamp diode in the nine-level mode (Pcon_D9) can be obtained as:

Then the switching losses in the nine-level mode are calculated. The switching losses are caused by the non-ideal state of the switch device. It takes time for the switch device to go from fully on to fully off, and this process produces losses. The switching loss of one MOSFET in a single switch motion can be calculated as:

where Es is the energy of the switching loss of one switch motion (J); VD is the voltage stress of the switch (V); ID is the conduction current of the switch (A); and tS(on) and tS(off) are the on delay time and the off delay time of the switch (s).

When the proposed inverter operates in the nine-level mode, there are 12 switches participate in modulation. S1, S2, S7, S8 operate at the carrier frequency in one cycle. The bridge arm switches act only one time in one cycle, and can be ignored. The total switching losses can be obtained by summing the losses of all the switches.

where, Psw_9 is power of the switching losses (W); T is the modulation period (s); fs is the motion frequency of one switch (Hz); and fc is the carrier frequency (Hz).

To sum up (5), (6), (8), the total losses of the inverter in the 9-level mode is:

Similarly, the losses of the proposed inverter under the five-level mode is calculated. The conduction losses of the MOSFET (Pcon_M5) and the conduction losses of the antiparallel diode (Pcon_D5) can be expressed as:

The total switching losses in the five-level mode can be expressed as:

To sum up (10), (11), (12), the total losses of the inverter in the five-level mode is:

The losses of the proposed inverter under the three-level mode are calculated as follows. The conduction losses of the MOSFET (Pcon_M3) and the conduction losses of the antiparallel diode (Pcon_D3) can be expressed as:

The total switching losses under the three-level mode can be expressed as:

To sum up (14), (15), (16), the total losses of the inverter in the three-level mode is:

To analyze and compare the losses under different modes, specific data was substituted into the equations and a function diagram was obtained, as shown in Fig. 5. To simplify the calculations, the parameters of the antiparallel diode and the clamping diode are the same. The parameters used in the calculation are shown in Table 2.

As can be seen from Fig. 5, the total losses increase with an increase of the current. When the current is the same, the losses of the nine-level mode are the largest, and the losses of the three-level mode are the lowest. The larger the current is, the more obvious the difference is. An increase of the level number leads to an increase of the losses.

3.2 Calculations of current THD

Total harmonic distortion (THD) plays an important role in the detection and evaluation of a power system. It is an important index to evaluate the characteristics of an inverter. It is not easy to calculate the current THD by its definition. However, the output current of an inverter can be seen as a combination of the current fundamental wave and the current ripple. Therefore, the current ripple can be approximately regarded as the sum of harmonic currents. Thus, the current THD is approximately expressed by the ratio of the current ripple to the fundamental wave as:

where ∆IRMS is the RMS value of the current ripple (A); ∆Im is the peak–peak value of the current ripple wave (A); and IM is the peak value of the output current fundamental wave (A).

When the proposed inverter operates in the nine-level mode, the current ripple in different intervals is calculated first. Following the rules in Sect. 2.1, interval [0, π/2] is divided into four parts. Thus, the peak–peak values of the current ripple in the four intervals are:

RMS values of the current ripple are obtained by integrating the peak–peak values of the current ripple in the four intervals. Thus, the RMS values of the current ripple in the nine-level mode are expressed as:

Hence, the current THD of the proposed inverter in the nine-level mode is obtained as:

Similarly, when the inverter operates in the five-level mode, the interval [0, π/2] is divided into two parts. In addition, the peak–peak value of the current ripple in the two intervals are:

The RMS value of the current ripple in the five-level mode can be obtained as:

Thus, the current THD of the proposed inverter in the five-level mode is expressed as:

In a similar way, when the inverter operates in the three-level mode, the peak–peak value of the current ripple in the interval [0, π/2] is:

The RMS values of the current ripple in the three-level mode is calculated as:

The current THD of the proposed inverter in the five-level mode is expressed as:

To intuitively analyze the difference of the current THD in the three modes, specific data was substituted into the above equations. Take a grid-connected application as an example, ‘Uout’ in (19), (22) and (25) is replaced with ‘Em sinωt’, and its value is 311 V. For comparison purposes, Udc in both the nine-level mode and the five-level mode is 200 V; and Udc in the three-level mode is 400 V. The other parameters used in the calculations are shown in Table 2. Figure 6 shows different current THDs under the three operation modes. As can be seen from Fig. 6, the current THD decreases along with the increase of the current. When the current is the same, the current THD of the nine-level mode is the lowest, and that of the three-level mode is the highest.

4 Simulation and experimental results

4.1 Simulation results

To verify the correctness and feasibility of the proposed inverter, simulation models are established on a MATLAB/Simulink platform. The parameters used in the simulations are shown in Table 3.

The steady-state performance of the inverter under each mode was simulated first. The proposed inverter has three modes. Simulation results of the nine-level mode are shown in Fig. 7. Figure 7b shows the current waveform with a 25 Ω resistive load and an 18mH inductive load. It can be seen from Fig. 7 that the inverter can output a nine-level voltage waveform with a frequency of 50 Hz as required.

Simulation results of the five-level mode are shown in Fig. 8. Figure 8b shows the output current with the same load as the nine-level mode. The inverter can output a five-level voltage waveform and the switching frequency of the output voltage is halved when compared with Fig. 7a.

Simulation results of the three-level mode are shown in Fig. 9. Comparing the above three simulation results, the quality of the output current under the nine-level mode is the best, and the quality of the output current under the three-level mode is the worst. Simulation results can confirm the theoretical analysis in this paper.

When the inverter works in the nine-level mode, the capacitor voltage must be balanced. Figure 10 shows the voltage waveforms of the four capacitors. The obtained simulation results indicate that the voltages of the four capacitors are well balanced under the modulation strategy proposed in this paper.

The dynamic performance of the proposed inverter was also simulated. Figure 11 shows the simulation results of the online transition process with different modes. With the given control signals at 0.3 s and 0.6 s, the inverter changes from the nine-level mode to the five-level mode at 0.3 s, and from the five-level mode to the three-level mode at 0.6 s. The output waveform is correct and good during the transition process.

Simulation results of THD corresponding to different currents are obtained by an FFT analysis. In addition, simulation results of the current THD curve are obtained, as shown in Fig. 12. The colored points are simulation values of different currents. By comparing the THD simulation results with the THD calculation results in Fig. 6, it can be seen that the simulation results are in accord with the calculation curves, which verifies the correctness of calculations in this paper.

4.2 Experimental results

An experimental platform was implemented to further validate the proposed inverter and its modulation strategy. The parameters in the experiment are the same as those used in the simulation, as shown in Table 3.

Firstly, the steady-state performance of the inverter was tested. Experiments of the inverter working in different modes were conducted, and output voltage and current waveforms were observed. Figure 13 shows signal waveforms of twelve switches in the nine-level mode. It can be seen from this figure that the four dc side switches work at a high frequency and the eight bridge arm switches work at a low frequency. The obtained experimental signals are consistent with modulation signals.

Figure 14 shows output voltage waveforms and current waveforms of the proposed inverter in the nine-level mode. Figure 14a shows output waveforms with a 60 Ω resistive load, and Fig. 14b shows output waveforms with a 25 Ω resistive load and an 18mH inductive load.

Figure 15 shows dc side capacitor voltage waveforms when the inverter works in the nine-level mode. It can be seen from this figure that the voltage of each capacitor is half of the dc side voltage. The voltage values are stable and the voltage ripple is small. This shows that the voltage balance strategy in this paper is effective.

Figure 16 shows switching signal waveforms of the five-level mode. As can be seen, eight switches participated in the modulation. The obtained experimental switching signals are consistent with the modulation signals.

Figure 17 shows output voltage waveforms and current waveforms of the proposed inverter in the five-level mode. Figure 17a shows output waveforms with a 60 Ω resistive load, and Fig. 17b shows output waveforms with a 25 Ω resistive load and an 18 mH inductive load.

Figure 18 shows switching signal waveforms of the three-level mode. Four bridge arm switches participated in the modulation. The obtained experimental switching signals are consistent with the modulation signals.

Figure 19 shows output voltage waveforms and current waveforms of the proposed inverter in the five-level mode. Figure 19a shows waveforms with a 60 Ω resistive load, and Fig. 19b shows waveforms with a 25 Ω resistive load and an 18mH inductive load. It can be observed from Figs. 14, 17 and 19 that the inverter has the best output characteristics under the nine-level mode, and that the voltage waveform has the highest switching frequency. With the same load, the output characteristics under the three-level mode are the worst. The obtained voltage waveform has a lower switching frequency. These experimental results are consistent with the theoretical analysis and simulation results in this paper.

Then the dynamic performance of the proposed inverter was tested. The inverter changes its working modes online by given control signals. Figure 20 shows experimental results of an online transition between the different modes of the inverter.

In Fig. 20a, the inverter changes from the nine-level mode to the five-level mode, and t1 is the moment to give a switch signal. In Fig. 20b, the inverter changes from the five-level mode to the three-level mode, and t2 is the moment to give a switch signal. Since the circuit structure changes from cascade to parallel, the output voltage of the three-level mode is halved. The obtained experimental results are in agreement with simulation results. It can be seen from these results that the working modes can switchover online and that the output waveforms is good during the transition process.

5 Conclusions

To achieve a wide operational range and to reduce the power losses, a flexible cascaded multilevel inverter is proposed in this paper. According to the actual working conditions, the inverter can change its topology structure to work in three modes. The proposed inverter can reduce the number of active switch devices to decrease the inverter losses in the three-level mode. In addition, the inverter can provide more output levels to improve the quality of its output waveforms in the nine-level mode. Furthermore, its modulation strategies and voltage balance method were analyzed. Simulations and experiments were conducted. The obtained results indicate that the topology and modulation strategy of the inverter are correct and valid. In addition, the online transition process between the different modes is effective and favorable. The proposed inverter can achieve a wide operational range and decreased total losses.

References

Wandhare, R.G., Agarwal, V.: Novel integration of a PV-wind energy system with enhanced efficiency. IEEE Trans. Power Electron. 30(7), 3638–3649 (2015)

Hannan, M.A., Ghani, Z.A., Hoque, M.M., Ker, P.J., Hussain, A., Mohamed, A.: Fuzzy logic inverter controller in photovoltaic applications: issues and recommendations. IEEE Access 7, 24934–24955 (2019)

Agrawal, R., Jain, S.: Multilevel inverter for interfacing renewable energy sources with low/medium- and high-voltage grids. In: IET Renewable Power Generation, vol. 11, No. 14, pp. 1822–1831 (2017)

Zhang, X., Zhao, T., Mao, W., Tan, D., Chang, L.: Multilevel inverters for grid-connected photovoltaic applications: examining emerging trends. IEEE Power Electron. Mag. 5(4), 32–41 (2018)

Amamra, S., Meghriche, K., Cherifi, A., Francois, B.: Multilevel inverter topology for renewable energy grid integration. IEEE Trans. Ind. Electron. 64(11), 8855–8866 (2017)

Sandeep, N., Yaragatti, U.R.: Operation and control of a nine-level modified ANPC inverter topology with reduced part count for grid-connected applications. IEEE Trans. Ind. Electron. 65(6), 4810–4818 (2018)

Hasan, M.M., Abu-Siada, A., Dahidah, M.S.A.: A three-phase symmetrical DC-link multilevel inverter with reduced number of DC sources. IEEE Trans. Power Electron. 33(10), 8331–8340 (2018)

Shuvo, S., Hossain, E., Islam, T., Akib, A., Padmanaban, S., Khan, M.Z.R.: Design and hardware implementation considerations of modified multilevel cascaded H-bridge inverter for photovoltaic system. IEEE Access 7, 16504–16524 (2019)

Zhang, Y., Li, J., Li, X., Cao, Y., Sumner, M., Xia, C.: A Method for the suppression of fluctuations in the neutral-point potential of a three-level NPC inverter with a capacitor-voltage loop. IEEE Trans. Power Electron. 32(1), 825–836 (2017)

Zhou, L., Gao, F., Xu, T.: A family of neutral-point-clamped circuits of single-phase PV inverters: generalized principle and implementation. IEEE Trans. Power Electron. 32(6), 4307–4319 (2017)

Wang, W., Zhang, B., Xie, F.: A novel SVPWM for three-level NPC inverter based on m-mode controllability. IEEE Trans. Ind. Electron. 65(8), 6055–6065 (2018)

Sadigh, A.K., Dargahi, V., Corzine, K.A.: analytical determination of conduction and switching power losses in flying-capacitor-based active neutral-point-clamped multilevel converter. IEEE Trans. Power Electron. 31(8), 5473–5494 (2016)

Ghias, A.M.Y.M., Pou, J., Capella, G.J., Agelidis, V.G., Aguilera, R.P., Meynard, T.: Single-carrier phase-disposition PWM implementation for multilevel flying capacitor converters. IEEE Trans. Power Electron. 30(10), 5376–5380 (2015)

Zhou, Y., Li, H.: Analysis and suppression of leakage current in cascaded-multilevel-inverter-based PV systems. IEEE Trans. Power Electron. 29(10), 5265–5277 (2014)

McGrath, B.P., Holmes, D.G., Kong, W.Y.: A decentralized controller architecture for a cascaded H-bridge multilevel converter. IEEE Trans. Ind. Electron. 61(3), 1169–1178 (2014)

Yu, Y., Konstantinou, G., Hredzak, B., Agelidis, V.G.: Operation of cascaded H-bridge multilevel converters for large-scale photovoltaic power plants under bridge failures. IEEE Trans. Ind. Electron. 62(11), 7228–7236 (2015)

Gupta, K.K., Ranjan, A., Bhatnagar, P., Sahu, L.K., Jain, S.: Multilevel Inverter topologies with reduced device count: a review. IEEE Trans. Power Electron. 31(1), 135–151 (2016)

Storey, J., Wilson, P.R., Bagnall, D.: The optimized-string dynamic photovoltaic array. IEEE Trans. Power Electron. 29(4), 1768–1776 (2014)

Zhang, L., Sun, K., Hu, H., Xing, Y.: A system-level control strategy of photovoltaic grid-tied generation systems for european efficiency enhancement. IEEE Trans. Power Electron. 29(7), 3445–3453 (2014)

Kim, Y., Ji, Y., Kim, J., Jung, Y., Won, C.: A new control strategy for improving weighted efficiency in photovoltaic AC module-type interleaved flyback inverters. IEEE Trans. Power Electron. 28(6), 2688–2699 (2013)

Nousiainen, L., et al.: photovoltaic generator as an input source for power electronic converters. IEEE Trans. Power Electron. 28(6), 3028–3038 (2013)

LaBella, T., Yu, W., Lai, J., Senesky, M., Anderson, D.: A bidirectional-switch-based wide-input range high-efficiency isolated resonant converter for photovoltaic applications. IEEE Trans. Power Electron. 29(7), 3473–3484 (2014)

Qin, S., Cady, S.T., Domínguez-García, A.D., Pilawa-Podgurski, R.C.N.: A distributed approach to maximum power point tracking for photovoltaic submodule differential power processing. IEEE Trans. Power Electron. 30(4), 2024–2040 (2015)

Valderrama, G.E., Guzman, G.V., Pool-Mazún, E.I., Martinez-Rodriguez, P.R., Lopez-Sanchez, M.J., Zuñiga, J.M.S.: A single-phase asymmetrical T-type five-level transformerless PV inverter. IEEE J. Emerg. Sel. Top. Power Electron. 6(1), 140–150 (2018)

Rani, I.S., Trinadh, M.: Single-phase nine-level grid-connected inverter for photo-voltaic system. In: 2016 International Conference on Electrical, Electronics, and Optimization Techniques (ICEEOT), Chennai, pp. 4106–4110 (2016)

Hinago, Y., Koizumi, H.: A single-phase multilevel inverter using switched series/parallel DC voltage sources. IEEE Trans. Ind. Electron. 57(8), 2643–2650 (2010)

He, L., Cheng, C.: A flying-capacitor-clamped five-level inverter based on bridge modular switched-capacitor topology. IEEE Trans. Ind. Electron. 63(12), 7814–7822 (2016)

Shen, J., Jou, H., Wu, J., Wu, K.: Five-Level inverter for renewable power generation system. IEEE Trans. Energy Convers. 28(2), 257–266 (2013)

Acknowledgements

This work was supported in part by the National Natural Science Foundation of China under Grant 51507155, in part by the Youth key Teacher Project of the Provincial Higher Educational Institution of Henan under Grant 2019GGJS011, and in part by the Graduate Education Research Project of Zhengzhou University under Grant YJSJY201964.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Wang, Y., Du, G., Liang, J. et al. Flexible cascaded multilevel inverter with multiple operation modes. J. Power Electron. 20, 675–686 (2020). https://doi.org/10.1007/s43236-020-00060-4

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s43236-020-00060-4