Abstract

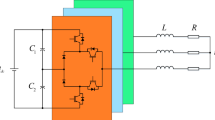

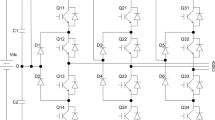

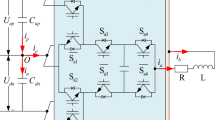

Neutral-point potential unbalancing is an inherent disadvantage of NPC three-level inverter. Traditional control methods, e.g. the space vector PWM (SVPWM) considering balance factor or the model predictive control (MPC), usually needs large amounts of calculation and the common-mode voltage usually keeps large due to the zero vectors being involved in the modulation or the roll optimization. Aiming at above problems, this paper proposes a simplified model predictive algorithm based on the characteristics analysis on the unbalancing and common-mode voltage. Firstly, an approximate two-level structure containing 12 vectors is proposed by the reduced-order processing for the three-level structure, which solves the calculation complexity problem. Meanwhile, multi-constraints including switching frequency, neutral-point potential deviation and the common-mode voltage, are constructed within the roll optimization items of the MPC scheme to make common-mode voltage being restricted less than 1/6 DC voltage while the switching frequency is almost constant. Finally, experiments were carried out to verify that this method can realize a neutral-point voltage balance and a low common-mode voltage along with less execution time.

Similar content being viewed by others

References

Abari I, Lahouar A, Hamouda M et al (2018) Fault detection methods for three-level NPC inverter based on DC-bus electromagnetic signatures. IEEE Trans Ind Electron 65(7):5224–5236

Rodriguez J, Bernet S, Steimer PK (2010) A survey on neutral point clamped inverters. IEEE Trans Ind Electron 57(7):2219–2230

Gang L et al (2018) Neutral-point voltage balancing in three-level inverters using an optimized virtual space vector PWM with reduced commutations. IEEE Trans Ind Electron 65(9):6959–6969

Lee JS, Lee KB (2016) Time-offset injection method for neutral-point AC ripple voltage reduction in a three-level inverter. IEEE Trans Power Electron 31(3):1931–1941

Lyu J, Hu W, Wu F et al (2015) Variable modulation offset SPWM control to balance the neutral-point voltage for three-level inverters. IEEE Trans Power Electron 30(12):7181–7192

Xiang CQ, Shu C, Han D et al (2018) Improved virtual space vector modulation for three-level neutral-point-clamped converter with feedback of neutral-point voltage. IEEE Trans Power Electron 33(6):5452–5464

Tsai M-J, Chen H-C, Tsai M-R et al (2018) Evaluation of carrier-based modulation techniques with common-mode voltage reduction for neutral point clamped converter. IEEE Trans Power Electron 33(4):3268–3275

Xiang W, Tan G, Ye Z et al (2018) Virtual-space-vector PWM for a three-level neutral-point-clamped inverter with unbalanced DC-links. IEEE Trans Power Electron 33(3):2630–2642

Pratheesh KJ, Jagadanand G, Ramchand R (2018) A generalized-switch-matrix-based space vector modulation technique using the nearest level modulation concept for neutral-point-clamped multilevel inverters. IEEE Trans Ind Electron 65(6):4542–4552

Qiang S, Wenhua L, Qingguang Y, Xiaorong X et al (2003) A neutral-point potential balancing algorithm for three-level NPC inverters using analytically injected zero-sequence voltage. In: Proceedings of IEEE applied power electronics conference, Miami Beach, Feb 2003, pp 228–233

Xi YG, Li DW, Lin S (2013) Model predictive control-status and challenges. Acta Autom Sin 29(3):222–236

Gong Z, Xiaojie W, Dai P et al (2019) Modulated model predictive control for MMC-based active front-end rectifiers under unbalanced grid conditions. IEEE Trans Ind Electron 66(3):2398–2409

Perez MA, Rodriguez J, Fuentes EJ et al (2012) Predictive control of ac–ac modular multilevel converters. IEEE Trans Ind Electron 59(7):2832–2839

Hou C-C, Shih C-C, Cheng P-T et al (2013) Common-mode voltage reduction pulse width modulation techniques for three-phase grid-connected converters. IEEE Trans Power Electron 28(4):1971–1979

Kai L, Zhao J, Wenjie W et al (2016) Performance analysis of zero common-mode voltage pulse-width modulation techniques for three-level neutral point clamped inverters. IET Power Electron 9(14):2654–2664

Yuen KF, Chung SH, Cheung VS (2012) An active low-loss motor terminal filter for over voltage suppression and common-mode current reduction. IEEE Trans Power Electron 27(7):3158–3172

Nguyen N-V, Nguyen T-KT, Hong-Hee L (2015) A reduced switching loss PWM strategy to eliminate common mode voltage in multilevel inverters. IEEE Trans Power Electron 30(10):5425–5438

Nguyen T-KT, Nguyen N-V, Prasad NR (2016) Eliminated common mode voltage pulse-width modulation to reduce output current ripple for multilevel inverters. IEEE Trans Power Electron 31(8):5952–5966

Jiang D, Shen Z, Wang F (2018) Common-mode voltage reduction for paralleled inverters. IEEE Trans Power Electron 33(5):3961–3974

Nguyen T-K, Nguyen N-V (2018) An efficient four-state zero common-mode voltage PWM scheme with reduced current distortion for a three-level inverter. IEEE Trans Ind Electron 65(2):1021–1030

Vu H-C, Nguyen TD, Chun T-W et al (2017) New virtual space vector modulation scheme to eliminate common-mode voltage with balanced neutral-point voltage for three-level NPC inverters. In: 2017 IEEE 3rd international future energy electronics conference and ECCE Asia, Asia, Jul 2017, pp 311–318

Alawieh H, Arab Tehrani K, Azzouz Y et al (2014) A new active common-mode voltage elimination method for three-level neutral-point clamped inverters. In: Annual conference of the IEEE industrial electronics society, pp 1060–1066, Dallas, Nov 2014

Funding

Funding was provided by Shanghai Sailing Program (CN) (Grant no. 18YF1418300) and Key Laboratory of Control Power Transmission and Conversion (SJTU CN) (Grant no. 2016AC04).

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Yuan, Q., Qian, J. & Li, A. A Simplified Common-Mode Voltage Suppression and Neutral-Point Potential Control for the NPC Three-Level Inverter. J. Electr. Eng. Technol. 14, 2389–2398 (2019). https://doi.org/10.1007/s42835-019-00293-9

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s42835-019-00293-9