Abstract

In this work, the electrical property of Au/graphene oxide/p-InP hetero-structure has been evaluated by I–V and C–V measurements in dark and illuminated conditions (visible light). The diode exhibited significant rectifying behavior, thus indicating the heterojunction-type diode. The key electrical parameters of heterojunction diode including ideality factor (n), series resistance (Rs), shunt resistance (Rsh), and barrier height (Фb) are estimated from I–V data based on the theory of thermionic emission. The modified Norde and Cheung’s methods were utilized to evaluate the electrical parameters and compared the results. The current conduction mechanism at different voltage regions of I–V has also been investigated. The variation of 1/C2 versus voltage signifies linearity at high frequency (1 MHz), indicating that the type of heterojunction can be abrupt. The experimental outcomes of this study revealed that the performance of heterojunction diode in dark is considerably good as compared to the illumination condition with respect to the lower values of Фb, n, Rs, and interface state density (Nss).

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Owing to the intriguing properties of III–V semiconductors, in particular, indium phosphide (InP) is a kind of prominent semiconductor material and extensively employed in the development of optoelectronic and microwave devices [1, 2]. It has numerous applications including metal/insulator/semiconductor field effect transistors, photodetectors, solar cells, microwave sources, and amplifiers [3,4,5,6,7]. In addition, InP has great potential for radiation resistance in comparison to other semiconductor materials like GaAs [8] and Si [9], which makes it a promising candidate in telecommunication applications, especially optical generation, switching, and detection components. In the meantime, InP-based Schottky junctions suffer low Schottky barrier height, which will cause a huge leakage current and degenerate the performance of the devices resulting from the high surface state density and other nonstoichiometric defects [10]. The inserted layer of high conductive oxide material can act as a blockade of inter-diffusion, which can not only decrease the existing surface state density, leakage current, and series resistance, but also improve the shunt resistance and rectification ratio. Meanwhile, the inserted layer isolates metal from the semiconductor and hence hinders the inter-diffusion and reaction among them. Benefiting from these advantages, the metal/insulator/semiconductor (MIS) structure devices have emerged with excellent potential in a wide variety of applications, especially in optoelectronic and high-frequency devices owing to their easy and low-cost processing, better performance, flexibility, and low energy consumption. Therefore, in this regard, the in-depth knowledge of the rectification behavior characteristics of metal/insulator/InP structure would help to accelerate the development of the emerging potential applications.

There are only a few reported studies in open literature on the tuning of the Schottky barrier properties of metal/bulk InP contact by inserting a very thin interfacial layer between the M/S interface by different research groups [11,12,13,14,15,16,17,18,19,20,21]. Lin et al. [16] have prepared the MoS2/p-InP heterojunction diode by chemical vapor deposition. The BH, ideality factor, and Rs values extracted from forward bias J–V characteristics are 0.73 eV, 2.4, and 12.8 Ω respectively. Chen et al. [17] reported the Al/MoO3/p-InP MIS Schottky barrier diode and measured its electrical parameters with temperatures from 310 to 400 K. Reddy et al. [18] demonstrated that effective improvement could be attributed to the modification of Ti/p-type InP interface by inclusion of a polyvinylpyrrolidone (PVP) polymer interlayer. Recently, Acar et al. [21] fabricated the Au/ZnO/p-InP metal/oxide/semiconductor structure by using RF magnetron sputtering technique, and they found the density of interface states of this structure is from 8.18 × 1013 to 1.24 × 1011 eV−1 cm−2 with a change of frequency.

In recent years, an interesting layered material, graphene oxide (GO), has attracted many researchers’ attention in a variety of applications due to its exceptional electrical, mechanical, and optical properties, which makes it one of the potential candidates in emerging electronics and optoelectronics. Currently, graphene/bulk semiconductor-based hybrid heterojunction has emerged in versatile diverse applications, such as solar cells, photodetectors, sensors, and Schottky junctions [22]. To date, many research groups have been devoted to constructing graphene-based hybrid heterostructures to modify or improve their performance with various bulk semiconductors such as GaAs [23], SiC [24, 25], AlGaN [26, 27], GaN [28,29,30,31], Ge [32, 33], and Si [34,35,36,37,38,39], whereas only a little work [40,41,42] had been reported on InP. Phan et al. [43] have explored the photoelectrical performance of Al/GO/n-Si/Al Schottky diode and revealed that the photocurrent increases while the light intensity increases, where the nanoscale GO film acts as a semiconductor with high photoconductivity. Kalita et al. [44] analyzed the photovoltaic properties of Au/pr-GO/n-Si Schottky diode in dark and illuminated conditions. The J–V characteristics of the diode show good rectification and the leakage current is small under reverse bias in dark conditions. Yang et al. [45] have introduced a GO interlayer into Gr/Si solar cells and found that the performance of Gr/GO/Si structure was significantly more stable than that without a GO interlayer, and the maximum power conversion efficiency with GO is about 6.18%. Gullu et al. [42] prepared a Al/GO/n-InP heterojunction, where the MIS structure achieved higher barrier height (0.85 eV) with GO of about 100% compared with the value (0.43 eV) of the MS diode without a GO interlayer. However, there were no reports on heterojunction diode fabrication using graphene oxide (GO) Schottky contact on p-type InP with a detailed electrical characterization. Therefore, in this context, a thin graphene oxide film was used as an interlayer at the metal/semiconductor interface and the properties of the heterojunction were investigated under dark and illuminated conditions. It has been discovered that a thin inserted layer in the interface can be wiped out to enhance the interfacial properties and influence the quality and performance of the device. To validate the above arguments, we have fabricated the Au/GO/p-InP heterojunction and determined its electrical and photoelectrical properties. Moreover, the main electrical parameters under dark and illuminated conditions were also evaluated, compared, and discussed in detail.

2 Experimental details

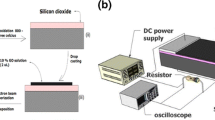

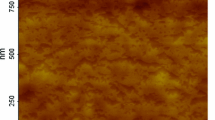

A cleaned p-type (100) InP (Zn-doped, 0.5 Ω cm) with 350-μm thickness (given by the manufacturer) was taken for the fabrication of the device. First, the wafer was treated by trichloroethylene, acetone, and methanol with ultrasound. Then the degreased wafer was dipped in a mixture of H2SO4, H2O2, and H2O (5:1:1) for 1 min to clean the surface. After that, the wafer was treated with diluted HF (10%) solution to etch the oxide layer. Subsequently, DI water was used to clean the wafers, which dried under the flow of high-purity N2 gas and then were immediately transferred into the deposition chamber. Pt film (30 nm, 99.99%) was deposited by electron beam evaporation and annealed at 350 °C for 1 min in N2 atmosphere to attain good conductive contact. Initially, the graphene oxide powder (purchased from XF Nano) was dissolved in water for 12 h by ultrasonic agitation to achieve the homogeneous GO solution. Then, using the drop casting method, the GO layer was obtained on the front side of the substrate (see in Fig. 1a) and the sample was baked at 50 °C. The thickness of GO was measured by a stylus profiler and the value was about 40 nm, which was obtained from the difference between the average height of the upper surface and the average height of the lower surface, so no repeated measurements were made. The preparation process and the schematic illustration of Au/GO/p-InP heterojunction structure are given in Fig. 1a, b. In addition, AFM was adopted to evaluate the surface quality before and after depositing the GO layer and is depicted in Fig. 2. The images show the continuous GO film, which works as the interlayer between the metal and the semiconductor. Eventually, Au circular dots with 30 ± 1 nm thickness and 0.7 ± 0.0075 mm diameter were deposited through a stainless-steel mask.

The I–V and C–V data of Au/GO/p-InP heterojunction were recorded by semiconductor device analyzer (Keysight B1500A) in dark and illuminated conditions. The illumination was carried out by a general commercial lamp with a power density of 30 mW/cm2. As well, the capacitance frequency (C–f) characteristics were also evaluated using a Keysight B1500A device. In addition, SEM was also used to evaluate the surface of the GO/p-InP structure as depicted in Fig. 2c.

3 Results and discussion

The I–V behavior of the Au/GO/p-InP heterojunction is measured in dark and illuminated conditions, respectively. As shown in Fig. 3, the Au/GO/p-InP heterojunction has exhibited a good rectifying behavior, while the ratios of the forward current and reverse current (IF/IR) in dark and illuminated conditions are (9.66 ± 0.01) × 10−2 and (5.14 ± 0.01) × 10−3 at 3 V, respectively. The measured reverse leakage currents are found to be (5.6812 ± 0.0001) × 10−8 A at 1 V in the dark and (4.1393 ± 0.0001) × 10−7 A at 1 V under illuminated conditions, respectively. Based on the TE theory, the current is [46],

where V is voltage, IRS is the voltage drop across the RS, kB is Boltzmann’s constant (1.3806 × 10−23 J/K), T is absolute temperature in Kelvin, q is the charge of electron (1.602 × 10−19 C), and Io is the saturation current.

where A is active area, A* is effective Richardson constant for p-InP (60 A cm−2 K−2), Фb is Schottky barrier height. From Eqs. (1) and (2), the ideality factor and barrier height can be rearranged as

and

To investigate, the V < 3kT regime, in dark and under illumination, the saturation current (Io) is derived from semilog reverse-bias I–V plots as shown in Fig. 4. Using Eq. (2), very small saturation current (Io) values of 5.94 × 10−11 A and 2.44 × 10−10 A can be acquired in dark and under illumination, respectively. The barrier heights of Au/GO/p-InP heterojunction could be obtained through the saturation current density (Io) in dark and under illumination. The ideality factor and barrier height of the Au/GO/p-InP heterojunction are estimated to be 1.67 and 0.87 eV in the dark and 1.81 and 0.83 eV in light conditions at room temperature, respectively. A summary of these experimental results is provided in Table 1. It can be observed that the differences in Фb obtained in dark and illuminated conditions were due to the device illumination at 30 mW/cm2 light and extra free charge carriers (electron–hole pairs) occurred in the devices. Now, these carrier movements cause an increase in the current in the reverse region depending on the illumination [47]. Usually, the expected value of the ideal factor should be close to unity, but as seen from Table 1, the obtained ideality factor is greater than 1, thus exhibiting the deviations from the ideal contact. This may origin from various factors, like different fitting procedures for data analysis, leakage current, series resistance, interface states, as well as the tunneling process [48,49,50,51].

Normally, an ideal Schottky diode exhibits low series resistance (Rs) that allows high current through the device, and large shunt resistance (Rsh) for small leakage current [46], which has affected the logI–V characteristics of the diode. In order to evaluate the value of Rs and Rsh, a plot of junction resistance (Rj) of the Au/GO/p-InP heterojunction diode was potted in Fig. 5. The estimated Rs and Rsh are 1209 Ω and 120 MΩ under darkness, 680 Ω and 10 MΩ under illumination, respectively. As shown in Table 1, the Au/GO/p-InP heterostructure has low Rs and high Rsh, thus indicating that the heterojunction is structure suitable for the potential applications.

As a result of the combined effects, the log(I)–V plots of Au/GO/p-InP heterojunction deviate at high currents (as shown in Fig. 3). In this context, the estimated value of Rs, Фb and n can be deduced using the well-known Cheung’s functions [52] as below:

and H(I) is given by

Figure 6 describes dV/d(lnI) and H(I) of the heterojunction in the dark and under illumination, respectively. Using the linear regression line of dV/d(lnI)–I plot, the parameters Rs and nkT/q can be deduced from the slope and intercept, respectively. From dV/d(lnI)–V plot, Rs and n were found to be 367 Ω and 1.86 in the dark, 268 Ω and 1.97 under illuminated condition, respectively. From H(I)–V plot, the Rs and Фb values are estimated to be 829 Ω, 0.93 eV in the dark and 599 Ω, 0.84 eV under illumination conditions respectively. The estimated values were also presented in Table 1. The experimental results indicate that the Rs values attained by the two equations are well in concurrence with each other, conforming their consistency and validity. It is also observed from Table 1, that the Фb and n deviate considerably with those results from the log(I)–V measurement. This deviation is due to the employed methods to estimate the Фb and n in various regions of log(I)–V data.

A well-known modified Norde method was also utilized to evaluate Au/GO/p-InP heterojunction diode for the comparison. From this method, the values of Фb and Rs are estimated from log(I)–V data using modified Norde method [53] as given below:

where γ is a (dimensionless) integer greater than the ideality factor (n), and I(V) is the current obtained from the log(I)–V curve. F(V)–V is plotted using Eq. (8) for the Au/GO/p-InP heterojunction as shown in Fig. 7a and b. The effective Фb can be derived by:

where F(Vmin) is the minimum value of F(V) corresponding to the minimum voltage Vmin, which are attained from the F(V)–V plot (Fig. 7). Similarly, the series resistance RS is obtained by using the following equation:

where n is the ideality factor, Imin is the current minimum corresponding to the minimum point of F(Vmin), the estimated values of Rs and Фb are 2572 kΩ, 0.88 eV in dark, and 1.457 kΩ, 0.84 eV under illumination for the Au/GO/p-InP heterojunction diode, respectively. These results clearly confirm the similarity of the barrier height (Фb) values obtained from Cheung’s and Norde methods, as well as high reliability and efficiency of these techniques. Meanwhile, Rs values obtained from the two methods have some discrepancy, because different regions of log(I)–V data were used in these applied methods. The estimated values of Фb and Rs are given in Table 1.

In general, considering the native oxide layer, the current through the Schottky junction can be estimated by [3].

Besides, if surface potential Ψsurf(Ic, Vc), Vc are known and n = 1/α, the barrier heights Фb can be obtained [54]. According to Chattopadhyay’s method [54], from Eq. (11), the surface potential (Ψsurf) can be described as

where Vn is the potential difference of Fermi level and valence band maximum, given as Vn = kT/qln(NV/NA). NA is the accepter carrier concentration (NA = 2(2Πm*kT/h2)3/2 with m* = 0.078 mo, while mo is electron effective mass and Nv is the effective density of states in p-InP valence band [55]. Thus, surface potential Ψsurf is deduced by substituting the Vn value in Eq (12). Figure 8 depicts the experimental surface potential Ψsurf of the Au/GO/p-InP heterojunction diode. From the plot, the values of n and Фb can be evaluated by the relation Фb = Ψsurf(Ic, Vc) + αVc + Vn [54, 56]. The value of α is

As shown in Fig. 8, the critical value of Vc and Ψsurf(Ic, Vc) for the heterojunction are calculated. The Фb and n are calculated using Eqs. (12) and (13) and the values are 0.83 eV, 1.82 in the dark and 0.76 eV, 1.78 under the illumination conditions, respectively.

The C–V measurement is one of the useful tools to attain the key information about the depletion region of the device structure. The characterization of the heterojunction under 1 kHz ~ 1 MHz is described in Fig. 9. It can be clearly observed that the measured capacitance is an intrinsic function of both applied bias and frequency. However, Fig. 9 shows that the capacitance of the Au/GO/p-InP heterojunction exhibits a slow decline with frequency increment, i.e., it offers higher capacitance at low frequencies (f = 1–10 kHz) and lower capacitance at high frequencies (f = 100 kHz to 1 MHz). This predicated that the interface states have an influence on the variance between the capacitance measured at different frequencies [57].

Additionally, parameters like doping (accepter) concentration (NA), diffusion potential (Vdo), and barrier height Фb(C–V) of Au/GO/p-InP heterojunction were evaluated by C–V method. The depletion capacitance of Au/GO/p-InP heterojunction is expressed as: [3, 46].

where A is the active area, εs is the permittivity (εp–InP = 12.4εo). The plot of 1/C2 − V measured at a high frequency of 1 MHz in dark and illuminated condition is shown in Fig. 10. The 1/C2 − V curves should be yielded a straight line [55]. From 1/C2 − V plot, NA, Vdo, and Фb(C–V) of the heterojunction are found to be 4.44 × 1018 cm−3, 0.98 V and 1.01 eV in dark, and 3.23 × 1018 cm−3, 0.86 V and 0.88 eV under illumination, respectively. NA and Vdo are showing lower values under the illumination condition whereas the same for the dark condition exhibit higher values. The decrease in diffusion potential and the increase in the activation carrier concentration under illumination condition implies an enhancement in the heterojunction performance and exhibits a good control for the optoelectronic applications. Although the Фb estimated from C–V data offers higher values than their counterparts derived from I–V data, which could be attributed to the different nature of I–V and C–V measurement techniques [57,58,59,60].

Further, the interface state density (Nss) is a very prominent parameter in the diode which has a strong impact on the conducting organic/inorganic InP interface. In n case of an adequately thicker interfacial layer, the effective barrier height (Фe) and Nss at the interface are stated below:

where β is the voltage coefficient. According to Card and Rhoderick [61, 62], Nss versus Ess − Ev for p-type semiconductor barrier diode can be given as the following relation

and

where εs = 12.4εo and εi = 3.8εo are the permittivity of semiconductor and interfacial layer, respectively. δ is interfacial layer thickness, Nss is interface state density and WD is depletion layer width which is estimated by 1/C2 − V plot at 1 MHz. The energy (Ess) distribution of Nss with respect to valence band top edge (EV) at semiconductor surface is presented as below

where V is a voltage drop across the depletion layer. Thus, the Nss can be calculated using Eq. (16) combined with Eqs. (15) and (18). The values of Nss exponentially decays with an increase in Ess − Ev for heterojunction in the dark and under the illumination conditions is nicely described through Fig. 11. Also, in Fig. 11, a prominent enhancement of Nss has been observed at the middle of the forbidden energy band gap to valence band maximum. As observed in Fig. 11, Nss varied in the range of 3.3629 × 1016 eV−1 cm−2 in (0.39 eV-Ev) to 4.0248 × 1015 eV−1 cm−2 in (0.77 eV-Ev) in the dark, and 3.6584 × 1016 eV−1 cm−2 in (0.41 eV-Ev) eV to 2.9443 × 1015 eV−1 cm−2 in (0.84 eV-Ev) under the illumination condition, respectively, for the Au/GO/p-InP heterojunction diode. A monotonic increase in Nss with respect to voltage lowering is clearly observable. This type of behavior of interface states (Nss) can be elucidated by charge and discharge of Nss under illumination impact [63].

At the same time, to explore the predominant current transport mechanism of Au/GO/p-InP heterojunction, a log–log I–V plot is depicted in Fig. 12. The plot can be sub-divided into three distinct regions (namely as region I, II, III) based on bias voltage. At region I (lower forward voltage V < 0.08 V), a linear dependency of the current on the applied bias (I ~ V) is observed, indicating the transport mechanism obeys the Ohm’s law (ohmic-type behavior) [64]. At region II (moderately high voltage, i.e., 0.15 V < V < 0.40 V), the exponential increment of current (I ~ exp (αV)) suggests that the charge conduction mechanism is dominated by the space-charge-limited current (SCLC) with a discrete trapping level [65]. Eventually, in the region III (at high-voltage region, i.e., 0.80 V < V < 2.30 V), the slope of the plot is inclined to decrease because the device approaches towards the trap-filling limit [66]. The term ‘traps-filling’ significantly influences the conduction process of semiconductors. The experimental outcomes revealed that the studied heterostructure exhibits a clear diversion from ohmic-type of conduction at lower voltage range (region I) to SCLC at higher voltage range (regions II and III) under dark and illuminated conditions, respectively. This behavior is in good agreement with published reports by various research groups working on different organic hybrid heterostructure devices [67, 68].

4 Conclusions

In this study, the Au/GO/p-InP heterojunction is fabricated and the electrical as well as photoelectrical properties are investigated. The ideality factor (n) and the barrier height (Фb) values of the Au/GO/p-InP heterojunction were found to be 1.67 and 0.87 eV in the dark and 1.81 and 0.83 eV in illumination conditions, respectively. The obtained Rs values from three distinct methods (log(I)–V, Cheung’s and Norde) exhibited a certain level of discrepancy, which could be possibly due to the fact that these methods were applied at different voltage regions of the log(I)–V data range. The Фb and n values deduced from Ψsurf–V plot are found to be 0.83 eV, 1.82 in the dark and 0.76 eV, 1.78 under illumination conditions, respectively. The interface state density is one order of magnitude lower for the Au/GO/p-InP heterojunction under illumination conditions compared to the same in dark conditions. The detailed analysis of logI- logV characteristics elucidates that at lower voltage range (region I) the dominant conduction mechanism is ohmic-type behavior, whereas the behavior goes through the space-charge-limited-current (SCLC) conduction mechanism occupied at higher voltage range (i.e., region II and III) in dark and illuminated conditions. The results unveiled that the heterostructure performance in dark was substantially good compared to the same under the light (visible light) condition with respect to the lesser values of Io, n, Nss, and Rs. The experimental consequences suggested that the Au/GO/p-InP heterostructure has promising characteristics to become an emerging candidate for the future photodiode applications.

References

Horváth ZJ, Rakovics V, Szentpáli B, Püspöki S (2003) Schottky junctions on n-type InP for zero bias microwave detectors. Physica Status Solidi 3:916–921

Mccafferty PG, Sellai A, Dawson P, Elabd H (1996) Barrier characteristics of PtSip-Si Schottky diodes as determined from I–V–T measurements. Solid State Electron 39(4):583–592

Rhoderick EH, Rothwarf A (1979) Metal-semiconductor contacts. PHYS TODAY 32(5):66

Wilmsen CW (1985) Physics and chemistry of III–V compound semiconductor interfaces. Electrochim Acta 31(12):1680

Cova P, Singh A, Masut RA (1999) Simultaneous analysis of current–voltage and capacitance–voltage characteristics of metal–insulator–semiconductor diodes with a high mid-gap trap density. J Appl Phys 85(9):6530

Rajagopal Reddy V, Umapathi A, Dasaradha Rao L (2013) Effect of annealing on the electronic parameters of Au/poly(ethylmethacrylate)/n-InP Schottky diode with organic interlayer. Curr Appl Phys 13(8):1604–1610

Chen WX, Yuan MH, Wu K, Zhang YX, Wang ZM, Qin GG (1995) Experimental study on the Er/p-InP Schottky barrier. J Appl Phys 78(1):584–586586

Biber M, Co Kun C, Türüt A (2005) Current–voltage–temperature analysis of inhomogeneous Au/n-GaAs Schottky contacts. Eur Phys J Appl Phys 31(2):79–86

Lin Y, Huang J (2005) Mobility Enhancement and Breakdown Behavior in InP-Based Heterostructure Field-effect Transistor. J Electrochem Soc 152(8):G627. https://doi.org/10.1149/1.1938008

Sugino T, Ito H (1990) Barrier height enhancement of InP Schottky junctions by treatment with photo-decomposed PH/sub 3/. Electron Lett 26(21):1750–1751

Aydogan S, Saglam M, Tueruet A, Onganer Y (2009) Series resistance determination of Au/polypyrrole/p-Si/Al structure by current–voltage measurements at low temperatures. Mater Sci Eng, C 29(4):1486–1490

Güllü Türüt A (2008) Photovoltaic and electronic properties of quercetin/p-InP solar cells. Sol Energy Mater Sol Cells 92(10):1205–1210

Gu Llu O, Tu RuTA (2009) Electrical analysis of organic interlayer-based metal/interlayer/semiconductor diode structures. J Appl Phys 106(10):103716–103717

Aydin ME, Yakuphanoglu F, Eom JH, Hwang DH (2007) Electrical characterization of Al/MEH-PPV/p-Si Schottky diode by current–voltage and capacitance–voltage methods. Phys B 387(1–2):239–244

Kilicoglu T, Tombak A, Ocak YS, Aydemir M (2014) Electrical and photoelectrical characterization of a TTF/p-InP organic-inorganic heterojunction. Microelectron Eng 129:91–95

Lin S, Peng W, Li X, Wu Z, Xu Z, Zhang S, Xu W (2015) Gate tunable monolayer MoS2/InP heterostructure solar cells. Appl Phys Lett 9 (7):666

Chen J, Wang Q, Lv J (2016) Electronic properties of Al/MoO3/p-InP enhanced Schottky barrier contacts. Thin Solid Films 616:145–150

Reddy M, Sreenu K, Reddy V, Park C (2017) Modified electrical properties and transport mechanism of Ti/p-InP Schottky structure with a polyvinylpyrrolidone (PVP) polymer interlayer. J Mater Sci Mater Electron 28(6):4847–4855

Padma R, Sreenu K, Reddy V (2017) Electrical and frequency dependence characteristics of Ti/polyethylene oxide (PEO)/p-type InP organic-inorganic Schottky junction. J Alloy Compd 695:2587–2596

Sreenu K, Venkata Prasad C, Rajagopal Reddy V (2017) Barrier parameters and current transport characteristicsof Ti/p-Inp schottky junction modified using orange G (OG) organic interlayer. J Electron Mater 46:5746–5754

Acar FZ, Buyukbas-Ulusan A, Tataroglu A (2018) Analysis of interface states in Au/ZnO/p-InP (MOS) structure. J Mater Sci: Mater Electron 29(15):12553–12560

Aydin H, Bacaksiz C, Yagmurcukardes N, Karakaya C, Mermer O, Can M, Senger RT, Sahin H, Selamet Y (2018) Experimental and computational investigation of graphene/SAMs/n-Si Schottky diodes. Appl Surf Sci 428:1010–1017

Tomer D, Rajput S, Hudy LJ, Li CH, Li L (2015) Inhomogeneity in barrier height at graphene/Si (GaAs) Schottky junctions. Nanotechnology 26(21):215702

Shivaraman S (2012) Schottky barrier inhomogeneities at the interface of few layer epitaxial graphene and silicon carbide. Appl Phys Lett 100(18):1–4

Giannazzo F, Raineri V, Yakimova R, Huntzinger JR, Tiberj A, Camassel J, Sonde S (2009) Electrical properties of the graphene/4 H -SiC (0001) interface probed by scanning current spectroscopy. Phys Rev B 80(24):241406. https://doi.org/10.1103/PhysRevB.80.241406

Park PS, Reddy KM, Nath DN, Yang Z, Padture NP, Rajan S (2013) Ohmic contact formation between metal and AlGaN/GaN heterostructure via graphene insertion. Appl Phys Lett 102(15):1535011–1535014

Fisichella G, Greco G, Roccaforte F, Giannazzo F (2014) From Schottky to Ohmic graphene contacts to AlGaN/GaN heterostructures: role of the AlGaN layer microstructure. Appl Phys Lett 105(6):63111–63117

Tongay S, Lemaitre M, Schumann T, Berke K, Appleton BR, Gila B, Hebard AF (2011) Graphene/GaN Schottky diodes: stability at elevated temperatures. Appl Phys Lett 99(10):102101–102102

Zhong H, Liu Z, Shi L, Xu G, Fan Y, Huang Z, Wang J, Ren G, Xu K (2014) Graphene in ohmic contact for both n-GaN and p-GaN. Appl Phys Lett 104(21):212101

Kim S, Lee JM, Dong HL, Park WI (2013) The effect of thermal annealing of graphene under ammonia atmosphere on its electrical properties and contact to p-GaN. Thin Solid Films 546(1):246–249

Shiu Hung W, Lo YC, Kai-Hsuan L, Chen H-Y (2013) Graphene as tunable transparent electrode material on GaN: layer-number-dependent optical and electrical properties. Appl Phys Lett 103(8):1–4

Khurelbaatar Z, Kil YH, Yun HJ, Shim KH, Nam JT, Kim KS, Lee SK, Choi CJ (2014) Modification of Schottky barrier properties of Au/n-type Ge Schottky barrier diode using monolayer graphene interlayer. J Alloy Compd 614:323–329

Khurelbaatar Z, Kang M, Shim K, Yun H, Lee J, Hong H, Chang S, Lee S, Choi C (2015) Temperature dependent current–voltage characteristics of Au/n-type Ge Schottky barrier diodes with graphene interlayer. J Alloy Compd 650:658–663. https://doi.org/10.1016/j.jallcom.2015.08.031

Kalita G, Hirano R, Ayhan ME, Tanemura M (2013) Fabrication of Schottky junction diode with direct growth graphene on silicon by a solid phase reaction. J Phys D Appl Phys 46(45):5326–5333

Wang X, Wang Y, Li D, Zou L, Zhang Q, Zhou J, Liu D, Zhang Z (2015) Thermal annealing and air exposing effect on the graphene/silicon Schottky junctions. Solid State Commun 201:115–119. https://doi.org/10.1016/j.ssc.2014.10.028

Lin Y (2015) Correlation between phonon and impurity scatterings, potential fluctuations and leakage conduction of graphene/n-type Si Schottky diodes. Superlattice Microst 88:645–650. https://doi.org/10.1016/j.spmi.2015.10.031

Chen C, Aykol M, Chang C, Levi AFJ, Cronin SB (2011) Graphene-silicon Schottky diodes. Nano Lett 11(5):1863–1867. https://doi.org/10.1021/nl104364c

Mohammed M, Li Z, Cui J, Chen T (2012) Junction investigation of graphene/silicon Schottky diodes. Nanoscale Res Lett 7(1):302. https://doi.org/10.1186/1556-276x-7-302

Zeng J, Lin Y (2014) Schottky barrier inhomogeneity for graphene/Si-nanowire arrays/n-type Si Schottky diodes. Appl Phys Lett 104(13):133506. https://doi.org/10.1063/1.4870258

Niu G, Capellini G, Hatami F, Di Bartolomeo A, Niermann T, Hussein EH, Schubert MA, Krause H, Zaumseil P, Skibitzki O, Lupina G, Masselink WT, Lehmann M, Xie Y, Schroeder T (2016) Selective Epitaxy of InP on Si and Rectification in Graphene/InP/Si Hybrid Structure. ACS Appl Mater Inter 8(40):26948–26955. https://doi.org/10.1021/acsami.6b09592

Wang P, Li X, Xu Z, Wu Z, Zhang S, Xu W, Zhong H, Chen H, Li E, Luo J, Yu Q, Lin S (2015) Tunable graphene/indium phosphide heterostructure solar cells. Nano Energy 13:509–517. https://doi.org/10.1016/j.nanoen.2015.03.023

Gullu O, Cankaya M, Rajagopal Reddy V (2019) Barrier enhancement of Al/n-InP Schottky diodes by graphene oxide thin layer. Indian J Phys 93(4):467–474. https://doi.org/10.1007/s12648-018-1311-4

Phan DT, Gupta RK, Chung GS, Al-Ghamdi AA, Al-Hartomy OA, El-Tantawy F, Yakuphanoglu F (2012) Photodiodes based on graphene oxide–silicon junctions. Sol Energy 86(10):2961–2966. https://doi.org/10.1016/j.solener.2012.07.002

Kalita G, Wakita K, Umeno M, Tanemura M (2013) Fabrication and characteristics of solution-processed graphene oxide–silicon heterojunction. Physica Status Solidi 7(5):340–343. https://doi.org/10.1002/pssr.201206516

Yang L, Yu X, Xu M, Chen H, Yang D (2014) Interface engineering for efficient and stable chemical-doping-free graphene-on-silicon solar cells by introducing a graphene oxide interlayer. J Mater Chem A 2(40):16877–16883. https://doi.org/10.1039/C4TA02216E

Sze S (1981) Physics of semiconductor devices. New York. Serbiula (sistema Librum 2.0) 1. https://doi.org/10.1063/1.3022205

Dahlan AS, Tataroğlu A, Al-Ghamdi AA, Al-Ghamdi AA, Bin-Omran S, Al-Turki Y, El-Tantawy F, Yakuphanoglu F (2015) Photodiode and photocapacitor properties of Au/CdTe/p-Si/Al device. J Alloy Compd 646:1151–1156. https://doi.org/10.1016/j.jallcom.2015.06.068

Sands T (1988) Stability and epitaxy of NiAl and related intermetallic films on III–V compound semiconductors. Appl Phys Lett 52(3):197–199. https://doi.org/10.1063/1.99518

Şahin B, Çetin H, Ayyildiz E (2005) The effect of series resistance on capacitance–voltage characteristics of Schottky barrier diodes. Solid State Commun 135(8):490–495. https://doi.org/10.1016/j.ssc.2005.05.050

Tung RT, Sullivan JP, Schrey F (1992) On the inhomogeneity of Schottky barriers. Mater Sci Eng, B 14(3):266–280. https://doi.org/10.1016/0921-5107(92)90309-W

Greco G, Prystawko P, Leszczyński M, Lo Nigro R, Raineri V, Roccaforte F (2011) Electro-structural evolution and Schottky barrier height in annealed Au/Ni contacts onto p-GaN. J Appl Phys 110(12):123703. https://doi.org/10.1063/1.3669407

Cheung SK, Cheung NW (1986) Extraction of Schottky diode parameters from forward current–voltage characteristics. Appl Phys Lett 49(2):85–87. https://doi.org/10.1063/1.97359

Norde H (1979) A modified forward I–V plot for Schottky diodes with high series resistance. J Appl Phys 50(7):5052–5053. https://doi.org/10.1063/1.325607

Chattopadhyay P (1995) A new technique for the determination of barrier height of Schottky barrier diodes. Solid State Electron 38(3):739–741. https://doi.org/10.1016/0038-1101(94)00167-E

Aydoğan S, Sağlam M, Türüt A (2005) Current–voltage and capacitance–voltage characteristics of polypyrrole/p-InP structure. Vacuum 77(3):269–274. https://doi.org/10.1016/j.vacuum.2004.10.003

Chattopadhyay S, Bera LK, Ray SK, Bose PK, Maiti CK (1998) Extraction of interface state density of Pt/p-strained-Si Schottky diode. Thin Solid Films 335(1):142–145. https://doi.org/10.1016/S0040-6090(98)00892-X

Siad M, Keffous A, Mamma S, Belkacem Y, Menari H (2004) Correlation between series resistance and parameters of Al/n-Si and Al/p-Si Schottky barrier diodes. Appl Surf Sci 236(1):366–376. https://doi.org/10.1016/j.apsusc.2004.05.009

Soylu M, Yakuphanoglu F (2010) Analysis of barrier height inhomogeneity in Au/n-GaAs Schottky barrier diodes by Tung model. J Alloy Compd 506(1):418–422. https://doi.org/10.1016/j.jallcom.2010.07.019

Card HC, Rhoderick EH (1971) Studies of tunnel MOS diodes I@@ Interface effects in silicon Schottky diodes. J Phys D Appl Phys 4(10):1589–1601. https://doi.org/10.1088/0022-3727/4/10/319

Taşçıoğlu I, Soylu M, Altındal S, Al-Ghamdi AA, Yakuphanoglu F (2012) Effects of interface states and series resistance on electrical properties of Al/nanostructure CdO/p-GaAs diode. J Alloy Compd 541:462–467. https://doi.org/10.1016/j.jallcom.2012.07.001

Güllü Ö, Aydoğan S, Türüt A (2008) Fabrication and electrical characteristics of Schottky diode based on organic material. Microelectron Eng 85(7):1647–1651. https://doi.org/10.1016/j.mee.2008.04.003

Card HC, Rhoderick EH (1971) Studies of tunnel MOS diodes II@ Thermal equilibrium considerations. J Phys D Appl Phys 4(10):1602–1611. https://doi.org/10.1088/0022-3727/4/10/320

Uslu H, Altındal S, Aydemir U, Dökme I, Afandiyeva IM (2010) The interface states and series resistance effects on the forward and reverse bias I–V, C–V and G/ω–V characteristics of Al–TiW–Pd2Si/n-Si Schottky barrier diodes. J Alloy Compd 503(1):96–102. https://doi.org/10.1016/j.jallcom.2010.04.210

Aydoğan S, İncekara Ü, Deniz AR, Türüt A (2010) Extraction of electronic parameters of Schottky diode based on an organic Orcein. Microelectron Eng 87(12):2525–2530. https://doi.org/10.1016/j.mee.2010.06.004

Dutta M, Basak D (2008) p-ZnO∕n-Si heterojunction: sol-gel fabrication, photoresponse properties, and transport mechanism. Appl Phys Lett 92(21):212112. https://doi.org/10.1063/1.2937124

El-Sayed SM, Abdel Hamid HM, Radwan RM (2004) Effect of electron beam irradiation on the conduction phenomena of unplasticized PVC/PVA copolymer. Radiat Phys Chem 69(4):339–345. https://doi.org/10.1016/j.radphyschem.2003.07.001

Gupta RK, Yakuphanoglu F, Hasar H, Al-Khedhairy AA (2011) p-Si/DNA photoconductive diode for optical sensor applications. Synthetic Met 161(17):2011–2016. https://doi.org/10.1016/j.synthmet.2011.07.016

Demirezen S, Altındal S, Uslu I (2013) Two diodes model and illumination effect on the forward and reverse bias I–V and C–V characteristics of Au/PVA (Bi-doped)/n-Si photodiode at room temperature. Curr Appl Phys 13(1):53–59. https://doi.org/10.1016/j.cap.2012.06.009

Acknowledgements

The authors would like to thank the National Science Fund for Excellent Young Scholars (51722509), National Key Research and Development Program of China (2017YFB1104700), Program for Science and Technology Innovation Group of Shaanxi Province (2019TD-011), and Key Research and Development Program of Shaanxi Province (2020ZDLGY04-02) for support..

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Lambada, D.R., Yang, S., Wang, Y. et al. Investigation of Illumination Effects on the Electrical Properties of Au/GO/p-InP Heterojunction with a Graphene Oxide Interlayer. Nanomanuf Metrol 3, 269–281 (2020). https://doi.org/10.1007/s41871-020-00078-z

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s41871-020-00078-z