Abstract

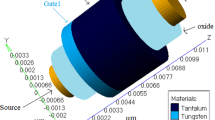

In this paper, a dual dielectric drain—dual dielectric gate hetero-structure Si0.2Ge0.8/GaAs charge plasma-based junctionless TFET (DDD-DDG-HJLTFET) is proposed and analyzed. Here mixed concepts of the band gap, drain dielectric pocket, and hetero dielectric gate engineering is utilized with the novel amalgamation of Si0.2Ge0.8/GaAs for the first time to reduce ambipolar conduction and improve the electrical characteristics of the device. To indicate the superiority of the reported device, results are compared with single dielectric gate hetero-structure JLTFET (SDG-HJLTFET) and traditional Si-JLTFET. The DDD-DDG-HJLTFET provides better performance than SDG-HJLTFET and Si-JLTFET in terms of D.C characteristics depicting ~ 2 and ~ 330 times greater ION, ~ 63 and ~ 4 × 109 times higher ION/IAmb ratio along with ~ 31, ~ 1.2 × 107 times lower IAmb and ~ 6%, ~ 67% lower subthreshold slope (SS) respectively. Furthermore, to check the suitability of the reported device in RF application, transconductances (gm, gm3), gate capacitances (Cgd, Cgg), cut-off frequency (fT), gain bandwidth product (GBWP), transconductance frequency product (TFP), intrinsic delay (τ), 2nd and 3rd order voltage intercept point (VIP2 and VIP3), 3rd order input intercept point (IIP3) has been analyzed. The proposed device shows superior RF performance in comparison to SDG-HJLTFET and Si-JLTFET, making it suitable for high-frequency and low-power applications.

Similar content being viewed by others

Data Availability

Data will be made available on request.

References

Wang PF, Hilsenbeck K, Nirschl T et al (2004) Complementary tunneling transistor for low power application. Solid State Electron 48:2281–2286. https://doi.org/10.1016/J.SSE.2004.04.006

Seabaugh AC, Zhang Q (2010) Low-voltage tunnel transistors for beyond CMOS logic. Proc IEEE 98:2095–2110. https://doi.org/10.1109/JPROC.2010.2070470

Choi WY, Park BG, Lee JD, Liu TJK (2007) Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett 28:743–745. https://doi.org/10.1109/LED.2007.901273

Ionescu AM (2011) Riel H (2011) Tunnel field-effect transistors as energy-efficient electronic switches. Nat 4797373(479):329–337. https://doi.org/10.1038/nature10679

Gupta SK, Kulkarni JP, Datta S, Roy K (2012) Heterojunction intra-band tunnel FETs for low-voltage SRAMs. IEEE Trans Electron Devices 59:3533–3542. https://doi.org/10.1109/TED.2012.2221127

Raad BR, Nigam K, Sharma D, Kondekar PN (2016) Performance investigation of bandgap, gate material work function and gate dielectric engineered TFET with device reliability improvement. Superlattices Microstruct 94:138–146. https://doi.org/10.1016/J.SPMI.2016.04.016

Chen S, Wang S, Liu H, et al (2020) A Novel Dopingless Fin-Shaped SiGe Channel TFET with Improved Performance. Nanoscale Res Lett 15:. https://doi.org/10.1186/S11671-020-03429-3

Vijayvargiya V, Vishvakarma SK (2014) Effect of Drain Doping Profile on Double-Gate Tunnel Field-Effect Transistor and its Influence on Device RF Performance. IEEE Trans Nanotechnol 13:974–981. https://doi.org/10.1109/TNANO.2014.2336812

Yadav DS, Sharma D, Raad BR, Bajaj V (2016) Impactful study of dual work function, underlap and hetero gate dielectric on TFET with different drain doping profile for high frequency performance estimation and optimization. Superlattices Microstruct 96:36–46. https://doi.org/10.1016/J.SPMI.2016.04.027

Abdi DB, Kumar MJ (2014) Controlling ambipolar current in tunneling FETs using overlapping gate-on-drain. IEEE J Electron Devices Soc 2:187–190. https://doi.org/10.1109/JEDS.2014.2327626

Lee MJ, Choi WY (2012) Effects of device geometry on hetero-gate-dielectric tunneling field-effect transistors. IEEE Electron Device Lett 33:1459–1461. https://doi.org/10.1109/LED.2012.2206790

Choi WY, Lee W (2010) Hetero-gate-dielectric tunneling field-effect transistors. IEEE Trans Electron Devices 57:2317–2319. https://doi.org/10.1109/TED.2010.2052167

Panda S, Jena B, Dash S (2022) Ambipolarity Suppression of a Double Gate Tunnel FET using High-k Drain Dielectric Pocket. ECS J Solid State Sci Technol 11:013014. https://doi.org/10.1149/2162-8777/ac4d82

Ram MS, Abdi DB (2015) Dopingless PNPN tunnel FET with improved performance: Design and analysis. Superlattices Microstruct 82:430–437. https://doi.org/10.1016/J.SPMI.2015.02.024

Gundapaneni S, Bajaj M, Pandey RK et al (2012) Effect of band-to-band tunneling on junctionless transistors. IEEE Trans Electron Devices 59:1023–1029. https://doi.org/10.1109/TED.2012.2185800

Bashir F, Loan SA, Rafat M et al (2015) A high performance gate engineered charge plasma based tunnel field effect transistor. J Comput Electron 14:477–485. https://doi.org/10.1007/S10825-015-0665-5/FIGURES/16

Ghosh B, Akram MW (2013) Junctionless tunnel field effect transistor. IEEE Electron Device Lett 34:584–586. https://doi.org/10.1109/LED.2013.2253752

Goswami Y, Ghosh B, Asthana PK (2014) Analog performance of Si junctionless tunnel field effect transistor and its improvisation using III-V semiconductor. RSC Adv 4:10761–10765. https://doi.org/10.1039/c3ra46535g

Anand S, Amin SI, Sarin RK (2016) Performance analysis of charge plasma based dual electrode tunnel FET. J Semicond 37:054003. https://doi.org/10.1088/1674-4926/37/5/054003

Lahgere A, Sahu C, Singh J (2015) PVT-Aware Design of Dopingless Dynamically Configurable Tunnel FET. IEEE Trans Electron Devices 62:2404–2409. https://doi.org/10.1109/TED.2015.2446615

Nigam K, Kondekar P, Sharma D, Raad BR (2016) A new approach for design and investigation of junction-less tunnel FET using electrically doped mechanism. Superlattices Microstruct 98:1–7. https://doi.org/10.1016/J.SPMI.2016.07.016

Bal P, Akram MW, Mondal P, Ghosh B (2013) Performance estimation of sub-30 nm junctionless tunnel FET (JLTFET). J Comput Electron 12:782–789. https://doi.org/10.1007/S10825-013-0483-6/FIGURES/13

Bashir F, Loan SA (2014) Design and simulation of a high performance dopingless p-tunnel field effect transistor. 2014 IEEE 2nd Int Conf Emerg Electron Mater to Devices, ICEE 2014 - Conf Proc. https://doi.org/10.1109/ICEMELEC.2014.7151160

Akram MW, Ghosh B, Bal P, Mondal P (2014) P-type double gate junctionless tunnel field effect transistor. J Semicond 35:. https://doi.org/10.1088/1674-4926/35/1/014002

MolaeiImenAbadi R, SedighZiabari SA (2016) Representation of strained gate-all-around junctionless tunneling nanowire filed effect transistor for analog applications. Microelectron Eng 162:12–16. https://doi.org/10.1016/J.MEE.2016.04.016

Kumar K, Kumar A, Mishra V, Chandra S (2022) Implementation of Band Gap and Gate Oxide Engineering to Improve the Electrical Performance of SiGe / InAs Charged Plasma - Based Junctionless - TFET. SILICON. https://doi.org/10.1007/s12633-022-02111-w

Rahi SB, Ghosh B, Bishnoi B et al (2015) Temperature effect on hetero structure junctionless tunnel FET. J Semicond 36(3):034002-034002-5 36:034002-034002–5. https://doi.org/10.1088/1674-4926/36/3/034002

Bal P, Ghosh B, Mondal P et al (2014) Dual material gate junctionless tunnel field effect transistor. J Comput Electron 13:230–234. https://doi.org/10.1007/S10825-013-0505-4/FIGURES/6

Lahgere A, Panchore M, Singh J (2016) Dopingless ferroelectric tunnel FET architecture for the improvement of performance of dopingless n-channel tunnel FETs. Superlattices Microstruct 96:16–25. https://doi.org/10.1016/J.SPMI.2016.05.004

Goswami Y, Asthana P, Basak S, Ghosh B (2015) Junctionless tunnel field effect transistor with nonuniform doping. Int J Nanosci 14:. https://doi.org/10.1142/S0219581X14500252

Rahimian M, Fathipour M (2016) Asymmetric junctionless nanowire TFET with built-in n+ source pocket emphasizing on energy band modification. J Comput Electron 15:1297–1307. https://doi.org/10.1007/S10825-016-0895-1/TABLES/1

Raad BR, Sharma D, Kondekar P et al (2016) Drain Work Function Engineered Doping-Less Charge Plasma TFET for Ambipolar Suppression and RF Performance Improvement: A Proposal, Design, and Investigation. IEEE Trans Electron Devices 63:3950–3957. https://doi.org/10.1109/TED.2016.2600621

Aghandeh H, SedighZiabari SA (2017) Gate engineered heterostructure junctionless TFET with Gaussian doping profile for ambipolar suppression and electrical performance improvement. Superlattices Microstruct 111:103–114. https://doi.org/10.1016/j.spmi.2017.06.018

Venkatasubramanian R, Timmons ML, Mantini M et al (1990) (2011) Heteroepitaxy and Characterisation Of Ge-Rich SiGe Alloys on GaAs. MRS Online Proc Libr 1981(198):547–552. https://doi.org/10.1557/PROC-198-547

Kumar K, Sharma SC (2022) Impact of band gap and gate dielectric engineering on novel Si 0.1 Ge 0.9 -GaAs lateral N-type charge plasma based JLTFET. Microelectronics J 130:105610. https://doi.org/10.1016/j.mejo.2022.105610

Youssouf AS, Habaebi MH, Ibrahim SN, Hasbullah NF (2017) Gain Investigation for commercial GaAs and SiGe HBT LNA’s under Electron irradiation. Proc - 14th IEEE Student Conf Res Dev Adv Technol Humanit SCOReD 2016. https://doi.org/10.1109/SCORED.2016.7810094

Han T, Liu H, Wang S et al (2019) Design and Investigation of the Junction-Less TFET with Ge/Si0.3Ge0.7/Si Heterojunction and Heterogeneous Gate Dielectric. Electron 8:476 8:476. https://doi.org/10.3390/ELECTRONICS8050476

Asthana PK, Ghosh B, Goswami Y, Tripathi BMM (2014) High-speed and low-power ultradeep-Submicrometer III-V heterojunctionless tunnel field-effect transistor. IEEE Trans Electron Devices 61:479–486. https://doi.org/10.1109/TED.2013.2295238

Silvaco Atlas user’s manual (2018) [Online]. Available: http://www.silvaco.com

Hänsch W, Vogelsang T, Kircher R, Orlowski M (1989) Carrier transport near the Si/SiO2 interface of a MOSFET. Solid State Electron 32:839–849. https://doi.org/10.1016/0038-1101(89)90060-9

Zhao Y, Wu C, Huang Q et al (2017) A Novel Tunnel FET Design Through Adaptive Bandgap Engineering with Constant Sub-Threshold Slope over 5 Decades of Current and High ION/IOFF Ratio. IEEE Electron Device Lett 38:540–543. https://doi.org/10.1109/LED.2017.2679031

Zhou G, Lu Y, Li R et al (2011) Self-aligned InAs/Al0.45Ga0.55Sb vertical tunnel FETs. Device Res Conf - Conf Dig DRC 205–206. https://doi.org/10.1109/DRC.2011.5994499

Na KY, Kim YS (2006) Silicon complementary metal-oxide-semiconductor field-effect transistors with dual work function gate. Japanese J Appl Physics, Part 1 Regul Pap Short Notes Rev Pap 45:9033–9036. https://doi.org/10.1143/JJAP.45.9033/META

Wang CH, Chu H, Lai YS et al (2008) Dual work-function metal gates, vol 73. US Patent, p 81619B2

Johnson RW, Hultqvist A, Bent SF (2014) A brief review of atomic layer deposition: from fundamentals to applications. Mater Today 17:236–246. https://doi.org/10.1016/J.MATTOD.2014.04.026

Brouzet V, Salem B, Periwal P et al (2015) Fabrication and characterization of silicon nanowire p-i-n MOS gated diode for use as p-type tunnel FET. Appl Phys A Mater Sci Process 121:1285–1290. https://doi.org/10.1007/S00339-015-9507-3

Xie H, Liu H, Wang S et al (2019) Improvement of Electrical Performance in Heterostructure Junctionless TFET Based on Dual Material Gate. Appl Sci 10:126 10:126. https://doi.org/10.3390/APP10010126

Paras N, Chauhan SS (2019) Insights into the DC, RF/Analog and linearity performance of vertical tunneling based TFET for low-power applications. Microelectron Eng 216:111043. https://doi.org/10.1016/J.MEE.2019.111043

Sharma S, Chaujar R (2022) RF, linearity and intermodulation distortion analysis with small-signal parameters extraction of tunable bandgap arsenide/antimonide tunneling interfaced JLTFET. Microsyst Technol. https://doi.org/10.1007/S00542-022-05273-0

Tirkey S, Sharma D, Yadav DS, Yadav S (2017) Analysis of a Novel Metal Implant Junctionless Tunnel FET for Better DC and Analog/RF Electrostatic Parameters. IEEE Trans Electron Devices 64:3943–3950. https://doi.org/10.1109/TED.2017.2730922

Acknowledgements

The research work has been carried out at “Microelectronics and VLSI lab” in the Department of Electronics and Computer Discipline DPT, Indian Institute of Technology Roorkee, Uttarakhand, India. The authors are thankful to Dr. Ajay Kumar (Assistant Professor Senior Grade in Electronics and Communication Engineering at Jaypee Institute of Information Technology, Noida, India) for his valuable supports and to IIT Roorkee and the research cell for the necessary facilities to conduct this research work.

Funding

Not Applicable.

Author information

Authors and Affiliations

Contributions

Conceptualization: [Kaushal Kumar]; Methodology: [Kaushal Kumar]; Formal analysis and investigation: [Kaushal Kumar, Subhash Chandra Sharma]; Writing—original draft preparation: [Kaushal Kumar]; Writing—review and editing: [Kaushal Kumar, Subhash Chandra Sharma].

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Ethics Approval

Not Applicable.

Consent to Participate

Not Applicable.

Consent for Publication

Not Applicable.

Conflict of Interest

The authors declare that they have no conflicts of interest.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Kumar, K., Sharma, S.C. Band Gap and Drain Dielectric Pocket Engineered Si0.2Ge0.8/GaAs Junctionless TFET with Dual Dielectric Gate for Ambipolar Suppression and Electrical Performance Enhancement. Silicon 15, 2663–2677 (2023). https://doi.org/10.1007/s12633-022-02192-7

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-022-02192-7