Abstract

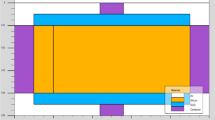

The main aim of this work is to study the effect of symmetric and asymmetric spacer length variations towards source and drain on n-channel SOI JL vertically stacked (VS) nanowire (NW) FET at 10 nm gate length (LG). Spacer length is proved to be one of the stringent metrics in deciding device performance along with width, height and aspect ratio (AR). The physical variants in this work are symmetric spacer length (LSD), source side spacer length (LS) and drain side spacer length (LD). The simulation results give the highest ION/IOFF ratio with LD variation compared to LS and LSD, whereas latter two variations have similar effect on ION/IOFF ratio. At 25 nm (2.5 × LG) of LD, the device gives appreciable ON current with the highest ION/IOFF ratio (2.19 × 108) with optimum subthreshold slope (SS) and ensures low power and high switching drivability. Moreover, it is noticed that among optimal values of LS and LD, the device ION/IOFF ratio has an improvement of 22.69% as compared to other variations. Moreover, the effect of various spacer dielectrics on optimized device is also investigated. Finally, the CMOS inverter circuit analysis is performed on the optimized symmetric and asymmetric spacer lengths.

Similar content being viewed by others

Data Availability

Not applicable.

References

Lin Y, Lin YH, Chen YF, Hsu YT, Chen YH, Huang YH, Wu YC (2020) Performance of Junctionless and inversion-mode thin-film transistors with stacked Nanosheet channels. IEEE Trans Nanotechnol 19:84–88

Fang WW, Singh N, Bera LK, Nguyen HS, Rustagi SC, Lo GQ, Balasubramanian N, Kwong D-L (2007) Vertically stacked SiGe nanowire Array Channel CMOS transistors. IEEE Electron Device Lett 28(3):211–213

Maheshwaram S, Manhas SK, Kaushal G, Anand B, Singh N (2013) Vertical nanowire CMOS parasitic modeling and its performance analysis. IEEE Trans Electron Devices 60(9):2943–2950

Sreenivasulu VB, Narendar V (2021) Junctionless, “Gate-all-around nanowire FET with asymmetric spacer for continued scaling”. Silicon. https://doi.org/10.1007/s12633-021-01471-z

Bala S, Kumar R, Kumar A (2021) Parameter variation analysis of Dopingless and Junctionless nanotube MOSFET. Silicon. https://doi.org/10.1007/s12633-021-01303-0

Meriga C, Ponnuri RT, Satyanarayana BVV, Gudivada AAK, Panigrahy AK, Prakash MD (2021) A novel teeth junction less gate all around FET for improving electrical characteristics. Silicon. https://doi.org/10.1007/s12633-021-00983-y

Colinge JP, Lee CW, Afzalian A, Akhavan ND, Yan R, Ferain I, Rezavi P, Neil BO, Blake A, White M, Kelleher AN, McCarthy B, Murphy R (2010) Nanowire transistors without junction. Nat Nanotechnol 5(3):225–229

Sreenivasulu VB, Narendar V (2021) p-Type Trigate Junctionless Nanosheet MOSFET: Analog/RF, Linearity, and Circuit Analysis. ECS J Solid State Sci Technol 10:123001

Barman KR, Baishya S (2021) The beneficial impact of a p-p+ junction on DC and analog/radio frequency performance of a vertical super-thin body FET. Int J RF Microw Comput-Aided Eng 31:e22938

Sreenivasulu VB, Narendar V (2021) Characterization and optimization of junctionless gate-all-around vertically stacked nanowire FETs for sub-5 nm technology nodes. Microelectron J 117:105214. https://doi.org/10.1016/j.mejo.2021.105214

Goel A, Gupta SK, Roy K (2011) Asymmetric drain spacer extension (ADSE) FinFETs for low- power and robust SRAMs. IEEE Trans Electron Devices 58(2):296–308

Pal PK, Kaushik BK, Dasgupta S (2014) Investigation of symmetric dual-k spacer Trigate FinFETs from delay perspective. IEEE Trans Electron Devices 61(11):3579–3585

Barman KR, Baishya S (2021) Improved electrical and RF performance of a junctionless vertical super-thin body (VSTB) FET by increased substrate doping. Mater Sci Semicond Process 135:106100. https://doi.org/10.1016/j.mssp.2021.106100

Kumar R, Bala S, Kumar A (2021) Study and analysis of advanced 3D multi-gate Junctionless transistors. Silicon. https://doi.org/10.1007/s12633-020-00904-5

Kumar R, Kumar A (2020) Hetro-Dielctric (HD) oxide-engineered junctionless double gate all around (DGAA) nanotube field effect transistor (FET). Silicon 13(7):2177–2184

Sreenivasulu VB, Narendar V (2021) Design insights into RF/analog and linearity/distortion of spacer engineered multi-fin SOI FET for terahertz applications. Int J RF Microw Comput Aided Eng 31(9):e22875. https://doi.org/10.1002/mmce.22875

Barraud S, Berthome M, Coquand R, Casse M, Ernst T, Samson MP, Perreau P, Bourdelle KK, Faynot O, Poiroux T (Sept. 2012) Scaling of Trigate Junctionless nanowire MOSFET with gate length down to 13 nm. IEEE Electron Device Lett 33(9):1225–1227. https://doi.org/10.1109/LED.2012.2203091

Sreenivasulu VB, Narendar V (2021) A comprehensive analysis of Junctionless tri-gate (TG) FinFET towards low-power and high-frequency applications at 5-nm gate length. Silicon

Genius (2008) 3-D Device Simulator, Version1.9.0, Reference Manual, Cogenda, Singapore

Jegadheesan V, Sivasankaran K (2020) Aniruddha Konar, improved statistical variability and delay performance with junctionless inserted oxide FinFET. AEU Int J Electron Commun 115:153030

Sreenivasulu VB, Narendar V (2021) Design and Temperature Assessment of Junctionless Nanosheet FET for Nanoscale Applications. Silicon

Narendar V, Narware P, Bheemudu V, Sunitha B (2019) Investigation of Short Channel effects (SCEs) and analog/RF figure of merits (FOMs) of dual-material bottom-spacer ground-plane (DMBSGP) FinFET. Silicon 12:2283–2291

Na MH, Nowak EJ, Haensch W, Cai J (2002) The effective drive current in CMOS inverters. Tech Dig - Int Electron Devices Meet:121–124

Hu J, Park JE, Freeman G, Wachnik R, Philip Wong HS (2008) Effective drive current in CMOS inverters for sub-45nm technologies, Tech. Proc. 2008 NSTI Nanotechnol. Conf. Trade Show, NSTI Nanotech. Nanotechnol 3:829–832

Sagar K, Satish M (2021) A novel circular double-gate SOI MOSFET with raised source/drain. Semicond Sci Technol 36:065009

Sreenivasulu VB, Narendar V (2021) Junctionless SOI FinFET with advanced spacer techniques for Sub-3 nm technology nodes. AEU Int J Electron Commun 145:154069. https://doi.org/10.1016/j.aeue.2021.154069

Kola SR, Li Y, Thoti N (2020) “Effects of Spacer and Single-Charge Trap on Voltage Transfer Characteristics of Gate-All-Around Silicon Nanowire CMOS Devices and Circuits,” 2020 IEEE 20th International Conference on Nanotechnology (IEEE-NANO), pp. 217–220. https://doi.org/10.1109/NANO47656.2020.9183712

Kumar R, Kumar A (2021) Hetro-dielectric (HD) oxide-engineered Junctionless double gate all around (DGAA) nanotube field effect transistor (FET). Silicon 13:2177–2184

Acknowledgements

The authors thank to the department of Electronics and Communications Engineering, NIT Warangal for providing the TCAD Tools.

Funding

No Funding Received.

Author information

Authors and Affiliations

Contributions

V. Bharath Sreenivasulu: Writing- Original draft preparation, Formal Analysis, Investigation, Simulation, Data Curation.

V. Narendar: Supervision, Resources.

Corresponding author

Ethics declarations

Consent to Participate

Not applicable.

Consent for Publication

Not applicable.

Financial Interests

The authors declare they have no financial interests.

Conflict of Interest

The author has no conflicts of interest to declare that are relevant to the content of this article.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Sreenivasulu, V.B., Narendar, V. Circuit Analysis and Optimization of GAA Nanowire FET Towards Low Power and High Switching. Silicon 14, 10401–10411 (2022). https://doi.org/10.1007/s12633-022-01777-6

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-022-01777-6