Abstract

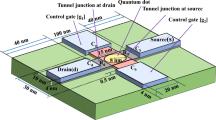

In this paper, a novel vertically stacked silicon Nanosheet Tunnel Field Effect Transistor (NS-TFET) device scaled to a gate length of 12 nm with Contact poly pitch (CPP) of 48 nm is simulated. NS-TFET device is investigated for its electrostatics characteristics using technology computer-aided design (TCAD) simulator. The inter-band tunneling mechanism with a P-I-N layout has been incorporated in the stacked nanosheet devices. The asymmetric design technique for doping has been used for optimum results. NS-TFET provides a low leakage current of order10−16 A, an excellent subthreshold swing (SW) of 23mv/decade, and negligible drain induced barrier lowering (DIBL) having a value of 10.5 mv/V. The notable ON to OFF current ratio of the order of 1011 has been achieved. The device exhibits a high transconductance of 3.022 × 10−5 S at the gate to source voltage of 1 V. The radiation effect of an alpha particle at different energies on NS-TFET is investigated. The injection causes drain current fluctuation for a short span and the result can serve as a guideline for designing of a robust circuit. NS-TFET shows tremendous improvement in short channel effects (SCE) and is a good option for advanced technologies.

Similar content being viewed by others

References

Jang D, Yakimets D, Eneman G, Schuddinck P, Bardo MG (2017) Device Exploration of NanoSheet Transistors for Sub-7-nm Technology Node. IEEE Trans Electron Devices 64(6):2707–2713. https://doi.org/10.1109/TED.2017.2695455

Barraud S, Lapras V, Previtali B, Samson MP, Lacord J, Martinie S, Jaud MA, Athanasiou S, Triozon F, Rozeau O, Hartmann JM, Vizioz C, Comboroure C, Andrieu F, Barbé JC, Vinet M, Ernst T (2017) Performance and design considerations for gate-all-around stacked-NanoWires FETs. IEEE International Electron Devices Meeting (IEDM). doi: https://doi.org/10.1109/IEDM.2017.8268473

Yakimets D, Bardon MG, Jang D, Schuddinck P, Sherazi Y, Weckx P, Miyaguchi K, Parvais B, Raghavan P, Spessot A, Verkest D, Mocuta A (2017) Power-aware FinFET and lateral nanosheet FET targeting for 3nm CMOS technology. IEEE international Electron devices meeting (IEDM), San Francisco. https://doi.org/10.1109/IEDM.2017.8268429

He X, Fronheiser J, Zhao P, Hu Z, Uppal S, Wu X, Hu Y, Sporer R, Qin L, Krishnan R, Bazizi EM, Carter R, Tabakman K, Jha AK, Yu H, Hu O, Choi D, Lee JG, Samavedam SB, Sohn DK (2017) Impact of aggressive fin width scaling on finfet device characteristics. IEEE international Electron devices meeting (IEDM), San Francisco. https://doi.org/10.1109/IEDM.2017.8268427

Bufler FM, Ritzenthaler R, Mertens H, Eneman G, Mocut A, Horiguchi N (2018) Performance Comparison of n-Type Si Nanosheets, and FinFETs by MC Device Simulation. IEEE Electron Device Lett 39(11):1628–1631. https://doi.org/10.1109/LED.2018.2868379

P. Feng, S. Song, G. Nallapati, J. Zhu, J. Bao, V. Moroz, M. Choi, X. Lin, Q. Lu, B. Colombeau, N. Breil, M. Chudzik and C. Chidambaram, "Comparative Analysis of Semiconductor Device Architectures for 5-nm Node and Beyond pp.," IEEE Electron Device Lett, vol. 38, no. 12, p. 1657–1660, Dec 2017. doi: https://doi.org/10.1109/LED.2017.2769058

Kalna K, Nagy D, García-Loureiro AJ, Seoane N (2019) 3D Schrödinger equation quantum corrected Monte Carlo and Drift diffusion simulations of stacked Nanosheet gate-all-around transistor, in IWCN. Institute for Microelectronics, TU Wien, Wien, pp 33–35

Kim SD, Guillorn M, Lauer I, Oldiges P, Hook T, Na MH (2015) Performance Trade-offs in FinFET and Gate-All-Around Device Architectures for 7nm-node and Beyond. IEEE SOI-3D-subthreshold microelectronics technology unified conference (S3S), Rohnert Park. https://doi.org/10.1109/S3S.2015.7333521

Yakimets D, Bardon MG, Jang D, Schuddinck P, Sherazi Y, Weckx P, Miyaguchi K, Parvais B, Raghavan P, Spessot A, Verkest D, Mocuta A (2017) Power aware FinFET and lateral nanosheet FET targeting for 3nm CMOS technology. IEEE International Electron Devices Meeting (IEDM), p. 501–504. doi: https://doi.org/10.1109/IEDM.2017.8268429

Cai L, Chen W, Du G, Zhang X, Liu X (2018) Layout design correlated with self-heating effect in stacked Nanosheet transistors. IEEE Trans Electron Devices 65(6):2647–2653. https://doi.org/10.1109/TED.2018.2825498

Loubet N, Hook T, Montanini P, Yeung CW, Kanakasab S Stacked nanosheet gateallaround transistor to enable scaling beyond FinFET. In Symposium on VLSI Technology, T230–T231, 2017. doi: https://doi.org/10.23919/VLSIT.2017.7998183

Moon D, Choi S, Duarte JP, Choi Y (2013) Investigation of silicon nanowire gate-all-around Junctionless transistors built on a bulk substrate. IEEE Trans Electron Devices 60:1355–1360. https://doi.org/10.1109/TED.2013.2247763

Chen H, Wu Y, Chang C, Han M, Lu N, Ch Y (2013) Performance of GAA poly-Si nanosheet (2nm) channel of junctionless transistors with ideal subthreshold slope. In symposium on VLSI technology

Choi WY, Park B, Lee JD, Liu TK (2007) Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett 28(8):743–745. https://doi.org/10.1109/LED.2007.901273

Colinge J (2008) FinFETs and other multi-gate transistors. Springer, New York. https://doi.org/10.1007/978-0-387-71752-4

Kumar S, Goel E, Singh K, Singh B, Singh PK, Baral K (2017) 2-D analytical modeling of the electrical characteristics of dual-material double-gate TFETS with a sio2/hfo2 stacked gate-oxide structure. IEEE Trans Electron Devices 64(3):960–968. https://doi.org/10.1109/TED.2017.2656630

Vaddi R, Agarwal RP, Dasgupta S (2011) Analytical modeling of subthreshold current and subthreshold swing of an underlap DGMOSFET with tied–independent gate and symmetric–asymmetric options. J Microelectron 42(5):798–807. https://doi.org/10.1016/j.mejo.2011.01.004

Wadhwa G, Raj B (2018) Label free detection of biomolecules using charge-plasma-based gate underlap dielectric modulated Junctionless TFET. J Electronics Material Springer 47(8):4883–4893. https://doi.org/10.1007/s11664-018-6343-1

Cao W, Sarkar D, Khatami Y (2014) Subthreshold-swing physics of tunnel field-effect transistors. AIP 4(6):067141–1–067141-9. https://doi.org/10.1063/1.4881979

Vijayvargiya V, Reniwal BS, Singh P, Vishvakarma SK (2016) Analogue/RF performance attributes of underlap tunnel field effect transistor for low power applications. Electron Letters 52(7):559–560. https://doi.org/10.1049/el.2015.3797

Jegadheesan V, Sivasankaran K, Konar A (2019) Impact of geometrical parameters and substrate on analog/RF performance of stacked nanosheet field effect transistor. Mater Sci Semicond Process 93:188–195. https://doi.org/10.1016/j.mssp.2019.01.003

Dutta U, Soni MK, Pattanaik M (2018) Design and Optimisation of GATE-All-Around Tunnel FET for Low Power Applications. Int J Eng Technol 7(4):2263–2270. https://doi.org/10.14419/ijet.v7i4.12352

D. B. Abdi and M. J. Kumar, "Controlling Ambipolar Current in Tunneling FET’s using Overlapping Gate-on Drain," J Electron Devices Soc, vol. 2, no. 6, pp. 187–190, Nov. 2014. doi: https://doi.org/10.1109/JEDS.2014.2327626 Genius Semiconductor Device Simulator Reference Manual

Vardhan PH, Ganguly AS, Gangu U (2019) Threshold voltage variability in Nanosheet GAA transistors. IEEE Trans Electron Devices 66:4433–4438. https://doi.org/10.1109/TED.2019.2933061

Ye P, Ernst T, Khare MV (2019) The last silicon transistor: Nanosheet devices could be the final evolutionary step for Moore's law. IEEE Spectr 56:30–35. https://doi.org/10.1109/MSPEC.2019.8784120

Dash TP, Dey S, Mohapatra E, Das S, Jena J (2019) Vertically-Stacked Silicon Nanosheet Field Effect Transistors at 3nm Technology Nodes. Devices for Integrated Circuit (DevIC), pp. 99–103. doi: https://doi.org/10.1109/DEVIC.2019.8783300

Lu H, Seabaugh A (2014) Tunnel FET transistors: state-of-the-art. IEEE J Electron Devices Soc 2(4):44–49. https://doi.org/10.1109/JEDS.2014.2326622

Ionescu AM, Riel H (2011) Tunneling field-effect transistors as energy-efficient electronic switches. Nature 479:329–337. https://doi.org/10.1038/nature10679

Kumar J, Vishnoi R, Pandey P (2017) Tunnel field-effect transistors (TFET): modelling and simulation, John Wiley & Sons, Ltd. doi: https://doi.org/10.1002/9781119246312

Dash S, Sahoo GS, Prasad G (2016) Improved cut-off frequency for cylindrical gate TFET using source delta doping. Procedia Technol 25:450–455. https://doi.org/10.1016/j.protcy.2016.08.131

Dutta U, Soni MK, Pattanaik M (2018) Simulation study of hetero dielectric tri material gate tunnel FET based common source amplifier circuit. Int J Electron Commun 9:2263–2270. https://doi.org/10.1016/j.aeue.2018.12.004

Vakkalakula BS, Vadthiya N (2021) Design and temperature assessment of junctionless nanosheet FET for nanoscale applications. Silicon. https://doi.org/10.1007/s12633-021-01145-w

J. Hong, J. Park, J. Lee, . J. Ham and K. Park, Alpha. Particle Effect on Multi-Nanosheet Tunneling Field-Effect Transistor at 3-nm Technology Node” Micromachines, vol. 10, no. 12, p. 847, 2019. doi: https://doi.org/10.3390/MI10120847

Lee S-Y, Kim S-M, Yoon E-J, Woo-Oh C, Chung I, Park D, Kim K (2003) A Novel Multibridge-Channel MOSFET (MBCFET):Fabrication Technologies and Characteristics. IEEE Trans Nanotechnol 2 (4)

Acknowledgements

We thank the Group, department of Electronics Technology, Guru Nanak Dev University, Amritsar for their interest in this work and useful comments to draft the final form of the paper. The support of CADRE Design Systems is gratefully acknowledged. We would like to thank Guru Nanak Dev University, Amritsar and Cadre Design Systems for lab facilities and research environment to carry out this work.

Author information

Authors and Affiliations

Contributions

All authors contributed to the design and simulation. Material preparation, data collection and analysis were performed by Garima Jain, Dr. Ravinder Singh Sawhney, Dr. Ravinder Kumar and Amit Saini. The first draft of the manuscript was written by Garima Jain and all authors commented on previous versions of the manuscript. All authors read and approved the final manuscript.

Corresponding author

Ethics declarations

Conflicts of Interest/Competing Interests

the authors have declared that no competing interests exist.

Availability of Data and Material

Not applicable.

Code Availability

Not applicable.

Compliance with Ethical Standards

This study was ap-proved by the university research ethics committee. All procedures per-formed in this study follow the ethical standards of the institutional and research committee.

Consent to Participate

Not applicable.

Consent for Publication

Yes

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Jain, G., Sawhney, R.S., Kumar, R. et al. Performance Analysis of Vertically Stacked Nanosheet Tunnel Field Effect Transistor with Ideal Subthreshold Swing. Silicon 14, 5067–5074 (2022). https://doi.org/10.1007/s12633-021-01302-1

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-021-01302-1