Abstract

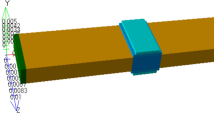

The efficiency of the integrated circuit (IC) as the reliability, speed, high production costs, and power consumption will be reduced by the nanometric size of the MOSFET transistor, the manufacturing of this device was getting into 7 nm, but the transition to 5 nm was predicted to appear in the future, to solve the decreased performance problems, the nano-double gate FinFET transistor are considered as an appropriate choice than the MOSFET device because of its improved channel control gate enabling enhanced device performance. In this paper, a comparison of the analog and RF performance of the ultra-short double gate DG-FinFET (Lg = 5 nm) with high-k material (TiO2) and the single gate fully depleted silicon on isolator (SG-FD-SOI-MOSFET) devices are investigated by using TCAD-SILVACO-Atlas simulator, the differents characteristics as leakage current, threshold voltage, Ion current, subthreshold slope, DIBL, transconductance, and GIDL are evaluated, furthermore, the channel doping has an important role in optimizing parameters of these devices, hence, the influence of channel doping concentration on the performance characteristics are investigated in this research, the results proved that the nano-short DG-FinFET device is more compatible for reduced short channel effect SCEs and improved DC and RF performances than the SG-FD-SOI-MOSFET,, an appropriate reference value of the channel doping concentration will be predicted in the future for increased the efficiency of these devices, In addition the parasitic capacitances are significantly reduced compared to the SG-FD-SOI-MOSFET, the cut off frequency (ft) and the maximum oscillator frequency (fmax) are significantly enhanced, which making DG-FinFET a suitable candidate for the RF applications and for the innovation of device manufacturing process in the future.

Similar content being viewed by others

Data Availability

no data or material has been copied from elsewhere in the proposed manuscript.

References

Phade G, Mishra BKRF (2013) Performance and Modelling of optically controlled MOSFET. Int J Electron Commun Eng(IJECE) 2:57–64

Sicard E (2017) Introducing 7-nm FinFET technology in Microwind, www.microwind.org

Mohapatra SK, Pradhan KP, Sahu PK (2012) Nanoscale SOI N-MOSFETS with different gate engineering having biaxial strained channel-a superlative study. J Electron Devices 15:1261–1268

Mohapatra SK, Pradhan KP, Sahu PK (2013) Some device design considerations to enhance the performance of DG-MOSFETs. Trans Electr Electron Mater 14(6):291–294

Lakhanpal A, Rana SB, Rana AK (2016) Review on Double-gate MOSFETs-Scaling, Operation, Challenges and Opportunities. International Journal of Advanced Research 4:367–372. https://doi.org/10.21474/IJAR01

Kumar V, Gupta R, Singh RPP, Vaid R et al (2016) Performance analysis of double gate n-FinFET using high-k dielectric materials. Int. J. Innov. Res. Sci Eng Technol 5(7):13242–13249

Cheng B, Maiti B, Samavedam S, Grant J, Taylor B, Tobin P, Mogab J (2001) Metal gates for advanced sub-90 nm SOI CMOS technology, Proc. IEEE Int. SOI Conf., p. 91–92

Rechem D, Latreche S, Gontrand C (2009) Channel length scaling and the impact of metal gate work function on the performance of double gate-metal oxide semiconductor field-effect transistors. Pramana 72(3):587–599

Shikha Bathla VK (2013) Lamba, comparison of single-gate SOI & MultiGate SOI MOSFETs. Int J Emerg Technol Adv Eng 3(3):578–580

AnkitaWagadre SM (2014) Design & performance analysis of DG-MOSFET for reduction of Short Channel effect over bulk MOSFET at 20nm. Int J Eng Res Appl 4(7):30–34 www.ijera.com

Devi S, Singh A, Lorenzo R et al. (2015) Comparative study of single gate and double gate fully depleted silicon on insulator MOSFET, in: 2015 communication, control and intelligent systems (CCIS), IEEE, 357–362

Shrivastava A, Tripathi N, Agarwal E, Singh A (2015) Comparative study of double gate SOI-MOSFET and single gate SOI MOSFET through simulation, International Journal Of Electrical And Electronics Engineers ISSN-2321-2055 (E) Http://Www.Arresearchpublication.Com IJEEE, Vol. 07, Issue 01

Faysal Al Mahmud, Md. Mydul Islam And Md. Hasan Maruf, Comparative study on single gate MOSFET and double gate MOSFET, Appl Res J, vol. 3, no 2, p. 80–86, 2017

Chinnappan U, Sanudin R (2017) Investigation of short channel effects on device performance for 60nm NMOS transistor International Research and Innovation Summit (IRIS) IOP Publishing IOP Conf. Series: Materials Science and Engineering, vol. 226, p. 012143, https://doi.org/10.1088/1757-899X/226/1/012143

Ferhati H, Douak F, Djeffal F (2017) Role of non-uniform channel doping in improving the nanoscale JL DG MOSFET reliability against the self-heating effects. Superlattices and Microstructures Superlattices and Microstructures 109:869–879. https://doi.org/10.1016/j.spmi.2017.06.009

Yadav VK, Rana AK (2012) Impact of Channel Doping on DGMOSFET Parameters in Nano Regime-TCAD Simulation. Int. J. Comput. Appl 37(11):36–41

Jiménez A, Ambrosio RC, Mireles Jr J, García D et al (2013) Analysis of threshold voltage fluctuations due to short channel and random doping effects. Superficies y vacío 26(1):1–3

Liu K-M, Peng F-I, Peng K-P et al (2014) The effects of channel doping concentration for n-type junction-less double-gate poly-Si nanostrip transistors. Semiconductor Sci Technol 29(5):055001. https://doi.org/10.1088/0268-1242/29/5/055001

Ullah K, Riaz S, Habib M, Abbas F et al (2015) Effect of channel doping concentration on the impact ionization of n-channel fully depleted SOI MOSFET. Int J Eng Works 2:1–5

Lakhanpal A, Rana SB, Rana AK (2016) International Journal of Computer Applications National Conference on Latest Initiatives& Innovations in Communication and Electronics (IICE (2016)), vol. 975, P. 8887

Rashmi Mahajan DK (2018) Gautam, analytical study of effect of channel doping on threshold voltage of metal gate high-k SiGe MOSFET. Silicon 10(1):85–90. https://doi.org/10.1007/s12633-017-9631-0

Boukortt N, Hadri B, Patanè S, Caddemi A, Crupi G (2017) Investigation on TG n-FinFET parameters by varying channel doping concentration and gate length. Silicon 9(6):885–893. https://doi.org/10.1007/s12633-016-9528-3

Fathil MFM, Tamjis N, Md Arshad MK et al. (2018) The impact of different channel doping concentrations on the performance of polycrystalline silicon nanowire field-effect transistor biosensor. In: AIP Conference Proceedings. AIP Publishing LLC, p. 020006, AIP Conference Proceedings, https://doi.org/10.1063/1.5080819

Goel A, Prakash NR (2020) The Effect of Doping on Different FET Structures: MOSFET, TFET and FinFET. Int J Innov Technol Exp Eng (IJITEE) 9. https://doi.org/10.35940/ijitee.F4051.049620

Kaharudin K et al (2019) Effect of channel length variation on analog and RF performance of Junctionless double gate vertical MOSFET. J Eng Sci Technol 14(4):2410–2430

Kumar A, Tripathi MM, Chaujar R (2018) Comprehensive analysis of sub-20 nm black phosphorus based junctionless-recessed channel MOSFET for analog/RF applications. Superlattices and Microstructures 116:171–180

Bourahla N, Hadri B, Bourahla A (2019) 3-D simulation of novel high performance of Nano-scale dual gate fin-FET inserting the high-K dielectric TiO2 at 5 nm technology. Silicon 12:1–9. https://doi.org/10.1007/s12633-019-00220-7

Kumar V, Gupta R, Singh RPP et al (2016) Performance analysis of double gate n-FinFET using high-k dielectric materials. Int. J. Innov. Res. Sci. Eng. Technol, (IJIRSET) 5(7):13242–13249. https://doi.org/10.4010/2016.1462

Shockley W, Read WT (1952) Statistics of the recombinations of holes and electrons. Phys Rev 87(5):835–842

Hall RN (1952) Electron-hole recombination in germanium. Phys rev 87(2):387

Ranka D, Rana AK, Yadav RK et al (2011) Performance analysis of FD-SOI MOSFET with different gate spacer dielectric. Int. J. Comput. Appl 18:22–27

Yan R-H, Ourmazd A, Lee LF (1992) Scaling the Si MOSFET: From bulk to SOI to bulk. IEEE Trans Electron Dev 39(7):1704–1710

Coling JP (2007) Multi-gate soi mosfets. Microelectron Eng 84(9–10):2071–2076

Kim K, Das KK, Joshi RV et al. (2004) Nanoscale CMOS circuit leakage power reduction by double-gate device. In: Proceedings of the 2004 international symposium on Low power electronics and design, 102–107

Kilchytska V, Chung TM, Olbrechts B, Vovk YA, Raskin J-P, Flandre D (2007) Electrical characterization of true silicon-on-nothing MOSFETs fabricated by Si layer transfer over a pre-etched cavity. Solid State Electron 51:1238–1244. https://doi.org/10.1016/j.sse.2007.07.021

Das R, Goswami R, Baishya (2016) Tri-gate heterojunction SOI Ge-FinFETs. Superlattices Microstrut 91:51–61. https://doi.org/10.1016/j.spmi.2015.12.039

Yang-Kyu CHOI, Daewon HA, Tsu-Jae KINK, Jeffrey BOKOR (2003) Investigation of Gate-Induced Drain Leakage (GIDL) Current in Thin Body Devices: Single-GateUltra-Thin Body ,Symmetrical Double-Gate, and Asymmetrical Double-Gate MOSFETs. Jpn J Appl Phys 42:2073–2076. https://doi.org/10.1143/JJAP.42.2073

Kumar A (2017) Effect of trench depth and gate length shrinking assessment on the analog and linearity performance of TGRC-MOSFET. Superlattice Microst 109:626–640

Nae B, Lazaro A, Iniguez B (2009) High frequency and noise model of gate-all-around MOSFETs, Electron Devices, 2009. CDE 2009. Spanish Conference on, IEEE, pp 112-115

Kumar A et Rai S (2021) Compact Modeling and Analysis of Charge and Device Capacitance for SELBOX Junctionless Transistor. Silicon, p. 1–8

Gupta N, Chaujar R (2016) Investigation of temperature variations on analog/RF and linearity performance of stacked gate GEWE-SiNW MOSFET for improved device reliability. Microelectron Reliab 64:235–241

Pandey CK, Dash D, Chaudhury S (2020) Improvement in analog/RF performances of SOI TFET using dielectric pocket. Int J Electron 107(11):1844–1860

Sarkar A, Jana R (2014) The influence of gate underlap on analog and RF performance of III–V heterostructure double gate MOSFET. Superlattice Microst 73:256–267

Acknowledgments

This work was supported by the Ministry of Higher Education and Scientific Research Algeria, We would thank the authors who motivated us to do this research and not forgot the colleagues in the ECP3M laboratory and the physics department of Mostaganem university to help us get the work done.

Author information

Authors and Affiliations

Contributions

The authors in the present manuscript were contributed to everything and they are accepted by the arrangement of their names as wrote in the paper.

Corresponding author

Ethics declarations

The authors declare that the manuscript follows ethical standards as per the guidelines provided during manuscript submission.

Consent to Participate

We agree to participate in everything suggested by the Journal.

Consent for Publication

All the authors whose names are mentioned in the present manuscript agree for publication in the silicon Journal.

Conflict of Interest

The authors declare that there is no conflict of interest in the proposed manuscript as far as the publication is concerned.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Bourahla, N., Hadri, B. & Bourahla, A. Impact of Channel Doping Concentration on the Performance Characteristics and the Reliability of Ultra-Thin Double Gate DG-FinFET Compared with Nano-Single Gate FD-SOI-MOSFET by Using TCAD-Silvaco Tool. Silicon 14, 3477–3491 (2022). https://doi.org/10.1007/s12633-021-01121-4

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-021-01121-4