Abstract

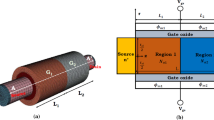

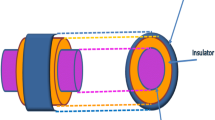

This paper presents an analytical modeling of a separated gate underlap graded N-channel FET to assess the short-channel effects. A 2D modeling scheme is employed to derive its surface potential, threshold voltage, subthreshold current and DIBL. The proposed structure includes four regions, and the potential function for each region is developed from solution of Poisson’s Equation using appropriate approximations. In order to estimate surface potential of the device, parabolic approximation scheme with geometrical approach is used in channel region to cater the influence of independently biased gates, while in source/drain underlap regions, conformal mapping is employed for the fringing field estimation. The study suggests that the independent gate bias, channel doping concentrations, spacer and other device parameters viz. underlap length, gate work function, gate oxide thickness etc. are efficacious in modulating the threshold voltage, subthreshold current and DIBL. The analytical results are compared with those obtained from TCAD device simulator, and found to match very closely. Moreover, the analytical solutions also follow the similar nature of variations as appeared in other experimental reports.

Similar content being viewed by others

References

Kedzierski J, Ieong M, Nowak E, Kanarsky TS, Zhang Y, Roy R, Boyd D, Fried D, Wong H-SP (2003) Extension and source/drain design for high-performance finFET devices. IEEE Trans Electron Devices 50(4):952–958. https://doi.org/10.1109/TED.2003.811412

Fossum JG, Chowdhury JG, Trivedi VP, King VP, Choi Y-K, An J, Yu B (2003) Physical insights on design and modeling of nanoscale FinFETs. In: IEEE Int Tech Dig Electron Devices Meeting (IEDM), pp 29.1.1-29.1.4. https://doi.org/10.1109/IEDM.2003.1269371

Singh R, Aditya K, Parihar SS, Chauhan YS, Vega R, Hook TB, Dixit A (2018) Evaluation of 10-nm Bulk finFET RF performance—conventional versus NC-finFET. Electron Devices Letter 36(8):1246–1249. https://doi.org/10.1109/LED.2018.2846

Datta A, Goel A, Cakici RT, Mahmoodi H, Lekshmanan D, Roy K (2007) Modeling and circuit synthesis for independently controlled double gate finFET devices. IEEE Trans Electron Devices 26(11):1957–1966. https://doi.org/10.1109/TCAD.2007.896320

Cakici T, Mahmoodi H, Mukhopadhyay S, Roy K (2005) Independent gate skewed logic in double gate SOI technology. In: Proc IEEE Int SOI Conf, pp 83–84. https://doi.org/10.1109/SOI.2005.1563543

Wang T, Cui X, Ni Y, Yu D, Cui X (2018) Evaluation of dynamic-adjusting threshold-voltage scheme for low-power finFET circuits. IEEE Trans VLSI Syst 26(10):1922–1929. https://doi.org/10.1109/TVLSI.2018.2842067

Possani VN, Reis AI, Ribas RP, Marques FS, da Rosa LS (2017) Transistor count optimization in IG finFET network design. IEEE Trans on Computer-Aided Design of Integrated Circuits and Systems 36(9):1483–1496. https://doi.org/10.1109/TCAD.2016.2629451

Bansal A, Roy K (2007) Analytical subthreshold potential distribution model for gate underlap Double-Gate MOS transistor. IEEE Trans Electron Devices 54(7):1793–1798. https://doi.org/10.1109/TED.2007.898042

Vaddi R, Agarwal RP, Dasgupta S (2012) Compact modeling of a generic Double-Gate MOSFET with Gate–S/D underlap for subthreshold operation. IEEE Trans Electron Devices 59(10):2846–2849. https://doi.org/10.1109/TED.2012.2208464

Kuo JB, Sun EC (2004) A compact threshold voltage model for gate misalignment effect of DG FD SOI nMOS devices considering fringing electric field effects. IEEE Trans Electron Devices 51(4):587–596

Trivedi V, Fossum JG, Chowdhury MM (2005) Nanoscale finFETs with gate-source/drain underlap. IEEE Trans Electron Devices 52(1):56–62. https://doi.org/10.1109/TED.2004.841333

Bansal A, Paul BC, Roy K (2004) Impact of gate underlap on gate capacitance and gate tunnelling current in 16 nm DGMOS devices. Proc IEEE SOI Conf, pp 94–95. https://doi.org/10.1109/SOI.2004.1391570

Tanaka K, Takeuchi K, Hane M (2005) Practical finFET design considering GIDL for LSTP (low standby power) devices. IEDM Tech Dig, pp 980–983. https://doi.org/10.1109/IEDM.2005.1609526

Shenoy RS, Saraswat KC (2003) Optimization of extrinsic source/drain resistance in ultrathin body double-gate FETs. IEEE Trans Nanotechnol 2(4):265–270. https://doi.org/10.1109/TNANO.2003.820780

Magnone P, Crupi F, Giusi G, Pace C, Simoen E, Claeys C, Pantisano L, Maji D, Ramgopal Rao V, Srinivasan P (2009) 1/F noise in drain and gate current of MOSFETswith high-k gate stacks. IEEE Trans Device Mater Reliab 9(2):180–189. https://doi.org/10.1109/TDMR.2009.2020406

Chen X, Ouyang QC, Wang G, Banerjee SK (2002) Improved hot-carrier and short-channel performance in vertical nMOSFETs with graded channel doping. IEEE Trans Electron Devices 49(11):1962–1968. https://doi.org/10.1109/TED.2002.804697

Agrawal B, De VK, Meindl JD (1996) Device parameter optimization for reduced short-channel effects in retrograde doping MOSFETs. IEEE Trans Electron Devices 43(2):365–368. https://doi.org/10.1109/16.481743

Yu B, Wann CHJ, Nowak ED, Noda K, Hu C (1997) Short-channel effect improved by lateral channel engineering in deep-submicronmeter MOSFETs. IEEE Trans Electron Devices 44(4):627–634. https://doi.org/10.1109/16.563368

Cheng B, Inani A, Rao R, Woo JCS (1999) Channel engineering for high-speed sub-1.0-V power supply deep submicron CMOS. Symp VLSI Technol, pp 69–70. https://doi.org/10.1109/VLSIT.1999.799344

Chattopadhyay A, Dutta A, Kundu A, Sarkar CK (2016) Influence on the analog/RF Performance in Graded Channel Gate Stack DG-MOSFETs. ICDCS, pp 167–169. https://doi.org/10.1109/ICDCSyst.2016.7570653

Chattopadhyay A, Das R, Dasgupta A, Kundu A, Sarkar CK (2017) Effect of channel engineering on analog/RF performance of underlapped gatestack DG-MOSFET in sub-20nm regime. DevIC, pp 299–302. https://doi.org/10.1109/DEVIC.2017.8073956

Sharma RK, Gupta M, Gupta RS (2011) TCAD Assessment of device design technologies for enhanced performance of nanoscale DG MOSFET. IEEE Trans Electron Devices 58(9):2936–2943. https://doi.org/10.1109/TED.2011.2160065

Chattopadhyay A, Das R, Dasgupta A, Kundu A, Sarkar CK (2017) A linearity based comparison between symmetric and asymmetric lateral diffusion for a 22 nm Underlapped DG-MOSFET. Superlattices and Microstructures, pp 69–82. https://doi.org/10.1016/j.spmi.2017.03.056

Koley K, Dutta A, Saha SK, Sarkar CK (2015) Analysis of high-k spacer asymmetric Underlap DG-MOSFET for SOC application. IEEE Trans Electron Devices 62(6):1733–1738. https://doi.org/10.1109/TED.2015.2397699

Fossum JG, Zhou Z, Mathew L, Nguyen B-Y (2010) SOI Versus bulk-silicon nanoscale finFETs. Solid-State Electron 54(2):86–89. https://doi.org/10.1016/j.sse.2009.12.002

Choi JH, Kim TK, Moon JM, Yoon YG, Hwang BW, Kim DH, Lee SH (2014) Origin of device performance enhancement of junctionless accumulation-mode (JAM) bulk finFETs with high- gate spacers. IEEE Electron Device Lett 35(12):1182–1184. https://doi.org/10.1109/LED.2014.2364093

Gundapaneni S, Ganguly S, Kottantharayil A (2011) Enhanced electrostatic integrity of short-channel junctionless transistors with high-k spacers. IEEE Electron Dev Lett 32(10):1325–1327. https://doi.org/10.1109/LED.2011.2162309

Chattopadhyay A, Dasgupta A, Das R, Kundu A, Sarkar CK (2017) Effect of spacer dielectric engineering on Asymmetric Source Underlapped Double Gate MOSFET using Gate Stack. Superlattices and Microstructures, pp 87–95. https://doi.org/10.1016/j.spmi.2016.11.024

Sachid AB, Chen M-C, Hu C (2016) FinFET with high- spacers for improved drive current. IEEE Trans Electron Devices 37(7):835–838. https://doi.org/10.1109/LED.2016.2572664

Sachid AB, Chen MC, Hu C (2017) Bulk finFET with low- spacers for continued scaling. IEEE Trans Electron Devices 67(4):1861–1864. https://doi.org/10.1109/TED.2017.2664798

Han JW, Kim CJ, Choi YK (2008) Universal potential model in tied and separated double-gate MOSFETs with consideration of symmetric and asymmetric structure. IEEE Trans Electron Devices 55(6):1472–1479. https://doi.org/10.1109/TED.2008.922492

Suzuki K, Sugii T (1995) Analytical model for n + -p + double-gate SOI MOSFET’s. IEEE Trans Electron Devices 42(11):1940–1948

Young KK (Feb. 1989) Short-channel effect in fully depleted SOI MOSFETs. IEEE Trans Electron Devices 36(2):399–402. https://doi.org/10.1109/16.19942

Dubey SK, Tiwari PK, Jit S (2010) A two-dimensional model for the potential distribution and threshold voltage of short-channel double-gate metal-oxide-semiconductor field-effect transistors with a vertical Gaussian-like doping profile. J Appl Phys 108(3):034518–1-034518-7. https://doi.org/10.1063/1.3460796

Goel E, Kumar S, Singh K, Singh B, Kumar M, Jit S (2016) 2-D analytical modeling of threshold voltage for graded-channel dual-material double-gate MOSFETs. IEEE Trans Electron Devices 63 (3):966–973. https://doi.org/10.1109/TED.2016.2520096

Jaiswal N, Kranti A (2018) A model for Gate-Underlap-Dependent short channel effects in junctionless MOSFET. IEEE Trans Electron Devices 65(3):881–887. https://doi.org/10.1109/TED.2018.2796602

Liang X, Taur Y (2004) A 2-D analytical solution for SCEs in DG MOSFETs. IEEE Trans Electron Devices 51(9):1385–1391. https://doi.org/10.1109/TED.2004.832707

Mollah SA (2012) Introduction to numerical analysis

Holtij T, Graef M, Hain FM, Kloes A, Iñíguez B (2014) Compact model for short-channel junctionless accumulation mode double gate MOSFETs. IEEE Trans Electron Devices 61(2):288–299. https://doi.org/10.1109/TED.2013.2281615

Sentaurus Device User Guide, Synopsys, Inc., Mountain View, CA, USA, 2010

International Technology Roadmap for Semiconductor, 2012

Arora ND, Gildenblat GS (Feb. 1987) A Semi-Empirical model of the MOSFET inversion layer mobility for Low-Temperature operation. IEEE Trans Electron Devices 34(1):89–93. https://doi.org/10.1109/T-ED.1987.22889

Lombardi C, Manzini S, Saporito A, Vanzi M (1988) A physically based mobility model for numerical simulation of nonplanar devices. IEEE Trans CAD 7(11):89–93. https://doi.org/10.1109/43.9186

Ferain I, Colinge CA, Colinge J-P (2011) Multigate transistors as the future of classical metal–oxide–semiconductor field-effect transistors. Nature 479:310–316. https://doi.org/10.1038/nature10676

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Appendices

Appendix A

Appendix B

The Vfg dependent coeffecients are expressed as,

The expressions of αi; i = 23 to 39 are given in Appendix A. We finally get the following equation of Vfg, \(\alpha _{40}V^{2}_{fg}-\alpha _{41}V_{fg}+\alpha _{42}=0\) and its solution as,

Appendix C

The Vfg dependent coeffecients are expressed as,

The quadratic equation of Vfg is expressed as, \(\alpha _{49}V^{2}_{fg}+ \ \ \alpha _{50}V_{fg}+\alpha _{51}=0\). The threshold voltage is obtained as,

Rights and permissions

About this article

Cite this article

Chattopadhyay, A., Bose, C. & Sarkar, C.K. Compact Modeling of Graded N-Channel Independent Gate FET with Underlaps, Spacer and S/D Straggle for Low Power Application. Silicon 13, 375–387 (2021). https://doi.org/10.1007/s12633-020-00424-2

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-020-00424-2