Abstract

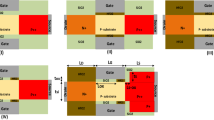

In this paper, the presence of source stack and heterogeneous gate dielectric material in the structure of an n-channel tunnel FET (TFET) is investigated. P+ type source stack above the source region causes an increase in the electric field which in turn leads to more band bending in the energy band diagram of the proposed structure. Therefore, the effective width of tunneling region decreases and as a result electron Band to Band Tunneling (BTBT) rate enhances. It is also shown that incorporating hetero gate dielectric material can further enhance BTBT rate in the source-channel region and it becomes more intensive as the permittivity of high-k dielectric is increased. The hetero gate structure which is utilized is a combination of SiO2 and a high-k material. Our simulation results indicate that the presence of SiO2 in the drain side minimizes ambipolar current at negative gate voltages. Simulations are performed using Silvaco Atlas TCAD for a channel length of 50 nm using nonlocal tunneling model.

Similar content being viewed by others

References

Ramezani Z, Orouji AA (2017) Amended electric field distribution: a reliable technique for electrical performance improvement in nano scale SOI MOSFETs. J Electron Mater 46:2269–2281

Taur Y, Ning TH (2009) Fundamentals of modern VLSI devices, 2nd edn. Cambridge University Press, New York

Weste NH, Harris D (2011) CMOS VLSI design: a circuits and systems perspective, 4th edn. Pearson Education, Boston

Karbalaei M, Dideban D (2016) A novel silicon on insulator MOSFET with an embedded heat pass path and source side channel doping. Superlattice Microst 90:53–67

Chander S, Baishya S (2016) Two-dimensional model of a heterojunction silicon-on-insulator tunnel field effect transistor. Superlattice Microst 90:176–183

Shahnazarisani H, Mohammadi S (2015) Simulation analysis of a novel fully depleted SOI MOSFET: electrical and thermal performance improvement through trapezoidally doped channel and silicon–nitride buried insulator. Physica E 69:27–33

Orouji AA, Anvarifard MK (2013) SOI MOSFET with an insulator region (IR-SOI): a novel device for reliable nanoscale CMOS circuits. Mater Sci Eng B 178:431–437

Mehrad M, Ghadi ES (2017) C-shape silicon window nanoMOSFET for reducing the short channel effects. In 2017 joint international EUROSOI workshop and international conference on ultimate integration on silicon (EUROSOI-ULIS), Athens, pp 164–167. https://doi.org/10.1109/ULIS.2017.7962572

Choi WY, Song JY, Lee JD, Park YJ, Park B-G (2005) 70-nm impact-ionization metal-oxide-semiconductor (I-MOS) devices integrated with tunneling field-effect transistors (TFETs). In 2007 IEEE international electron devices meeting (IEDM), Washington, pp 955–958. https://doi.org/10.1109/IEDM.2005.1609519

Jain P, Prabhat V, Ghosh B (2015) Dual metal-double gate tunnel field effect transistor with mono/hetero dielectric gate material. J Comput Electron 14:537–542

Kyung C-M (2016) Nano devices and circuit techniques for low-energy applications and energy harvesting. Springer Science & Business Media, Dordrecht

Choi WY, Lee HK (2016) Demonstration of hetero-gate-dielectric tunneling field-effect transistors (HG TFETs). Nano Converg 3:13

S. I.Association (2015) International technology roadmap for semiconductors, https://www.semiconductors.org/resources/2015-international-technology-roadmap-for-semiconductors-itrs. Accessed 12 Sept 2019.

Boucart K, Ionescu AM (2007) Double-gate tunnel FET with high-$\kappa $ gate dielectric. IEEE transactions on electron devices 54:1725–1733

Verhulst AS, Sorée B, Leonelli D, Vandenberghe WG, Groeseneken G (2010) Modeling the single-gate, double-gate, and gate-all-around tunnel field-effect transistor. J Appl Phys 107:024518

Lu H, Seabaugh A (2014) Tunnel field-effect transistors: state-of-the-art. IEEE J Electron Devi 2:44–49

Jang J-S, Choi W-Y (2011) Ambipolarity factor of tunneling field-effect transistors (TFETs). JSTS: Journal of Semiconductor Technology and Science 11:272–277

Krishnamohan T, Kim D, Raghunathan S, Saraswat K (2008) Double-gate strained-Ge heterostructure tunneling FET (TFET) with record high drive currents and ≪60mV/dec subthreshold slope. In 2008 IEEE international electron devices meeting (IEDM), San Francisco, pp 1–3. https://doi.org/10.1109/IEDM.2008.4796839

Kim SH, Kam H, Hu C, Liu T-J K (2009) Germanium-source tunnel field effect transistors with record high ION/IOFF. In 2009 symposium on VLSI technology, Honolulu, pp 178–179, 15–17 June 2009

D. S. Yadav, D. Sharma, B. R. Raad, and V. Bajaj, “Dual workfunction hetero gate dielectric tunnel field-effect transistor performance analysis,” in Advanced Communication Control and Computing Technologies (ICACCCT), 2016 International Conference on, 2016, pp. 26–29

Nagavarapu V, Jhaveri R, Woo JC (2008) The tunnel source (PNPN) n-MOSFET: a novel high performance transistor. IEEE Transactions on Electron Devices 55:1013–1019

Naderi A, Tahne BA (2016) T-CNTFET with gate-drain overlap and two different gate metals: a novel structure with increased saturation current. ECS Journal of Solid State Science and Technology 5:M3032–M3036

Naderi A, Ahmadmiri SA (2016) Attributes in the performance and design considerations of asymmetric drain and source regions in carbon nanotube field effect transistors: quantum simulation study. ECS Journal of Solid State Science and Technology 5:M63–M68

Choi WY, Lee W (2010) Hetero-gate-dielectric tunneling field-effect transistors. IEEE transactions on electron devices 57:2317–2319

Verhulst AS, Vandenberghe WG, Maex K, Groeseneken G (2007) Tunnel field-effect transistor without gate-drain overlap. Appl Phys Lett 91:053102

Madan J, Chaujar R (2017) Gate drain underlapped-PNIN-GAA-TFET for comprehensively upgraded analog/RF performance. Superlattices Microst 102:17–26

Vijayvargiya V, Vishvakarma SK (2014) Effect of drain doping profile on double-gate tunnel field-effect transistor and its influence on device RF performance. IEEE Trans Nanotechnol 13:974–981

Ahish S, Sharma D, Kumar YBN, Vasantha MH (2015) Performance enhancement of novel InAs/Si hetero double-gate tunnel FET using Gaussian doping. IEEE Trans on Electron Devices 63:288–295

Naderi A, Ghodrati M (2018) An efficient structure for T-CNTFETs with intrinsic-n-doped impurity distribution pattern in drain region. Turk J Electr Eng Comput Sci 26:2335–2346

Anvarifard MK, Orouji AA (2018) Proper electrostatic modulation of electric field in a reliable nano-SOI with a developed channel. IEEE Trans on Electron Devices 65:1653–1657

Anvarifard MK (2019) Junctionless transistor with pulsed shaped dielectric (PSD-JNL): an absorbing structure for nanoscale aims. ECS J Solid State Sci Technol 8:N5–N12

Colinge J-P (2004) Silicon-on-insulator technology: materials to VLSI, 3rd edn. Springer Science & Business Media, New York

Atlas DS (2016) Atlas user’s manual. Silvaco international software, Santa Clara, https://www.silvaco.com. Accessed 12 Sept 2019

Shaker A, El Sabbagh M, El-Banna MM (2017) Influence of drain doping engineering on the ambipolar conduction and high-frequency performance of TFETs. IEEE Trans Electron Devices 64:3541–3547

Solomon PM, Jopling J, Frank DJ, D’Emic C, Dokumaci O, Ronsheim P et al (2004) Universal tunneling behavior in technologically relevant P/N junction diodes. J Appl Phys 95:5800–5812

Boucart K, Ionescu AM (2007) Length scaling of the double gate tunnel FET with a high-k gate dielectric. Solid State Electron 51:1500–1507

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Karbalaei, M., Dideban, D. Influence of Source Stack and Heterogeneous Gate Dielectric on Band to Band Tunneling Rate of Tunnel FET. Silicon 12, 1811–1817 (2020). https://doi.org/10.1007/s12633-019-00272-9

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-019-00272-9