Abstract

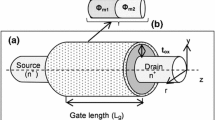

This work investigates design consideration of Gate Electrode Workfunction Engineered (GEWE) silicon nanowire MOSFET at room temperature. It is perceived from the results that the parasitic capacitances are higher in the deep inversion region, however; the coupling of parasitic capacitance is weak in GEWE-SiNW due to lower gate metal workfunction at the drain end. Moreover, the influence of drain voltage on Cgs is very less owing to constant depletion charges at the source side which results in almost constant value of Cgs with the change in Vds. With tuning of channel length (Lg) and oxide thickness (tox), the effect of capacitances in GEWE-SiNW further reduces significantly due to quantization effect at such scaled dimensions. Furthermore, Transconductance Frequency Product (TFP), Energy Delay Product (EDP) and Gain Bandwidth Product (GBP) have also been calculated with an aim to analyze the device DC and switching performance as they are directly or indirectly linked with parasitic capacitance. Calibrated 3D simulations validate that the GEWE-SiNW MOSFET exhibit 2.57, 34.5 and 2.75 times improvement in TFP, EDP and GBP respectively in comparison to SiNW in the linear region.

Similar content being viewed by others

References

Borkar S (1999) Design challenges of technology scaling. IEEE micro 19(4):23–29

Kuhn KJ (2011) Moore’s crystal ball: device physics and technology past the 15nm generation. Microelectron Eng 88(7):1044–1049

Kranti A, Armstrong GA (2006) Engineering source/drain extension regions in nanoscale double gate (DG) SOI MOSFETs: analytical model and design considerations. Solid State Electron 50(3):437–447

Kumar A, Tripathi M, Chaujar R (2018) Comprehensive analysis of sub-20 nm black phosphorus based junctionless-recessed channel MOSFET for analog/RF applications. Superlattice Microst 116:171–180

Kumar A (2017) Effect of trench depth and gate length shrinking assessment on the analog and linearity performance of TGRC-MOSFET. Superlattice Microst 109:626–640

Kumar A, Tripathi M, Chaujar R (2018) Reliability issues of in 2 O 5 Sn gate electrode Recessed Channel MOSFET: impact of Interface trap charges and temperature. IEEE Transactions on Electron Devices 65(3):860–866

Auth CP, Plummer JD (1997) Scaling theory for cylindrical, fully-depleted, surrounding-gate MOSFET's. Electron Device Letters, IEEE 18(2):74–76

Sarkar A, De S, Dey A, Sarkar CK (2012) Analog and RF performance investigation of cylindrical surrounding-gate MOSFET with an analytical pseudo-2D model. J Comput Electron 11(2):182–195

C.-Y. Chang, C.-H. Chang, C.-H. Hou, K.-L. Lin, K.-Y. Lee, X.-F. Yu, C.-O. Chui, Semiconductor devices, Finfet devices and methods of forming the same, US Patent App 15/876,223, 2019

K. Cheng, D.D. Lu, X. Miao, T. Yamashita, FinFET with reduced parasitic capacitance, Google patents, 2019

A. Abdelmoneam, B. Iñiguez, M. Fedawy, Compact modelling of quantum confinement in III-V gate all around nanowire MOSFET, 2018 Spanish Conference on Electron Devices (CDE), IEEE, 2018, pp. 1–4

Muscato O, Castiglione T, Coco A (2019) Hydrodynamic modeling of electron transport in gated silicon nanowires transistors, Atti della Accademia Peloritana Dei Pericolanti-Classe di Scienze Fisiche. Matematiche e Naturali 97(S1):18

Yang B, Buddharaju K, Teo S, Singh N, Lo G, Kwong D (2008) Vertical silicon-nanowire formation and gate-all-around MOSFET. IEEE Electron Device Letters 29(7):791–794

Pal HS, Cantley KD, Ahmed SS, Lundstrom MS (2008) Influence of bandstructure and channel structure on the inversion layer capacitance of silicon and GaAs MOSFETs. IEEE Transactions on Electron Devices 55(3):904–908

Luryi S (1988) Quantum capacitance devices. Appl Phys Lett 52(6):501–503

Kumar MJ, Chaudhry A (2004) Two-dimensional analytical modeling of fully depleted DMG SOI MOSFET and evidence for diminished SCEs. IEEE Transactions on Electron Devices 51(4):569–574

Long W, Chin KK (1997) Dual material gate field effect transistor (DMGFET), Electron devices meeting, 1997. IEDM'97. Technical digest. International, IEEE:549–552

Gupta N, Chaujar R (2016) Optimization of high-k and gate metal workfunction for improved analog and intermodulation performance of gate stack (GS)-GEWE-SiNW MOSFET. Superlattice Microst 97:630–641

Gupta N, Chaujar R (2016) Influence of gate metal engineering on small-signal and noise behaviour of silicon nanowire MOSFET for low-noise amplifiers. Applied Physics A 122(8):1–9

Takagi S-i, Toriumi A (1995) Quantitative understanding of inversion-layer capacitance in Si MOSFET's. IEEE Transactions on Electron Devices 42(12):2125–2130

Chaudhry A, Roy J (2010) MOSFET models, quantum mechanical effects and modeling approaches: a review. JSTS: J Semiconductor Tech Sci 10(1):20–27

Iannaccone G, Curatola G, Fiori G Effective Bohm quantum potential for device simulators based on drift-diffusion and energy transport, simulation of Semiconductor processes and devices 2004, Springer2004, pp 275–278

Gupta N, Chaujar R Implications of transport models on the analog performance of gate electrode Workfunction engineered (GEWE) silicon nanowire MOSFET, devices. Circuits and systems (ICDCS), 2014 2nd international conference on, IEEE, 2014, pp 1–5

I. SILVACO, ATLAS User’s manual, Santa Clara, CA, Ver 5 (2016)

Suk SD, Lee S-Y, Kim S-M, Yoon E-J, Kim M-S, Li M, Oh CW, Yeo KH, Kim SH, Shin D-S (2005) High performance 5 nm radius twin silicon nanowire MOSFET (TSNWFET): fabrication on bulk Si wafer, characteristics, and reliability. IEDM Tech Dig:717–720

Moon D-I, Choi S-J, Kim C-J, Kim J-Y, Lee J-S, Oh J-S, Lee G-S, Park Y-C, Hong D-W, Lee D-W (2011) Silicon nanowire all-around gate MOSFETs built on a bulk substrate by all plasma-etching routes. IEEE Electron Device Letters 32(4):452–454

Kumar A, Tripathi MM, Chaujar R (2018) In2O5Sn based transparent gate recessed channel MOSFET: RF small-signal model for microwave applications. AEU Int J Electron Commun 93:233–241

Kumar A, Tripathi M, Chaujar R (2017) Investigation of parasitic capacitances of In2O5Sn gate electrode recessed channel MOSFET for ULSI switching applications. Microsyst Technol 23(12):5867–5874

Gupta N, Kumar A, Chaujar R (2015) Impact of device parameter variation on RF performance of gate electrode workfunction engineered (GEWE)-silicon nanowire (SiNW) MOSFET. J Comput Electron 14:798–810

Acknowledgments

The authors would be grateful to Microelectronics Research Lab, Department of Applied Physics, Delhi Technological University and ADGITM (Formerly Northern India Engineering College) for providing the required aid to carry out this research work.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Gupta, N., Kumar, A. & Chaujar, R. Design Considerations and Capacitance Dependent Parametric Assessment of Gate Metal Engineered SiNW MOSFET for ULSI Switching Applications. Silicon 12, 1501–1510 (2020). https://doi.org/10.1007/s12633-019-00246-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-019-00246-x