Abstract

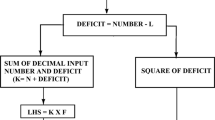

In current day situation we come across numerous mathematical challenges. This could be overwhelmed by the Vedic Mathematics. Vedic Mathematics is an ancient approach to solve problems in a rapid manner. In this paper the design of a novel Vedic square and multiplier architecture based on Yavadunam Sutra is proposed. Yavadunam is a squaring sutra of the Vedic Mathematics. We have designed a generic architecture for this squaring sutra and have designed a high speed Vedic binary multiplier architecture using the principles of Yavadunam sutra. The proposed multiplier offers significant improvement in speed. Xilinx Spartan FPGA is used to design and realize the architecture and the Synopsys device with 90 nm and 180 nm technology is used to synthesize the same.

Similar content being viewed by others

References

Akanksha K and Shobha S 2015 Applications of Vedic multiplier designs-a review. In: Proceedings of the 4th international conference on reliability, infocom technologies and optimization (trends and future directions). pp. 1–6

Deepa A and Marimuthu C N 2017 A high speed VLSI architecture of a pipelined reed solomon encoder for data storage in communication systems. Asian J. Res. Soc. Sci. Hum. 7(2): 228–238

Neeraj M and Asmita H 2013 An advancement in the N*N multiplier architecture realization via the ancient Indian Vedic mathematics. Int. J. Electron. Commun. Comput. Eng. 4(2): 544–548

Jinesh S, Ramesh P and Thomas J 2015 Implementation of 64 bit high speed multipliers for DSP application-based on vedic mathematics. In: Proceedings TENCON 2015 IEEE region 10 conference. pp. 1–5

Arushi S, Dheeraj J, Sanjay J, Kumkum V and Swati K 2012 Compare Vedic multipliers with conventional hierarchical array of array multiplier. Int. J. Comput. Technol. Electron. Eng. 2(6): 52–55

Nisha Angeline M and Valarmathy S 2016 Implementation of N-bit binary multiplication using N−1 bit multiplication based on Nikhilam Sutra principles and bit reduction. Transylv. Rev. 24: 982–992

Richa S, Manjit K and Gurmohan S 2015 Design and FPGA implementation of optimized 32-bit Vedic multiplier and square architectures In: Proceedings of the international conference on industrial instrumentation and control. pp. 960–964

Sriraman L, Saravana Kumar K and Prabakar T N 2013 Design and FPGA implementation of binary squarer using Vedic mathematics In: Proceedings of the 4th international conference on computing, communication and networking technologies. pp. 1–5

Vaijyanath K, Linganagouda K and Subhash K 2013 Low power square and cube architectures using Vedic Sutras. In: Proceedings of the 5th international conference on signal and image processing. pp. 354–358

Jagadguru Swami Sri Bharati Krishna Tirthaji Maharaj 2009 Vedic mathematics. Delhi: Agarwala V S Delhi Motilal Banarasidass Publishers Pvt. Ltd

Deepa A and Marimuthu C N 2018 High speed VLSI architecture for squaring binary numbers using Yavadunam Sutra and bit reduction technique. Int. J. Appl. Eng. Res. 13(6): 4471–4474

Deepa A and Marimuthu C N 2017 A modified multiplier architecture using Yavadunam: a squaring algorithm of Vedic mathematics. Perspectivas em ciencia da Informacao 22(3): 322–332

Wang J S, Kuo C N and Yang T H 2004 Low power fixed width array multipliers. In: Proceedings of international symposium on low power electronics and design. pp. 307–312

Wallace C S 1964 A suggestion for a fast multiplier. IEEE Trans. Electron. Comput. 13(1): 14–17

Hussain R K and Sah 2015 Performance comparison of Wallace multiplier architectures. Int. J. Innov. Res. Sci. Eng. Technol. 4(1): 2347–6710

Dadda L 1965 Some schemes for parallel multipliers. Alta Freq. 34: 349–356

Ramesh A P 2011 Implementation of dadda and array multiplier architecture using tanner tool. IJCSET 2(2): 28–41

Anitha R, Nelapati A, Lincy Jesima W and Bagyaveereswaran V 2012 Comparative study of high performance Braun’s multiplier using FPGAs. IOSR J. Electron. Commun. Eng. 1(4): 33–37

Arish S and Sharma R K 2015 An efficient binary multiplier design for high speed applications using Karatsuba algorithm and Urdhva-Tiryagbhyam algorithm. In: Proceedings of the 2015 global conference on communication technologies. pp. 192–196

Harish Kumar Ch 2013 Implementation and analysis of power, area and delay of array, Urdhva, Nikhilam Vedic multipliers. Int. J. Sci. Res. Publ. 3(1): 1–5

Mottaghi Dastjerdi M, Afzali Kusha A and Pedram M 2014 BZ-FAD: a low-power low-area multiplier based on shift-and-add architecture. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 17(2): 267–386

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Deepa, A., Marimuthu, C.N. Design of a high speed Vedic multiplier and square architecture based on Yavadunam Sutra. Sādhanā 44, 197 (2019). https://doi.org/10.1007/s12046-019-1180-3

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s12046-019-1180-3