Abstract

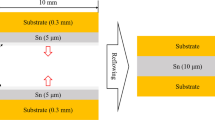

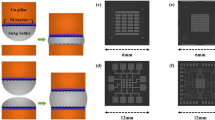

Structural integrity of circuits is greatly dependent on interfacial microstructure. In this paper, the status of the current understanding of various interfaces appearing in lead-free soldering is reviewed, and recent data on interfaces in electronic interconnections, primarily analyzed by transmission electron microscopy (TEM), is presented. The compound Cu6Sn5 is formed, as localized precipitates attach to the interface of a Cu substrate with Sn plating, even in an as-received condition. After long-time exposure at room temperature, it grows into a Cu6Sn5 layer along the interface. When the temperature is raised slightly or Sn in a plating layer is consumed by the reaction, a Cu3Sn layer can grow between a Cu6Sn5 layer and a Cu substrate. In soldering, most Sn alloys involving pure Sn, Sn-Ag, or their ternary alloys form two intermetallic compounds, e.g., Cu6Sn5 and Cu3Sn, on a Cu substrate, with the former much thicker than the latter. The Ni plating forms Ni3Sn4/Ni3Sn2 double layers at the interface with Sn alloys in soldering with the latter layer very much thinner. In contrast, Fe-42Ni alloy forms (Fe,Ni)Sn2 double layers by the reaction with Sn and Sn-Ag(-Cu). When Zn becomes one of the elements of the solder, Zn first reacts with a substrate. Thus, the Sn-Zn alloy forms different intermetallic compounds at an interface with Cu, i.e., the CuZn/Cu5Zn8 double layers. The Sn-Zn alloy also forms a thin AuZn layer when thin Au plating is on a substrate.

Similar content being viewed by others

References

K. Suganuma, Current Opinion Solid State Mater. Sci. 5, 555 (2001).

K.N. Tu and K. Zeng, Mater. Sci. Eng. R34, 1 (2001).

H.K. Kim, H.K. Liou, and K.N. Tu, Appl. Phys. Lett. 66, 2237 (1995).

T.B. Massalski, H. Okamoto, P.R. Subramanian, and L. Kacprzak, Binary Alloy Phase Diagrams, 2nd ed. (Materials Park, OH: ASM International, 1990), pp. 1481–1483.

N. Sarafianos, Mater. Sci. Technol. 3, 66 (1987).

W.K. Choi and H.M. Lee, J. Electron. Mater. 28, 1251 (1999).

K.S. Kim, S.H. Huh, and K. Suganuma, Mater. Sci. Eng. A333, 106 (2002).

D. Frear, D. Gravis, and J.W. Morris, J. Electron. Mater. 16, 181 (1987).

C.H. Ho, Y.M. Chen, and Y.M. Kao, J. Electron. Mater. 28, 1231 (1999).

G. Ghosh, J. Electron. Mater. 28, 1238 (1999).

C.W. Hwang, J.G. Lee, K. Suganuma, and H. Mori, J. Electron. Mater. 32, 52 (2003).

P. Liu, Z. Xu, and J.K. Shang, Metall. Mater. Trans. A 31A, 2857 (2000).

J.W. Jang, P.G. Kim, K.N. Tu, D.R. Frear, and P. Thompson, J. Appl. Phys. 85, 8456 (1999).

Y. Kariya, Y. Hirata, and M. Otsuka, J. Electron. Mater. 28, 1263 (1999).

C.W. Hwang, K. Suganuma, J.G. Lee, and H. Mori, J. Mater. Res. 18, 1202 (2003).

S.W. Yoon, J.R. Soh, H.M. Lee, H.M. Kim, and B.J. Lee, Acta Mater. 45, 951 (1997).

S.P. Yu, M.H. Hon, and M.C. Wang, J. Electron. Mater. 29, 237 (2000).

K. Suganuma, K. Niihara, T. Shoutoku, and Y. Nakamura, J. Mater. Res. 13, 2859 (1998).

H.M. Lee, S.W. Yoon, and B.J. Lee, J. Electron. Mater. 27, 1161 (1998).

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Hwang, CW., Kim, KS. & Suganuma, K. Interfaces in lead-free soldering. J. Electron. Mater. 32, 1249–1256 (2003). https://doi.org/10.1007/s11664-003-0019-0

Received:

Accepted:

Issue Date:

DOI: https://doi.org/10.1007/s11664-003-0019-0