Abstract

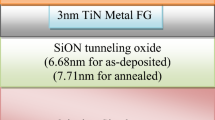

Charge trap flash (CTF) memory devices are candidates to replace NAND flash devices. In this study, Pt/Al2O3/LaAlO3/SiO2/Si multilayer structures with lanthanum aluminate charge traps were fabricated for nonvolatile memory device applications. An aluminum oxide film was used as a blocking oxide for low power consumption in the program/erase operation and to minimize charge transport through the blocking oxide layer. The thickness of SiO2 as tunnel oxide layer was varied from 30 to 50 Å. Thicknesses of oxide layers were confirmed by high resolution transmission electron microscopy (HRTEM) and all the samples showed amorphous structure. From the C–V measurement, a maximum memory window of 3.4 V was observed when tunnel oxide thickness was 40 Å. In the cycling test for reliability, the 30 Å tunnel oxide sample showed a relatively large memory window reduction by repeated program/erase operations due to the high electric field of ~10 MV/cm through tunnel oxide. The other samples showed less than 10% loss of memory window during 104 cycles.

Similar content being viewed by others

References

Kim KN, Lee SY (2007) Microelectron Eng 84:1976

Burr GW, Kurdi BN, Scott JC, Lam CH, Gopalakrishnan K, Shenoy RS (2008) IBM J Res Dev 52:449

White MH, Adams DA, Bu J (2000) IEEE Circuits Device 16(4):22

Felix JA, Schwank JR, Fleetwood DM, Shaneyfelt MR, Gusev EP (2004) Microelectron Reliab 44:563

Pan TM, Yu TY (2008) Appl Phys Lett 92:112906

Tan YN, Chim WK, Cho BJ, Choi WK (2004) IEEE Trans Electron Devices 51(7):1143

Xiong K, Robertson J, Clark SJ (2006) Appl Phys Lett 89:022907

Jeon S, Han JH, Lee JH, Choi S, Hwang H, Kim C (2005) IEEE Trans Electron Devices 52(12):2654

Alvarado SF, Mattina FL, Bednorz JG (2007) Appl Phys A 89(1):85

Kang JM, Keem KH, Jeong DY, Park MY, Whang DM, Kim SS (2008) J Mater Sci 43(10):3424. doi:10.1007/s10853-007-2310-6

International Technology Roadmap for Semiconductors, 2007 Edition

Sandhya C, Oak AB, Chattar N, Joshi AS, Ganguly U, Olsen C, Seutter SM, Date L, Hung R, Vasi J, Mahapatra S (2009) IEEE Trans Electron Devices 56(12):3123

Acknowledgement

This work was supported by the Korea Research Foundation Grant funded by the Korean Government (KRF-2008-313-D00448).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Cha, SY., Kim, HJ. & Choi, DJ. Memory characteristics of Al2O3/LaAlO3/SiO2 multilayer structures with tunnel oxide thickness variation. J Mater Sci 45, 5223–5227 (2010). https://doi.org/10.1007/s10853-010-4562-9

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10853-010-4562-9