Abstract

We have investigated the spin-Hall effect (SHE)-assisted spin transfer torque (STT) switching mechanism in a three-terminal MTJ device developed using p-MTJ (perpendicular magnetic tunnel junction) and heavy metal materials of high atomic number, which possesses large spin–orbit interaction. Using p-MTJ schematic and complementary-metal-oxide-semiconductor (CMOS) logic, we have designed three basic hybrid logic-in-memory structure-based logic gates NOR/OR, NAND/AND, and XNOR /XOR. Then the performances of these hybrid gates are evaluated and the results are compared with the conventional CMOS-based gates in terms of power, delay, power delay product, and device count. From the analysis, it is concluded that SHE-assisted STT MTJ/CMOS logic gates are nonvolatile, consume less power, and occupy a smaller die area as compared to conventional CMOS only logic gates.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Spintronics is one of the emerging areas that use the spin property of an electron in association with its charge [1, 2]. It has an extra degree of freedom for computation. The spintronics research community has attracted much of the attention because already many efforts were made for various spintronics-based applications such as the development of nonvolatile (NV) memory [3,4,5,6,7,8], NV-logic implementation [9,10,11,12,13,14,15,16,17,18], and magnetic sensors for sensing magnetic field in pico-tesla range to the new growing technologies like neuromorphic computing and the brain-inspired computing, etc. [19,20,21]. In conventional electronics, which relies on the charge-based scalar quantity, the power (or heat) dissipation can be reduced up to a certain extent. The absence or presence of charge may correspond to logic “0” and logic “1.” In contrast, spin is a pseudovector quantity whose magnitude is fixed with variable polarization and denoted by \(\hslash /2\) (where \(\hslash\) is the reduced Planck’s constant). If an electron is placed in a magnetic field, various logic states can be achieved by varying the applied magnetic field. But, while designing the hybrid circuits, which is a combination of conventional charge-based CMOS logic and spin-based spintronic devices, we need only two stable logic states, i.e., logic “1” and logic “0.” In spintronics, a spin-up and a spin-down electron are considered to be representing logic “1” and logic “0,” respectively, or vice versa. There are various spintronic devices that have been reported in the literature, such as spin-valve [22] magnetic tunnel junction (MTJ) [23], ferroelectric tunnel junction (FTJ) [24], domain wall [13, 25], skyrmion [26, 27], all-spin logic (ASL) devices [17, 18, 28], etc. Among all the spintronic devices, we chose MTJ owing to its advantages such as simplicity, nonvolatility, large endurance, high density, fast reading capability, logic computation ability, 3D fabrication, and ease of integration with the existing CMOS technology, availability of models, and ease of manufacturing, etc. [1, 29, 30]. Alternatively, it consumes zero static power and has an instant ON-OFF feature. In the literature, there are various switching/writing techniques for MTJ device, such as spin-transfer torque (STT) [31,32,33], spin–orbit torque (SOT) [34,35,36], field-induced magnetic switching (FIMS) [37], and voltage-controlled magnetic anisotropy (VCMA) [38,39,40]. Considering the commercial aspect, the STT switching mechanism is more attractive among the rest [41,42,43,44,45]. Also, because of its simplicity, STT-MTJ can be easily incorporated into logic-in-memory (LIM) circuits. LIM is a new paradigm where computational capability is embedded into the memory, i.e., memory and processing of data/information is united in a single unit. In LIM, the memory which is involved in the processing of information is also nonvolatile in nature. LIM structure offers benefits over the conventional von-Neumann architecture, viz. lower power dissipation (both static and dynamic), scaling compatibility below sub-micron level (thereby increases the device density), immunity for the radiation effects, etc. [30, 46,47,48]. However, one of the key challenges for the LIM circuit is to improve the write speed and lowering the energy dissipation. The STT-MTJ device used in the LIM shows a large intrinsic incubation delay, which slows the write speed. Furthermore, incubation delay can contribute to circuit reliability issues. Because, to ensure the correct writing, we need a large write current flowing across the STT-MTJ. The flow of large write current causes a dielectric breakdown in the STT-MTJ over a period of time. This results in poor write endurance when we use only STT switching for MTJ devices [49]. In other words, it is challenging to maintain the critical current density (\(J_C\)) while keeping high stability for the LIM structure. On the contrary, lowering \(J_C\) can be achieved at the cost of lower stability. Also, lower \(J_C\) causes read disturbance in STT-MTJ. There are several methods discussed in the literature to alleviate this trade-off [50,51,52,53,54]. But all the issues mentioned above can be addressed by spin–orbit torque (SOT) [55,56,57]. SOT is observed in a three-terminal device as shown in Fig. 1a. For STT, a spin-polarized current is needed to switch the magnetization of the free layer, while for SOT, this spin-polarized current is created by either the Rashba effect [58] or the spin-Hall effect (SHE) [35, 59]. The SOT induced by the Rashba effect is more subjected to debate [60]. Therefore, for the simplicity and availability of the MTJ model, we consider that SHE is the driving mechanism for SOT. However, the requirement of an additional external field hinders the development of SHE-MTJ-based circuits, which works purely on the SHE mechanism. As a solution, SHE-assisted STT (SHE+STT) switching method was reported in the literature [61]. The SHE+STT switching technique has proved to be not only faster but also energy efficient. Using SHE+STT switching mechanism, various applications such as memory [62, 63], flip flop [64, 65], full adder [66, 67], and recently basic logic gates [68, 69] have already been developed. However the logic gates developed in Ref. [68] utilize in-plane-MTJ (i-MTJ) rather than perpendicular-MTJ (p-MTJ). The i-MTJ suffers from disadvantages such as larger size, the difficulty for scaling, and low thermal stability, as compared to p-MTJ [2, 70, 71]. Further only AND and OR operations can be performed using the circuit proposed in Ref. [68]. Though Ref. [69] uses p-MTJ to develop the logic gate circuit, it can perform only NOT, AND/NAND, and OR/NOR operations. Further to perform these operations, the circuit requires two passive capacitors to store the sensing voltage signals. But in VLSI design incorporation of passive devices is not preferred. In this paper, we have developed all the basic logic gates such as NOR/OR, NAND/AND, and XNOR/XOR using SHE-MTJ devices based on LIM structure, where the writing of the SHE-MTJ device is performed using the SHE+STT switching mechanism. Simulations are carried out to study the performance of these circuits in terms of an output response, power dissipation, power delay product (PDP), and the number of devices utilized in comparison with their CMOS counterparts; double pass-transistor logic-based clocked CMOS (DPTL-\(\text {C}^\text {2}\text {MOS}\)) logic gates. Further, we have also performed Monte Carlo (MC) simulations on these gates to study the power variations by incorporating process and mismatch variations in CMOS and extracted parameters of MTJ, which would arise during the fabrication process.

The paper is organized as follows: Sect. 2 presents the structure and working of SHE-MTJ device and hybrid LIM structure with MTJ/CMOS. In Sect. 3, we have explained the design and working of all the hybrid logic gates. Section 4 presents the performance evaluation of all the hybrid gates in terms of key performance indicators (KPI), power dissipation, delay, PDP, and device count. Comparison of these KPIs is compared with their CMOS counterparts. To study the power variations of various gates for process and mismatch (PM) variations, we have also conducted MC simulation. Finally, the paper is concluded in Sect. 5. Appendix representing the structure of (DPTL-\(\text {C}^\text {2}\text {MOS}\))-based logic gates has been also appended for convenience.

2 Background

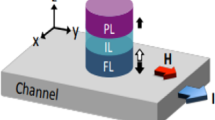

a Schematic of SHE-assisted STT MTJ showing the pinned layer (PL) and free layer (FL) separated by a barrier layer. The FL is in contact with the heavy metal (HM). When the magnetic orientation of the FL and PL is pointing in the same direction, then the MTJ is in a parallel state (P) with its resistance represented as \(R_P\). On the contrary, when the magnetic orientation of the PL and FL is pointing in the opposite direction, then the MTJ is in the anti-parallel state (AP) and the resistance state is represented as \(R_{AP}\). b Generation of pure spin current in the HM due to strong spin–orbit coupling illustrating the SHE effect [2]

SHE is considered as another phenomenon accountable for the SOT apart from Rashba effect [72]. Based on Mott scattering [73], Dyakonov and Perel predicted SHE in 1971 [34] and was revived by Hirsch in 1999 [35], the same was later demonstrated in Pt at room temperature by generating the substantial spin current [36]. Largely, SHE was believed to be arisen due to the skew scattering of s-electrons [35, 74], which is also known as an extrinsic mechanism. Materials with large SOI that also possess high atomic number such as HM convert the charge current to spin current exhibiting the SHE effect as shown in Fig. 1b. Here in HM, a flow of unpolarized electrons with charge current density (\(\mathbf {J}_C\)) creates spin-polarized electrons with spin current density (\(\mathbf {J}_S\)). Note that, \(\mathbf {J}_C\), \(\mathbf {J}_S\) and electron spin polarization \(\mathbf {\sigma }\) are all perpendicular to each other, and the relationship between them is defined in Eq. 1 as,

Where \(\theta _{SH}\) is the spin-Hall angle characterizing the strength of SHE in HM. In the SHE-MTJ structure (Fig. 1a, the SHE generated in HM influences the direction of the free layer (FL). However, accurate switching cannot be guaranteed. This is because the direction of FL in p-MTJ and the electron spin in HM are not collinear. Accurate switching in p-MTJ can be achieved by the application of either an external magnetic field or a STT current. From the literature, it is clear that generation and maintenance of the external magnetic field is undesirable from a practical point of view due to its design complexity, reduced sensitivity, and thermal stability [2]. Hence, using STT current in conjunction with SHE is a more suitable option for precise switching in p-MTJ [61]. This is called as SHE+STT switching in our manuscript. Figure 2 shows the switching of a three-terminal p-MTJ device structure with SHE+STT currents.

SHE-assisted STT MTJ switching mechanism in a p-MTJ device. a AP to P switching of the MTJ, when \(J_{SHE}\) and \(J_{STT}\) flow along Y and -Z directions, respectively. b For P to AP switching of the MTJ, the direction of \(J_{SHE}\) is the same while the direction of \(J_{STT}\) has been reversed [2]

Switching the p-MTJ from AP to P (Fig. 2a) is explained as follows when the SHE current \(J_{SHE}\) flows in Y-direction (from T3 to T2), and spin accumulation is created at the FL-HM interface. This exerts a SOT onto the FL to tilt its magnetic orientation from −Z-direction to the X-Y plane. At the same time, the STT current (\(J_{STT}\)) flowing in the -Z-direction (from T1 to T2) exerts STT and switches the orientation of FL from XY-plane to Z-direction. On the contrary, to switch p-MTJ from P to AP (Fig. 2b), the direction of \(J_{STT}\) is reversed (from −Z to Z).

2.1 Logic-in-memory structure

Initially, Kautz put forth the idea of LIM in 1969 [75], and later in a year, i.e., in 1970, Stone presented an approach for LIM computer [76]. But later it did not attract much attention. However recently, due to the slowing trend of transistor scaling, advancements in thin films, and the emergence of spintronics devices, LIM concept is drawing the notice of both academia and industry. LIM can offer solutions for the problems of increased leakage current due to scaling and considerable delay in long interconnects by positioning the NV memory section above the CMOS logic [46]. MTJs provide nonvolatility to the structure. As a result, the power supply to the idle block can be turned off without losing the information stored in the MTJ. When the power is restored this information is readily available for processing without the need for the restore operation. Hence, the static power dissipation is almost zero in the standby mode. Therefore this approach is convenient for the “instant-on” and “normally-off” system [77]. To add to the above advantage, the 3D stacking feasibility of MTJ on top of CMOS not only reduces the latency but also increases the integration density in the LIM structure. A schematic of the LIM structure with three major components is illustrated in Fig. 3 as,

-

1.

Sense amplifier/Read circuit: It produces Out and \(\overline{\text {Out}}\) based on the differential current (IL and IR) flowing through the logic network.

-

2.

Write circuit: This is used to write the information (or change the states of MTJ) in pair of MTJ. Based on the various writing mechanisms, there will be a change in the write circuitry.

-

3.

Logic network: Various logical operations can be performed based on the design of the nMOS logic tree and information stored in the MTJ pair.

Schematic of a hybrid MTJ/CMOS LIM structure [1]. Here, \(I_{write}\) is the bi-directional write current generated by the writing circuit, \(R_L\) and \(R_R\) are the left and right branch total resistances of the nMOS logic tree and MTJs, respectively. A and B are the two logic operands represented by the nMOS and three terminal MTJ

3 Hybrid MTJ/CMOS LIM-based logic gates

3.1 Selection and working of MTJ reading circuit

We have adopted the reading circuit proposed by [78], which is a modified version of the conventional pre-charge sense amplifier (PCSA) discussed in Ref. [79]. We address the PCSA from Ref. [79] as PCSA1 and from Ref. [78] as PCSA2. PCSA2 is superior to PCSA1 in terms of speed and power/energy consumption and the schematic of PCSA2 is shown in Fig. 4. The PCSA2 circuit works in two phases: the pre-charge phase and the evaluation phase. In pre-charge phase both outputs, OUT and \(\overline{\text {OUT}}\) are high. During the evaluation phase, the values stored in the MTJs are read and reflected at the output nodes. When the bit “0” is stored, the MTJ pair (MTJ0-MTJ1) is in AP-P configuration; on the contrary, when bit “1” is stored, the MTJ pair is configured as P-AP. The detailed working of the reading circuit is explained by considering bit “0” is stored in the MTJ pair as follows: Since the output of the hybrid circuits is complementary in nature, initially we consider OUT is at logic “0” and \(\overline{\text {OUT}}\) is at logic “1.”

-

1.

In the pre-charge phase: Clock (CLK)= “0” transistors P3 is ON and N3 is OFF. The OUT and \(\overline{\text {OUT}}\) node voltages will be shared through P3 and both OUT and \(\overline{\text {OUT}}\) will be pre-charged to Vdd-Vth (In PCSA1 [79], it was Vdd).

-

2.

In the evaluation phase: CLK=“1,” transistor N3 is turned ON, and it offers a discharging path for OUT as well as \(\overline{\text {OUT}}\) nodes to gnd. The current I1 and I2 in the left branch (LB) and right branch (RB), respectively, start to flow towards gnd at a different rate. This is due to the resistance variation between MTJ0 and MTJ1. As MTJ0 and MTJ1 are at \(R_{AP}\) and \(R_P\), respectively, I2 discharges faster than I1. It causes, OUT node to be pulled down the threshold voltage of P1, turning it ON. So the node \(\overline{\text {OUT}}\) is raised to logic “1.” On the contrary, OUT keeps discharging to gnd and reaches logic “0.” So sensing/reading bit “0” takes place from MTJ0-MTJ1. Similarly, we can understand reading bit “1” from the MTJ pair when it is configured as P-AP.

PCSA2 produces a quicker output response than PCSA1 because, in the pre-charge phase of PCSA2 both the outputs, i.e., OUT and \(\overline{\text {OUT}}\) are pre-charged to Vdd-Vth, whereas in PCSA1, OUT and \(\overline{\text {OUT}}\) are pre-charged to Vdd. In the evaluation phase, when one of the outputs of PCSA2 discharges to gnd from Vdd-Vth, it takes lesser time as compared to PCSA1, where Vdd needs to be discharged to gnd. Consequently, the lower voltage (Vdd-Vth) in PCSA2 dissipates lower power than PCSA1. Further, PCSA2 works with one PMOS lesser than PCSA1, which helps to reduce the transistor count.

Schematic of the PCSA2 circuit which reads the bit stored in a pair of MTJs [78]

3.2 SHE+STT MTJ writing circuit for LIM structure

Schematic of the MTJ write circuit working with the SHE+STT writing mechanism [64]

Figure 5 shows the writing circuit for SHE-MTJs with the SHE+STT switching mechanism. The writing driver is divided into two parts: control circuitry and writing core. It has three inputs, viz. Data, EnW, and EnSHE. Table 1 shows the different combinations of the input signals, control signals, and the corresponding status of the MTJ pair. When EnW is at logic “0,” the writing core is disabled by the intermediate signals (STTP, STTN, SHEP, SHEN = “1010”) of the control circuit, and no writing takes place. Information will be written only when EnW = “1.” Consider writing bit “1” into the MTJ pair, for which EnW, EnSHE, and Data are set as “111,” respectively. So the intermediate signals STTP, STTN, SHEP, SHEN will be at “1101,” respectively. This will turn ON transistors MP1, MP2, MP3, MN0, MN1, MN3. Two types of current are flowing in the circuit, i.e., SHE and STT current. SHE current path is; Vdda-MP1-MTJ0-MN1-gnd and Vdda-MP3-MTJ1-MN3-gnd. STT current path is; Vdda-MP2-MTJ1-MN3-gnd and Vdda-MP1-MTJ0-MN0-gnd. At this point, the MTJ pair is in a metastable state. After a brief period, EnSHE is asserted to “0” , making STTP, STTN, SHEP, SHEN = “1100.” This will turn OFF the transistors MP3 and MN1 which stops the flow of SHE current in the circuit. But STT current flows continuously to change the MTJ0-MTJ1 configuration to P-AP, respectively. Similarly, Data “0” can be written into the MTJ pair by suitably changing the input signals as shown in Table 1.

3.3 Hybrid MTJ/CMOS LIM-based logic gates

Figure 6a–c shows the circuit for NOR/OR, NAND/AND and XNOR/XOR gates, respectively, and Table 2 shows corresponding truth table. These hybrid circuits operate in the pre-charge and evaluation phase. In the pre-charge phase inputs are applied and in the evaluation phase output and its complement are obtained. The working of the NOR/OR gate in its evaluation phase is as follows. Whenever input A = “1” , N6 in the right branch (RB) is open and N5 in the left branch (LB) is ON. The total RB resistance for the discharge current (I2) is the sum of OFF-transistor (N6) resistance (\(R_{OFF}\)) and MTJ1 resistance (\(R_P/R_{AP}\)). Similarly, total LB resistance for the discharge current (I1) is the sum of ON-transistor (N5) resistance (\(R_{ON}\)) and MTJ0 resistance (\(R_P/R_{AP}\)). In this case, since transistor N6 is OFF, RB resistance is always greater than the LB resistance. The state of the MTJ does not affect the output, as \(R_{OFF}\) is always greater than either \(R_{ON}+R_{AP}\) or \(R_{ON}+R_P\) (\(R_{OFF}>(R_{ON}+R_{AP}\)) or \(R_{OFF}>(R_{ON}+R_P\))). Therefore OR output node is raised to Vdd, and the NOR node discharge to gnd; hence, it is at logic “0,” whereas when the A = “0,” N4 and N6 in LB and RB are ON, due to that NOR and OR outputs have a discharging path to gnd. In this condition, the bit stored in B decides the value of output nodes. If B = “0,” the state of the MTJ0-MTJ1 is in AP-P configuration. So the total resistance observed for currents I1 and I2 is \(R_{ON}+R_{AP}\) and \(R_{ON}+R_{P}\), respectively. Thus the LB resistance is comparatively greater than RB. This results in the NOR node being raised to logic “1”; correspondingly, OR node will be discharged to gnd. In another instance, when A = “0” and B = “1,” MTJ pair is at P-AP configuration. Resistances of LB and RB are at \(R_{ON}+R_{P}\) and \(R_{ON}+R_{AP}\) for the currents I1 and I2, respectively. Now the LB resistance is lower than RB. Hence, OR output node raises to logic “1” and the NOR output node discharges to gnd, producing logic “0.” Similarly working of NAND/AND and XNOR/XOR gates can be understood.

4 Simulation results and discussion

We have performed electrical simulations in 45 nm CMOS generic process design kit using the Cadence tool (IC 6.1.7-64b.500.19) with default transistor parameters, L =45nm and W =120nm. The SHE-MTJ electrical model developed by Ref. [60] is used in our simulation work. This model is developed using the Verilog-A language. Table 3 shows the MTJ parameters set during the simulation with the SHE-MTJ model, whereas the other parameters are retained as default values as mentioned in Ref. [60]. We have set a supply voltage of Vdda = 1.2V for MTJ writing purpose, and Vdd = 1V for MTJ reading operations and DPTL-\(\text {C}^\text {2}\text {MOS}\) logic. With Vdda, we ensure that there is no area overhead caused by the writing core transistors; meanwhile, the MTJ write current is larger than the critical current so that switching of the MTJ can be accomplished with 100% probability.

4.1 Model verification of SHE-assisted STT MTJ model

In this section, we have performed model verification of SHE-MTJ and studied its switching behavior. Figure 7a, b show the waveform of SHE-MTJ model for three particular cases with SHE+STT, STT only (SHE current is zero), and SHE only (STT current is zero) simulation for AP to P and P to AP switching condition, respectively [60]. As seen in Fig. 7a, the switching time for AP to P switching with SHE+STT mechanism is at T1, whereas with STT only mechanism, it is at T2. On the contrary, with SHE only, the switching of MTJ does not take place. Similarly, as seen in Fig. 7b, the switching time for P to AP switching with SHE+STT mechanism is at T3, whereas it is at T4 with STT only mechanism. In this case also, with SHE only, switching does not take place. With SHE+STT switching mechanism, we have obtained T2-T1 and T4-T3, as the improvement in switching time for AP to P and P to AP switching, respectively, as compared to STT only switching mechanism. This is due to the elimination of incubation delay with the SHE+STT switching mechanism.

Simulated waveform of a single-cell SHE-MTJ for a AP to P and b P to AP switching. While obtaining the switching times (T1 to T4), a supply of 1.2 V, and SHE pulse width of 250 ns are applied. Other MTJ parameters are set according to Table 3. When the signal crosses 90% of its maximum value we consider that the MTJ switching is complete

Figure 8 shows the analysis of varying SHE pulse width, i.e., from 0 to 355 ps, on the switching process of the SHE+STT switching mechanism. It is observed that when SHE pulse width is zero, STT only switching takes place. The switching time is minimum when SHE pulse width is set to 100 ps. Figure 9 shows the simulated waveform for the writing circuit which works on the SHE+STT switching mechanism. Initially bit “1” is stored in the MTJ pair. At time T1, EnW and EnSHE enable the writing of bit “0.” At time T2 bit “1” is written. At time T3, bit “1” is being rewritten into the MTJ pair, which is known as redundant write. Table 4 shows the comparison in terms of energy consumption, device count, and worst-case switching delay for SHE+STT and STT only writing process. Here we can notice that the average energy/bit consumption for STT only switching is 813.17fJ, whereas, with SHE+STT switching, it is 822.28fJ. There is a marginal decrease in the average energy/bit (i.e., 9.11fJ) with STT only as compared to SHE+STT switching. However, the worst-case delay for SHE+STT switching is 386.82ps, whereas for the STT only switching it is 900ps. With SHE+STT switching, the worst-case delay is decreased by 57.02%. Moreover, due to stochasticity and incubation delay associated with STT only switching, there is no guaranteed 100% switching in STT only. Hence, SHE+STT switching is the better option over STT only.

4.2 Performance analysis of hybrid MTJ/CMOS logic gates

We address the hybrid NOR/OR, NAND/AND, and XNOR/XOR logic gates with PCSA1 as HG1 and hybrid logic gates with PCSA2 as HG2, whereas its corresponding CMOS counterparts are developed using DPTL-\(\text {C}^{2}\text {MOS}\) logic and we address them as DPTL-\(\text {C}^\text {2}\text {MOS}\) logic gates. The comparison between hybrid and DPTL-\(\text {C}^{2}\text {MOS}\)-based NOR/OR, NAND/AND, and XOR/XNOR gate operations in terms of power, delay, PDP, and device count is presented in Table 5. The static power dissipation of HG1 and HG2 gates is considered to be zero in comparison with their CMOS counterparts because, in the hybrid logic gate, we store the input B in the nonvolatile MTJ pair, due to which we can turn off the power supply in the standby mode without losing the information. In the active mode, the stored information is readily available for computation without the need for a write/restoration process. However, there is steady-state power dissipation observed for the hybrid logic gates which are shown in Table 5.

The dynamic power dissipation in HG2 is least as compared to its corresponding HG1 and DPTL-\(\text {C}^{2}\text {MOS}\) logic gates. The dynamic power dissipation for NOR/OR, NAND/AND, and XNOR /XOR logic gates in HG2 is less than HG1 by 51.7%, 55.11% and 53.23%, respectively, and it is less than its DPTL-\(\text {C}^ {2}\text {MOS}\) logic gates by 66.11%, 66.23% and 62.03%, respectively. Similarly, the total power dissipation of NOR/OR, NAND/AND, and XNOR /XOR logic gates in HG2 is less than HG1 by 23.42%, 22.31%, and 27.84% and it is less than DPTL-\(\text {C}^ {2}\text {MOS}\) logic gates by 24.85%, 27.84% and 29.02%, respectively. Figure 10a, b shows a bar chart plot for the dynamic as well as total power dissipation comparison between HG1, HG2 and DPTL-\(\text {C}^ {2}\text {MOS}\)-based NOR/OR, NAND/AND and XNOR/XOR logic gates, respectively.

The delay depends upon the quality of the sense amplifier used in hybrid logic gates. In HG2 with PCSA2, during the pre-charge phase both output and its complement are at voltage Vdd-Vth, whereas for HG1 with PCSA1, output and its complement are at voltage Vdd. Hence during the evaluation phase, HG2 with PCSA2 discharges one of its output to gnd quicker than its corresponding HG1 with PCSA1 counterpart, producing a faster output response. But the DPTL-\(\text {C}^{2}\text {MOS}\) logic gates have lesser delay than hybrid gates. This is because in DPTL-\(\text {C}^ {2}\text {MOS}\) logic operates based on clocked CMOS pass transistor logic, whereas the hybrid gates use current-controlled sense amplifier. In the evaluation phase, the pull-down transistor N3 of the hybrid gates needs to provide a discharge path for the current (either I1 or I2) due to which the output delay depends upon the size of this transistor. By increasing the width of the N3 transistor the delay of the hybrid gates can be reduced. However, by doing so the power dissipation in the HG2 will increase, which is shown in Table 6 and Fig. 11. Hence, we need to tackle this delay versus power dissipation trade-off for the hybrid gates.

In terms of device count, the HG2 NOR/OR and NAND/AND gates need only 11 MOS transistors, on the contrary, HG1, and DPTL-\(\text {C}^\text {2}\text {MOS}\) require 12 and 19 MOS transistors, respectively. Similarly, for XNOR/XOR gate, HG1 and DPTL-\(\text {C}^\text {2}\text {MOS}\) require 13 and 22 MOS transistors, whereas, for the HG2 XNOR/ XOR gate, only 12 MOS transistors are sufficient. Hence, in terms of the number of transistors HG2 logic gates are superior to HG1 and DPTL-\(\text {C}^\text {2}\text {MOS}\) logic gates.

The process and mismatch variations during nano-scale fabrication of VLSI circuits affect its performance. To study this effect at the design stage, we have performed MC simulation of 200 runs for the design. During MC simulation, we have not only incorporated CMOS variations, but also, 3% variations in the TMR, \({t_{sl}}\) and \({t_{ox}}\) (refer Table 3) that follow Gaussian distribution for the MTJs. Table 7 shows the total power dissipation comparison among all the logic gates. It suggests that HG2 logic gate design dissipates the least power compared to the rest of the designs.

5 Conclusion

The major contribution of this work is to provide an in-depth analysis of basic hybrid circuits developed using CMOS logic and p-MTJ device. In this paper, we have designed and presented a detailed analysis of all the logic gates, i.e., NOR/OR, NAND/AND, and XNOR/XOR based on the hybrid SHE+STT-MTJ/CMOS LIM structure. The simulation results obtained substantiates the fact that hybrid logic gates are not only nonvolatile in nature but also are superior to their CMOS counterparts in terms of power dissipation and the number of transistors used in the design. Due to the nonvolatility nature of hybrid logic gates, they can be completely turned off in standby mode to save a significant amount of power without the necessity of backup or restoring process as in the conventional CMOS technology. Hence these circuits can be considered for future low power applications.

Availability of data and material

Not applicable.

References

Joshi, V.K., Barla, P., Bhat, S., Kaushik, B.K.: From MTJ device to hybrid CMOS/MTJ circuits: a review. IEEE Access 8, 194105–194146 (2020). https://doi.org/10.1109/ACCESS.2020.3033023

Barla, P., Joshi, V.K., Bhat, S.: Spintronic devices: a promising alternative to CMOS devices. J. Comput. Electron. 20(2), 805–837 (2021). https://doi.org/10.1007/s10825-020-01648-6

Sousa, R.C., Prejbeanu, I.L.: Non-volatile magnetic random access memories (MRAM). C. R. Phys. 9(6), 1013–1021 (2005). https://doi.org/10.1016/j.crhy.2005.10.007

Zhao, W., Belhaire, E., Chappert, C., Jacquet, F., Mazoyer, P.: New non-volatile logic based on spin-MTJ. Phys. Status Solidi A 205(6), 1373–1377 (2008). https://doi.org/10.1002/pssa.200778135

Chabi, D., Zhao, W., Deng, E., Zhang, Y., Romdhane, N.B., Klein, J.-O., Chappert, C.: Ultra low power magnetic flip-flop based on checkpointing/power gating and self-enable mechanisms. IEEE Trans. Circuits Syst. I Regul. Pap. 61(6), 1755–1765 (2014). https://doi.org/10.1109/TCSI.2013.2295026

Roohi, A., DeMara, R.F.: NV-clustering: normally-off computing using non-volatile datapaths. IEEE Trans. Comput. 67(7), 949–959 (2018). https://doi.org/10.1109/TC.2018.2795601

Jaiswal, A., Andrawis, R., Roy, K.: Area-efficient nonvolatile flip-flop based on spin hall effect. IEEE Magn. Lett. 9, 1–4 (2018). https://doi.org/10.1109/LMAG.2018.2829676

Kang, W., Ran, Y., Lv, W., Zhang, Y., Zhao, W.: High-speed, low-power, magnetic non-volatile flip-flop with voltage-controlled, magnetic anisotropy assistance. IEEE Magn. Lett. 7, 1–5 (2016). https://doi.org/10.1109/LMAG.2016.2604205

Barla, P., Shet, D., Joshi, V. K., Bhat, S.: Design and analysis of LIM hybrid MTJ/CMOS logic gates. In: 2020 5th International Conference on Devices, Circuits and Systems (ICDCS), 2020, pp. 41–45. https://doi.org/10.1109/ICDCS48716.2020.243544

Barla, P., Joshi, V.K., Bhat, S.: A novel low power and reduced transistor count magnetic arithmetic logic unit using hybrid STT-MTJ/CMOS circuit. IEEE Access 8, 6876–6889 (2020). https://doi.org/10.1109/ACCESS.2019.2963727

Matsunaga, S., Hayakawa, J., Ikeda, S., Miura, K., Endoh, T., Ohno, H., Hanyu, T.: MTJ-based nonvolatile logic-in-memory circuit, future prospects and issues. In: Proceedings of Conference Design, Autom. Test Europe, 2009, pp. 433–435. https://doi.org/10.1109/DATE.2009.5090704

Deng, E., Zhang, Y., Klein, J.-O., Ravelsona, D., Chappert, C., Zhao, W.: Low power magnetic full-adder based on spin transfer torque MRAM. IEEE Trans. Magn. 49(9), 4982–4987 (2013). https://doi.org/10.1109/TMAG.2013.2245911

Roohi, A., Zand, R., DeMara, R.F.: A tunable majority gate-based full adder using current-induced domain wall nanomagnets. IEEE Trans. Magn. 52(8), 1–7 (2016). https://doi.org/10.1109/TMAG.2016.2540600

Roohi, A., Zand, R., Fan, D., DeMara, R.F.: Voltage-based concatenatable full adder using spin hall effect switching. IEEE Trans. Comput.-Aid. Des. Integr. Circuits Syst. 36(12), 2134–2138 (2017). https://doi.org/10.1109/TCAD.2017.2661800

Zarei, A., Safaei, F.: Power and area-efficient design of VCMA-MRAM based full-adder using approximate computing for IoT applications. Microelectron. J. 82, 62–70 (2018). https://doi.org/10.1016/j.mejo.2018.10.010

An, Q., Su, L., Klein, J.-O., Beux, S.L., OConnor, I., Zhao, W.: Full-adder circuit design based on all-spin logic device, 163–168 (2015). https://doi.org/10.1109/NANOARCH.2015.7180606

Patra, M., Maiti, S.K.: All-spin logic operations: memory device and reconfigurable computing. EPL 121(3), 38004 (2018). https://doi.org/10.1209/0295-5075/121/38004

An, Q., Beux, S.L., OConnor, I., Klein, J.O., Zhao, W.: Arithmetic Logic Unit based on all-spin logic devices. IEEE (2017). https://doi.org/10.1109/NEWCAS.2017.8010169

Cardoso, S., Leitao, D.C., Gameiro, L., Cardoso, F., Ferreira, R., Paz, E., Freitas, P.P.: Magnetic tunnel junction sensors with pTesla sensitivity. Microsyst. Technol. 20(4), 793–802 (2014). https://doi.org/10.1007/s00542-013-2035-1

Roy, K., Sengupta, A., Shim, Y.: Perspective: stochastic magnetic devices for cognitive computing. J. Appl. Phys. 123(21), 210901 (2018). https://doi.org/10.1063/1.5020168

Wijesinghe, P.: Neuro-inspired computing enhanced by scalable algorithms and physics of emerging nanoscale resistive devices, Ph.D. thesis, Purdue University Graduate School (2019). https://doi.org/10.25394/PGS.8273483.v1

Lin, X., Yang, W., Wang, K.L., Zhao, W.: Two-dimensional spintronics for low-power electronics. Nat. Electron. 2(7), 274–283 (2019). https://doi.org/10.1038/s41928-019-0273-7

Jinnai, B., Watanabe, K., Fukami, S., Ohno, H.: Scaling magnetic tunnel junction down to single-digit nanometers-Challenges and prospects. Appl. Phys. Lett. 116(16), 160501 (2020). https://doi.org/10.1063/5.0004434

Wang, Z., Zhao, W., Kang, W., Bouchenak-Khelladi, A., Zhang, Y., Zhang, Y., Klein, J.-O., Ravelosona, D., Chappert, C.: A physics-based compact model of ferroelectric tunnel junction for memory and logic design. J. Phys. D Appl. Phys. 47(4), 045001 (2013). https://doi.org/10.1088/0022-3727/47/4/045001

Luo, Z., Hrabec, A., Dao, T.P., Sala, G., Finizio, S., Feng, J., Mayr, S., Raabe, J., Gambardella, P., Heyderman, L.J.: Current-driven magnetic domain-wall logic. Nature 579(7798), 214–218 (2020). https://doi.org/10.1038/s41586-020-2061-y

Mankalale, M.G., Zhao, Z., Wang, J.-P., Sapatnekar, S.S.: SkyLogic-a proposal for a skyrmion-based logic device. IEEE Trans. Electron Devices 66(4), 1990–1996 (2019). https://doi.org/10.1109/TED.2019.2899263

Zhang, Z., Zhu, Y., Zhang, Y., Zhang, K., Nan, J., Zheng, Z., Zhang, Y., Zhao, W.: Skyrmion-based ultra-low power electric-field-controlled reconfigurable (SUPER) logic gate. IEEE Electron Device Lett. 40(12), 1984–1987 (2019). https://doi.org/10.1109/LED.2019.2946863

Behin-Aein, B., Datta, D., Salahuddin, S., Datta, S.: Proposal for an all-spin logic device with built-in memory. Nat. Nanotechnol. 5(4), 266–270 (2010). https://doi.org/10.1038/nnano.2010.31

Zhao, W., Prenat, G.: Spintronics-Based Computing. Springer, Berlin (2015). https://doi.org/10.1007/978-3-319-15180-9

Kang, W., Deng, E., Wang, Z., Zhao, W.: Spintronic Logic-in-Memory Paradigms and Implementations. In: Suri M. (eds) Applications of Emerging Memory Technology., Springer Series in Advanced Microelectronics 63 (2020) 215–229. https://doi.org/10.1007/978-981-13-8379-3-9

Slonczewski, J.C.: Current-driven excitation of magnetic multilayers. J. Magn. Magn. Mater. 159(1), L1–L7 (1996). https://doi.org/10.1016/0304-8853(96)00062-5

Berger, L.: Emission of spin waves by a magnetic multilayer traversed by a current. Phys. Rev. B 54(13), 9353–9358 (1996). https://doi.org/10.1103/PhysRevB.54.9353

Huai, Y., Albert, F., Nguyen, P., Pakala, M., Valet, T.: Observation of spin-transfer switching in deep submicron-sized and low-resistance magnetic tunnel junctions. Appl. Phys. Lett. 84(16), 3118–3120 (2004). https://doi.org/10.1063/1.1707228

DYakonov, M. I., Perel, V. I.:https://ui.adsabs.harvard.edu/abs/1971JETPL..13..467D/abstractPossibility of Orienting Electron Spins with Current, JETPL 13 (1971) 467

Hirsch, J.E.: Spin hall effect. Phys. Rev. Lett. 83(9), 1834–1837 (1999). https://doi.org/10.1103/PhysRevLett.83.1834

Saitoh, E., Ueda, M., Miyajima, H., Tatara, G.: Conversion of spin current into charge current at room temperature: Inverse spin-Hall effect. Appl. Phys. Lett. 88(18), 182509 (2006). https://doi.org/10.1063/1.2199473

Wolf, S.A., Awschalom, D.D., Buhrman, R.A., Daughton, J.M., von Molnár, S., Roukes, M.L., Chtchelkanova, A.Y., Treger, D.M.: Spintronics: a spin-based electronics vision for the future. Science 294(5546), 1488–1495 (2001). https://doi.org/10.1126/science.1065389

Shiota, Y., Nozaki, T., Bonell, F., Murakami, S., Shinjo, T., Suzuki, Y.: Induction of coherent magnetization switching in a few atomic layers of FeCo using voltage pulses. Nat. Mater. 11(1), 39–43 (2012). https://doi.org/10.1038/nmat3172

Chu, Y.-H., Martin, L.W., Holcomb, M.B., Gajek, M., Han, S.-J., He, Q., Balke, N., Yang, C.-H., Lee, D., Hu, W., Zhan, Q., Yang, P.-L., Fraile-Rodríguez, A., Scholl, A., Wang, S.X., Ramesh, R.: Electric-field control of local ferromagnetism using a magnetoelectric multiferroic. Nat. Mater. 7(6), 478–482 (2008). https://doi.org/10.1038/nmat2184

Nozaki, T., Shiota, Y., Shiraishi, M., Shinjo, T., Suzuki, Y.: Voltage-induced perpendicular magnetic anisotropy change in magnetic tunnel junctions. Appl. Phys. Lett. 96(2), 022506 (2010). https://doi.org/10.1063/1.3279157

Song, Y.J. , Lee, J.H., Shin, H.C., Lee, K.H., Suh, K., Kang, J.R., Pyo, S.S., Jung, H.T., Hwang, S.H., Koh, G.H., Oh, S.C., Park, S.O., Kim, J.K., Park, J.C., Kim, J., Hwang, K.H., Jeong, G.T., Lee, K.P., Jung, E.S.:Highly functional and reliable 8Mb STT-MRAM embedded in 28nm logic, 2016 IEEE International Electron Devices Meeting (IEDM) (2016) 27.2.1–27.2.4 https://doi.org/10.1109/IEDM.2016.7838491

Chung, S.-W., Kishi, T., Park, J.W., Yoshikawa, M., Park, K.S., Nagase, T., Sunouchi, K., Kanaya, H., Kim, G.C., Noma, K., Lee, M.S., Yamamoto, A., Rho, K.M., Tsuchida, K., Chung, S.J., Yi, J.Y., Kim, H.S., Chun, Y.S., Oyamatsu, H., Hong, S.J.:4Gbit density STT-MRAM using perpendicular MTJ realized with compact cell structure, 2016 IEEE International Electron Devices Meeting (IEDM) (2016) 27.1.1–27.1.4 https://doi.org/10.1109/IEDM.2016.7838490

Lu, Y., Zhong, T., Hsu, W., Kim, S., Lu, X., Kan, J.J., Park, C., Chen, W.C., Li, X., Zhu, X., Wang, P., Gottwald, M., Fatehi, J., Seward, L., Kim, J.P., Yu, N., Jan, G., Haq, J., Le, S., Wang, Y.J., Thomas, L., Zhu, J., Liu, H., Lee, Y.J., Tong, R.Y., Pi, K., Shen, D., He, R., Teng, Z., Lam, V., Annapragada, R., Torng, T., Wang, P.-K., Kang, S.H.: Fully functional perpendicular STT-MRAM macro embedded in 40 nm logic for energy-efficient IOT applications, 2015 IEEE International Electron Devices Meeting (IEDM) (2015) 26.1.1–26.1.4 https://doi.org/10.1109/IEDM.2015.7409770

https://www.everspin.com/spin-transfer-torque-mram-productsSpin-transfer Torque MRAM Products\(\vert\)Everspin (2021)

Yoda, H., Fujita, S., Shimomura, N., Kitagawa, E., Abe, K., Nomura, K., Noguchi, H., Ito, J.:Progress of STT-MRAM technology and the effect on normally-off computing systems. In: 2012 International Electron Devices Meeting, 2012, pp. 11.3.1–11.3.4. https://doi.org/10.1109/IEDM.2012.6479023

Endoh, T., Koike, H., Ikeda, S., Hanyu, T., Ohno, H.: An overview of nonvolatile emerging memories- spintronics for working memories. IEEE J. Emerg. Sel. Top. Circuits Syst. 6(2), 109–119 (2016). https://doi.org/10.1109/JETCAS.2016.2547704

Kang, W., Zhao, W., Deng, E., Klein, J.-O., Cheng, Y., Ravelosona, D., Zhang, Y., Chappert, C.: A radiation hardened hybrid spintronic/CMOS nonvolatile unit using magnetic tunnel junctions. J. Phys. D Appl. Phys. 47(40), 405003 (2014). https://doi.org/10.1088/0022-3727/47/40/405003

Onizawai, N., Hanyu, T.:Soft-error tolerant transistor/ magnetic-tunnel-junction hybrid non-volatile C-element. IEICE Electron. Express (2014) 11.20141017 https://doi.org/10.1587/elex.11.20141017

Wang, Z., Zhou, H., Wang, M., Cai, W., Zhu, D., Klein, J.-O., Zhao, W.: Proposal of toggle spin torques magnetic RAM for ultrafast computing. IEEE Electron Device Lett. 40(5), 726–729 (2019). https://doi.org/10.1109/LED.2019.2907063

Mangin, S., Ravelosona, D., Katine, J.A., Carey, M.J., Terris, B.D., Fullerton, E.E.: Current-induced magnetization reversal in nanopillars with perpendicular anisotropy. Nat. Mater. 5, 210–215 (2006). https://doi.org/10.1038/nmat1595

Kishi, T., Yoda, H., Kai, T., Nagase, T., Kitagawa, E., Yoshikawa, M., Nishiyama, K., Daibou, T., Nagamine, M., Amano, M., Takahashi, S., Nakayama, M., Shimomura, N., Aikawa, H., Ikegawa, S., Yuasa, S., Yakushiji, K., Kubota, H., Fukushima, A., Oogane, M., Miyazaki, T., Ando, K.: Lower-current and fast switching of a perpendicular TMR for high speed and high density spin-transfer-torque MRAM. https://doi.org/10.1109/IEDM.2008.4796680

Yoshikawa, M., Kitagawa, E., Nagase, T., Daibou, T., Nagamine, M., Nishiyama, K., Kishi, T., Yoda, H.: Tunnel magnetoresistance over 100% in MgO-based magnetic tunnel junction films with perpendicular magnetic L1\(\_\)\(\lbrace\)0\(\rbrace\)-FePt electrodes. IEEE Trans. Magn. 44(11), 2573–2576 (2008). https://doi.org/10.1109/TMAG.2008.2003059

Ikeda, S., Miura, K., Yamamoto, H., Mizunuma, K., Gan, H.D., Endo, M., Kanai, S., Hayakawa, J., Matsukura, F., Ohno, H.: A perpendicular-anisotropy CoFeB-MgO magnetic tunnel junction. Nat. Mater. 9(9), 721–724 (2010). https://doi.org/10.1038/nmat2804

Barla, P., Joshi, V.K., Bhat, S.: A novel self write-terminated driver for hybrid STT-MTJ/CMOS LIM structure. Ain Shams Eng. J. 12(2), 1839–1847 (2021). https://doi.org/10.1016/j.asej.2020.10.012

Mihai Miron, I., Gaudin, G., Auffret, S., Rodmacq, B., Schuhl, A., Pizzini, S., Vogel, J., Gambardella, P.: Current-driven spin torque induced by the Rashba effect in a ferromagnetic metal layer. Nat. Mater. 9(3), 230–234 (2010)

Miron, I.M., Garello, K., Gaudin, G., Zermatten, P.-J., Costache, M.V., Auffret, S., Bandiera, S., Rodmacq, B., Schuhl, A., Gambardella, P.: Perpendicular switching of a single ferromagnetic layer induced by in-plane current injection. Nature 476, 189–193 (2011). https://doi.org/10.1038/nature10309

Liu, L., Pai, C.-F., Li, Y., Tseng, H.W., Ralph, D.C., Buhrman, R.A.: Spin-torque switching with the giant spin hall effect of tantalum. Science 336(6081), 555–558 (2012). https://doi.org/10.1126/science.1218197

Bychkov, Y.A., Rashba, É.I.: Properties of a 2d electron gas with lifted spectral degeneracy. JETP Lett. 39(2), 78 (1984)

Zhang, S.: Spin hall effect in the presence of spin diffusion. Phys. Rev. Lett. 85(2), 393–396 (2000). https://doi.org/10.1103/PhysRevLett.85.393

Wang, Z., Zhao, W., Deng, E., Klein, J.-O., Chappert, C.: Perpendicular-anisotropy magnetic tunnel junction switched by spin-Hall-assisted spin-transfer torque. J. Phys. D Appl. Phys. 48(6), 065001 (2015). https://doi.org/10.1088/0022-3727/48/6/065001

van den Brink, A., Cosemans, S., Cornelissen, S., Manfrini, M., Vaysset, A., Van Roy, W., Min, T., Swagten, H.J.M., Koopmans, B.: Spin-Hall-assisted magnetic random access memory. Appl. Phys. Lett. 104(1), 012403 (2014). https://doi.org/10.1063/1.4858465

Kang, W., Lv, W., Zhang, Y., Zhao, W.: Low store power high-speed high-density nonvolatile SRAM design with spin hall effect-driven magnetic tunnel junctions. IEEE Trans. Nanotechnol. 16(1), 148–154 (2017). https://doi.org/10.1109/TNANO.2016.2640338

Wang, Z., Zhang, L., Wang, M., Wang, Z., Zhu, D., Zhang, Y., Zhao, W.: High-density NAND-like spin transfer torque memory with spin orbit torque erase operation. IEEE Electron Device Lett. 39(3), 343–346 (2018). https://doi.org/10.1109/LED.2018.2795039

Wang, Z., Zhao, W., Deng, E., Zhang, Y., Klein, J.-O.: Magnetic non-volatile flip-flop with spin-Hall assistance. Phys. Status Solidi RRL 9(6), 375–378 (2015). https://doi.org/10.1002/pssr.201510097

Javadi, A.A., Morsali, M., Moaiyeri, M.H.: Magnetic nonvolatile flip-flops with spin-Hall assistance for power gating in ternary systems. J. Comput. Electron. 19(3), 1175–1186 (2020). https://doi.org/10.1007/s10825-020-01516-3

Amirany, A., Rajaei, R.: Fully nonvolatile and low power full adder based on spin transfer torque magnetic tunnel junction with spin-hall effect assistance. IEEE Trans. Magn. 54(12), 1–7 (2018). https://doi.org/10.1109/TMAG.2018.2869811

Deng, E., Wang, Z., Klein, J.-O., Prenat, G., Dieny, B., Zhao, W.: High-frequency low-power magnetic full-adder based on magnetic tunnel junction with spin-hall assistance. IEEE Trans. Magn. 51(11), 1–4 (2015). https://doi.org/10.1109/TMAG.2015.2449554

Parveen, F., Angizi, S., He, Z., Fan, D.: Low power in-memory computing based on dual-mode SOT-MRAM. In: IEEE/ACM International Symposium on Low Power Electronics and Design (ISLPED). IEEE 2017, 1–6 (2017). https://doi.org/10.1109/ISLPED.2017.8009200

Wang, C., Wang, Z., Xu, Y., Yang, J., Zhang, Y., Zhao, W., Based, Computing-in-Memory Architecture., on Field-Free SOT-MRAM with Self-Reference Method, in, : IEEE International Symposium on Circuits and Systems (ISCAS). IEEE 2020, 1–4 (2020). https://doi.org/10.1109/ISCAS45731.2020.9180668

Johnson, M.T., Bloemen, P.J.H., Broeder, F.J.A.D., de Vries, J.J.: Magnetic anisotropy in metallic multilayers. Rep. Prog. Phys. 59(11), 1409–1458 (1996). https://doi.org/10.1088/0034-4885/59/11/002

Draaisma, H.J.G., de Jonge, W.J.M., Den Broeder, F.J.A.: Magnetic interface anisotropy in Pd/Co and Pd/Fe multilayers. J. Magn. Magn. Mater. 66(3), 351–355 (1987). https://doi.org/10.1016/0304-8853(87)90169-7

Bandyopadhyay, S., Cahay, M.: Introduction to Spintronics. CRC Press, Boca Raton (2015)

Francis, M.N., David, B.N.H.: The scattering of fast electrons by atomic nuclei. Proc. R. Soc. Lond. A 124(794), 425–442 (1929). https://doi.org/10.1098/rspa.1929.0127

Smit, J.: The spontaneous hall effect in ferromagnetics II. Physica 24(1), 39–51 (1958). https://doi.org/10.1016/S0031-8914(58)93541-9

Kautz, W.H.: Cellular logic-in-memory arrays. IEEE Trans. Comput. C 18(8), 719–727 (1969). https://doi.org/10.1109/T-C.1969.222754

Stone, H.S.: A logic-in-memory computer. IEEE Trans. Comput. C 19(1), 73–78 (1970). https://doi.org/10.1109/TC.1970.5008902

Hanyu, T., Endoh, T., Suzuki, D., Koike, H., Ma, Y., Onizawa, N., Natsui, M., Ikeda, S., Ohno, H.: Standby-power-free integrated circuits using MTJ-based VLSI computing. Proc. IEEE 104(10), 1844–1863 (2016). https://doi.org/10.1109/JPROC.2016.2574939

Thapliyal, H., Sharifi, F., Kumar, S.D.: Energy-efficient design of hybrid MTJ/CMOS and MTJ/nanoelectronics circuits. IEEE Trans. Magn. 54(7), 1–8 (2018). https://doi.org/10.1109/TMAG.2018.2833431

Zhao, W., Chappert, C., Javerliac, V., Noziere, J.-P.: High speed, high stability and low power sensing amplifier for MTJ/CMOS hybrid logic circuits. IEEE Trans. Magn. 45(10), 3784–3787 (2009). https://doi.org/10.1109/TMAG.2009.2024325

Acknowledgements

Prashanth Barla would like to acknowledge the Manipal Institute of Technology, Manipal Academy of Higher Education, Manipal, for providing TMA Pai scholarship for his research work. Part of the work presented in Introduction and Background sections has been already reported and refs. [1, 2, 9] and can be used for detailed understanding.

Funding

Open access funding provided by Manipal Academy of Higher Education, Manipal.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest.

Code availability

Not applicable

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Barla, P., Joshi, V.K. & Bhat, S. Design and analysis of SHE-assisted STT MTJ/CMOS logic gates. J Comput Electron 20, 1964–1976 (2021). https://doi.org/10.1007/s10825-021-01759-8

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-021-01759-8