Abstract

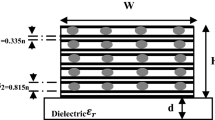

A temperature-dependent delay optimization model for a multilayered graphene nanoribbon (MLGNR) with top contact (TC-GNR), side contact (SC-GNR), and Cu-based nano-interconnects using a wire sizing method was applied to determine the delay for different interconnects widths (11 nm, 16 nm, and 22 nm) and lengths (10 μm, 50 μm, and 100 μm), being the first such model for TC-GNR, SC-GNR, and Cu interconnects applied at three different chip operating temperatures (233 K, 300 K, and 378 K). The results reveal that the SC-GNR requires ~ 3–6× and ~ 2–3× fewer repeaters w.r.t. the TC-GNR or Cu interconnect, and that the SC-GNR and Cu interconnects can achieve ~ 4–5× and ~ 2–2.5× reduction in repeater dimension compared with the TC-GNR interconnect. Meanwhile, the SC-GNR interconnect can achieve 73× less propagation delay w.r.t. the TC-GNR interconnect for interconnect width of 22 nm, interconnect length of 10 μm, and two different chip operating temperatures of 233 K and 300 K. Similarly, the Cu interconnect can achieve 6× less propagation delay w.r.t. the TC-GNR interconnect at interconnect width of 22 nm and 16 nm, interconnect length of 10 μm, and 300 K.

Similar content being viewed by others

References

Fuchs, K.: Conduction electrons in thin metallic films. Proc. Camb. Phil. Soc. 34, 100 (1938)

Sondheimer, E. H.: The MFP of electron in metals. In: Advance in Physics, vol 1(1), pp. 1–42. Taylor & Francis, Routledge (1952)

Mayaddas, A.F., Shatzke, M.: Electrical resistivity model for polycrystalline films: the case of arbitrary reflection at external surfaces. Phys. Rev. B 1(4), 1382–1389 (1970)

Naeemi, A., Meindll, J.D.: Performance benchmarking for graphene nanoribbon, carbon nanotube, and Cu interconnects. In: IITC, pp. 183–185 (2008)

Naeemi, A., Meindl, J.D.: Compact physics-based circuit model for GNR interconnect. IEEE Trans. Electron Devices 56(9), 1822–1833 (2009)

Naeemi, A., Meindl, J.D.: Conductance modeling for GNR interconnect. IEEE Electron Device Lett. 28(5), 428–431 (2007)

Chuan, X., Hong, L., Banerjee, K.: Modeling, analysis, and design of graphene nano-ribbon interconnects. IEEE Trans. Electron Device 56(8), 1567–1578 (2009)

Nasiri, S.H., Farshi, M.K.M., Faez, R.: Stability analysis in graphene nanoribbon interconnects. IEEE Electron Device Lett. 31(12), 1458–1460 (2010)

Tanachutiwat, S., Shuhong, L., Geer, R., Wang, W.: Monolithic graphene nanoribbon electronics for interconnect performance improvement. In: IEEE (ISCAS), pp. 589–592 (2009)

Das, D., Rahaman, H.: Modeling of IR-drop induced delay fault in CNT and GNR power distribution networks. In: CODEC-2012, pp. 1–4 (2012)

Murali, R., Brenner, K., Yang, Y., Beck, T., Meindl, J.D.: Resistivity of graphene nanoribbon interconnects. IEEE Electron Device Lett. 30(6), 611–613 (2009)

Pan, C., Raghavan, P., Ceyhan, A., Catthoor, F., Tokei, Z., Naeemi, A.: Technology/circuit/system co-optimization and benchmarking for multilayer graphene interconnects at sub-10-nm technology node. IEEE Trans. Electron Devices 62(5), 1530–1536 (2015)

Bhattacharya, S., Das, D., Rahaman, H.: Analysis of temperature dependent power supply voltage drop in graphene nanoribbon and Cu based power interconnects. AIMS Mater. Sci. 3, 1493–1506 (2016)

Bhattacharya, S., Das, D., Rahaman, H.: Analysis of delay fault in GNR power interconnects. Int. J. Numer. Modelling Electron. Networks Devices Fields 31(3), 1–16 (2018)

Congs, J.J., Leunge, K.S.: Optimal wire sizing under Elmore delay model. IEEE Trans. Comput. Aided Des. Integr. Circuit Syst 14(3), 321–336 (1995)

Ismail, Y.I., Friedman, E.G., Neves, J.L.: Figures of merit to characterize the importance of on-chip inductance. IEEE Trans. Very Large Scale Integr. Syst. 7(4), 442–449 (1999)

Zhu, Q., Dai, W.M.: High-speed clock network sizing optimization based on distributed RC and lossy RLC interconnect models. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 15(9), 1106–1118 (1996)

El-Moursy, M.A., Friedman, E.G.: Optimum wire sizing of RLC interconnect with repeaters. Integr. VLSI J. 38(2), 205–225 (2004)

Bakoglou, H.B., Mendl, J.D.: Optimal interconnections circuit for VLSI. IEEE Trans. Electron Device 32(5), 903–909 (1985)

Alperte, C.J., Devgane, A., Fishburne, J.P., Quaye, S.T.: Interconnect synthesis without wire tapering. IEEE Trans. Comput. Aided Des. Integr. Circuit Syst. 20(1), 90–104 (2001)

Geim, A.K., Novoselov, K.S.: The rise of graphene. Nat. Mater. 6(3), 183–191 (2007)

Bhattacharya, S., Das, D., Rahaman, H.: Reduced thickness interconnect model using GNR to avoid crosstalk effects. J. Comput. Electron. 15(2), 367–380 (2016)

Kumar, V., Rakheja, S., Naeemi, A.: Performance and energy-per-bit modeling of multilayer graphene nanoribbon conductors. IEEE Trans. Electron Devices 59(10), 2753–2761 (2012)

Leong, W.S., Gong, H., Thong, J.T.L.: Low-contact-resistance graphene devices with nickel–etched–graphene contacts. ACS Nano 8(1), 994–1001 (2014)

Internationals Technology Roadmap for Semiconductors (ITRS-2013) Report. http://www.itrs.net/report.html. Accessed 2018

Goetsch, R.J., Anand, V.K., Pandey, A., Johnston, D.C.: Structural, thermal, magnetic, and electronic transport properties of the LaNi2(Ge1−x Px)2 system. Phys. Rev. B 85(5), 054517 (2012)

Bid, A., Bora, A., Raychaudhuri, A.K.: Temperature dependence of the resistance of metallic nanowires of diameter ≥ 15 nm: applicability of Bloch–Grüneisen theorem. Phys. Rev. B: Condens. Matter Mater. Phys. 3(74), 1–9 (2006)

Nishad, A.K., Sharma, R.: Analytical time-domain models for performance optimization of multilayer GNR interconnects. IEEE J. Sel. Top. Quantum Electron. 20(1), 17–24 (2014)

Bhattacharya, S., Das, D., Rahaman, H.: Stability analysis in top contact and side-contact graphene nanoribbon interconnects. IETE J. Res. 63(4), 588–596 (2017)

Bhattacharya, S., Das, D., Rahaman, H.: Analysis of simultaneous switching noise and IR-drop in side-contact multilayer graphene nanoribbon power distribution network. J. Circuit Syst. Comput. 27(1), 1850001–1850017 (2018)

Funding

SMDP-C2SD, DeitY, MCIT, India.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflicts of interests.

Research involving human participants and/or animals

This article does not contain any studies with human participants or animals performed by any of the authors.

Informed consent

Informed consent was obtained from all individual participants included in the study.

Rights and permissions

About this article

Cite this article

Bhattacharya, S., Das, S., Mukhopadhyay, A. et al. Analysis of a temperature-dependent delay optimization model for GNR interconnects using a wire sizing method. J Comput Electron 17, 1536–1548 (2018). https://doi.org/10.1007/s10825-018-1251-4

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-018-1251-4