Abstract

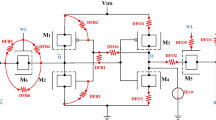

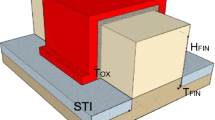

Scaling of metal–oxide–semiconductor field-effect transistors (MOSFETs) to below a few tens of nanometer has failed to make significant improvements. FinFETs were introduced to replace MOS devices in circuits, offering good performance improvement in the nanoscale regime. Memories occupy a major portion of chip area. Their reliability is a primary concern in harsh environments such as cosmic radiation. Also, in the nanoscale regime, reliability proves to be challenging. We present herein FinFET- and junctionless FinFET-based 6T-static random-access memories (SRAMs) for the 16-nm technology node. In the literature so far, either drain or gate strike has been considered. In this work, we studied irradiation in both the drain and the gate region. The FinFET-based 6T-SRAM showed higher hardness to single-event upset (SEU) radiation in both regions compared to junctionless FinFET-based 6T-SRAM.

Similar content being viewed by others

References

Kuhn, K.J.: Considerations for ultimate CMOS scaling. IEEE Trans. Electron Devices 59, 1813–1828 (2012)

Lin C.H., Chang J., Guillorn M., Bryant A., Haensch P.O.W.: Non-planar device architecture for 15 nm node: FinFET or trigate?. In: SOI Conference (SOI) IEEE International San Diego, CA, pp. 1–2 (2010)

Lee, C.W., Afzalian, A., Akhavan, N.D., Yan, R., Ferain, I., Colinge, J.P.: Junctionless multigate field-effect transistor. Appl. Phys. Lett. 94, 053511-1–053511-2 (2009)

Kranti A., Yan R., Lee C. W., Ferain I., Yu R., Akhavan D.N., Razavi P., Colinge J.P.: Junctionless nanowire transistor (JNT): properties and design guidelines. In: 2010 Proceedings of the European Solid State Device Research Conference, pp. 357–360 (2010)

Price, W.E., Nichols, D.K., Soliman, K.A.: A study of single event upsets in static RAMS’s. IEEE Trans. Nucl. Sci. 27, 1506–1508 (1980)

Dodd, P.E.: Device simulation of charge collection and single-event upset. IEEE Trans. Nucl. Sci. 43, 561–575 (1996)

Munteanu, D., Autran, J.L.: Modeling and simulation of single-event effects in digital devices and ICs. IEEE Trans. Nucl. Sci. 55, 1854–1878 (2008)

Simoen, E., Gaillardin, M., Paillet, P., Reed, R.A., Schrimpf, R.D., Alles, A.L., El-Mamouni, F., Fleetwood, D.M., Griffoni, A., Claeys, C.: Radiation effects in advanced multiple gate and silicon-on-insulator transistors. IEEE Trans. Nucl. Sci. 60, 1970–1991 (2013)

Baumann, R.C.: Radiation-induced soft errors in advanced semiconductor technologies. IEEE Trans. Device Mater. Reliab. 5, 305–316 (2005)

Warren, K.M., Weller, R.A., Mendenhall, M.H., Reed, R.A., Ball, D.R., Howe, C.L., Olson, B.D., Alles, M.L., Massengill, L.W., Schrimpf, R.D., Haddad, N.F., Doyle, S.E., McMorrow, D., Melinger, J.S., Lotshaw, W.T.: The contribution of nuclear reactions to heavy ion single event upset cross-section measurements in a high-density SEU hardened SRAM. IEEE Trans. Nucl. Sci. 52, 2125–2131 (2005)

Munteanu D., Autran J.L.: 3D numerical simulation of bipolar amplification in junctionless double-gate MOSFETs under heavy-ion irradiation. In: 12th European Conference on Radiation and Its Effects on Components and Systems, pp. 73–76 (2011)

Esqueda, I.S., Barnaby, H.J., Holbert, K.E., El-Mamouni, F., Schrimpf, R.D.: Modeling of ionizing radiation-induced degradation in multiple gate field effect transistors. IEEE Trans. Nucl. Sci. 58, 499–505 (2011)

El-Mamouni, F., Zhang, E.X., Ball, D.R., Sierawski, B., King, M.P., Schrimpf, R.D., Reed, R.A., Alles, M.L., Fleetwood, D.M., Linten, D., Simoen, E., Vizkelethy, G.: Heavy-ion-induced current transients in bulk and SOI FinFETs. IEEE Trans. Nucl. Sci. 59, 2674–2681 (2012)

Meinhardt, C., Zimpeck, A.L., Reis, R.A.L.: Predictive evaluation of electrical characteristics of sub-22 nm FinFET technologies under device geometry variations. Microelectron. Reliab. 54, 2319–2324 (2014)

The ITRS website. http://public.itrs.net. Accessed July 2015

User Manual Version K-2015.06 Synopsys TCAD Sentaurus Synopsys 2015

Artola L., Hubert G., Schrimpf R.D.: Modeling of radiation-induced single event transients in SOI FinFETS. In: Reliability Physics Symposium (IRPS) SE.1.1–SE.1.6 (2013)

Dodd, P.E., Sexton, F.W.: Critical charge concepts for CMOS SRAMs. IEEE Trans. Nucl. Sci. 42, 1764–1771 (1995)

Ramakrishnan, V.N., Srinivasan, R.: Soft error study in double gated FinFET-based SRAM cells with simultaneous and independent driven gates. Microelectron. J. 43, 888–893 (2012)

Ramakrishnan, V.N., Srinivasan, R.: Effect of underlap and soft error performance in 30 nm FinFET-based 6T-SRAM cells with simultaneous and independent driven gates. J. Comput. Electron. 12, 469–475 (2013)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Nilamani, S., Ramakrishnan, V.N. Gate and drain SEU sensitivity of sub-20-nm FinFET- and Junctionless FinFET-based 6T-SRAM circuits by 3D TCAD simulation. J Comput Electron 16, 74–82 (2017). https://doi.org/10.1007/s10825-016-0950-y

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-016-0950-y