Abstract

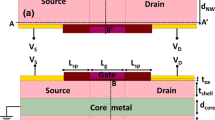

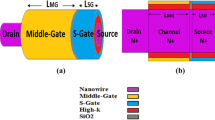

We present a detailed study on a technique to realize a narrow and highly doped built-in \({n}^{+}\) source pocket in an asymmetric junctionless nanowire tunnel field-effect transistor (AJN-TFET). In the proposed structure, a built-in \({n}^{+}\) source pocket is created between the \({p}^{+}\) source and the channel without the need for any separate implantation or epitaxial growth. This leads to band diagram modification by providing a local minimum in the conduction band which results in tunneling width reduction at the source–channel interface in on-state. This leads to an abrupt transition between on- and off-state, improved subthreshold swing (SS) (38 mV/dec), and significant on-current enhancement (\(\sim 2000\) times) at low operating voltage compared with the conventional TFET. We further study the effect of the length of the built-in \({n}^{+}\) source pocket on the AJN-TFET characteristics. The proposed structure overcomes the difficulty in creating a narrow \({n}^{+}\) pocket and thus renders the AJN-TFET device more amenable for the future scaling trend needed in low-power applications.

Similar content being viewed by others

References

Rahimian, M., Orouji, A.A.: Nanoscale SiGe-on-insulator (SGOI) MOSFET with graded doping channel for improving leakage current and hot-carrier degradation. Superlattices Microstruct. 50, 667–679 (2011)

Rahimian, M., Orouji, A.A., Aminbeidokhti, A.: A novel deep submicron SiGe-on-insulator (SGOI) MOSFET with modified channel band energy for electrical performance improvement. Curr. Appl. Phys. 13, 779–784 (2013)

Orouji, A.A., Rahimian, M.: Leakage current reduction in nanoscale fully-depleted SOI MOSFETs with modified current mechanism. Curr. Appl. Phys. 12, 1366–1371 (2012)

Chang, H.Y., Adams, B., Chien, P.Y., Li, J., Woo, J.C.S.: Improved subthreshold and output characteristics of source-pocket Si tunnel FET by the application of laser annealing. IEEE Trans. Electron Devices 60(1), 92–96 (2013)

Jhaveri, R., Nagavarapu, V., Woo, J.C.S.: Effect of pocket doping and annealing schemes on the source-pocket tunnel field-effect transistor. IEEE Trans. Electron Devices 58(1), 80–86 (2011)

Tura, A., Zhang, Z., Liu, P., Xie, Y.H., Woo, J.C.S.: vertical silicon p–n–p–n tunnel n MOSFET With MBE-grown tunneling junction. IEEE Trans. Electron Devices 58(7), 1907–1913 (2011)

Nikonov, D.E., Young, I.A.: Benchmarking of beyond-CMOS exploratory devices for logic integrated circuits. IEEE J. Exp. Solid. State Comput. Devices Circuits 1, 3–11 (2015)

Ionescu, A.M., Riel, H.: Tunnel field-effect transistors as energy efficient electronic switches. Nature 479(7373), 329–337 (2011)

Reddick, W., Amaratunga, G.: Silicon surface tunnel transistor. Appl. Phys. Lett. 67(4), 494–496 (1995)

Choi, W.Y., Park, B.G., Lee, J.D., Liu, T.J.K.: Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett. 28(8), 743–745 (2007)

Zhang, Q., Zhao, W., Seabaugh, A.: Low-subthreshold-swing tunnel transistors. IEEE Electron Device Lett. 27(4), 297–300 (2006)

Appenzeller, J., Lin, Y.M., Knoch, J., Chen, Zh, Avouris, Ph: Comparing carbon nanotube transistors-the ideal choice: a novel tunneling device design. IEEE Trans. Electron Devices 52(12), 2568–2576 (2005)

Ilatikhameneh, H., Klimeck, G., Rahman, R.: Can homojunction tunnel FETs scale below 10 nm? IEEE Electron Device Lett. 37(1), 115–118 (2016)

Shin, C.H.H., Kien, N.V.: Sub-10-nm asymmetric junctionless tunnel field-effect transistors. IEEE J. Electron Devices Soc. 2(5), 128–132 (2014)

Cui, N., Liang, R., Wang, J., Xu, J.: Lateral energy band profile modulation in tunnel field effect transistors based on gate structure engineering. AIP Adv. 2, 022111 (2012)

Shih, C.H.H., Chien, N.D.: Physical operation and device design of short-channel tunnel field-effect transistors with graded silicon-germanium heterojunctions. J. Appl. Phys. 113, 134507 (2013)

Shih, C.H.H., Chien, N.D.: Sub-10-nm tunnel field-effect transistor with graded Si/Ge heterojunction. IEEE Electron Device Lett. 32(11), 1498–1500 (2011)

Toh, E.H., Wang, G.H., Samudra, G., Yeo, YCh.: Device physics and design of germanium tunneling field-effect transistor with source and drain engineering for low power and high performance applications. J. Appl. Phys. 103, 104504 (2008)

Khatami, Y., Banerjee, K.: Steep subthreshold slope n- and p-type tunnel-FET devices for low-power and energy-efficient digital circuits. IEEE Trans. Electron Devices 56(11), 2752–2761 (2009)

Bhuwalka, K.K., Schulze, J., Eisele, I.: Scaling the vertical tunnel FET with tunnel bandgap modulation and gate workfunction engineering. IEEE Trans. Electron Devices 52(5), 909–917 (2005)

Asthana, P.K., Ghosh, B., Goswami, Y., Tripathi, B.M.M.: High-speed and low-power ultra deep-submicrometer III–V heterojunctionless tunnel field-effect transistor. IEEE Trans. Electron Devices 61(2), 479–485 (2014)

Imen Abadi, R.M., Ali, S., Ziabari, S.: Representation of type I heterostructure junctionless tunnel field effect transistor for high-performance logic application. Appl. Phys. A. 122, 616–622 (2016)

Imen Abadi, R.M., Ali, S., Ziabari, S.: Representation of strained gate-all-around junctionless tunneling nanowire filed effect transistor for analog applications. Microelectron. Eng. 162, 12–16 (2016)

Saurabh, S., Kumar, M.J.: Impact of strain on drain current and threshold voltage of nanoscale double gate tunnel field effect transistor: theoretical investigation and analysis. Jpn. J. Appl. Phys. 48, 064503 (2009)

Nagavarapu, V., Jhaveri, R., Woo, J.C.S.: The tunnel source (PNPN) n-MOSFET: a novel high performance transistor. IEEE Trans. Electron Devices 55(4), 1013–1019 (2008)

Cho, S., Kang, I.M.: Design optimization of tunneling field-effect transistor based on silicon nanowire PNPN structure and its radio frequency characteristics. Curr. Appl. Phys. 12, 673–677 (2012)

Cao, W., Yao, C.J., Jiao, G.F., Huang, D., Yu, H.Y., Li, M.F.: Improvement in reliability of tunneling field-effect transistor with p-n-i-n structure. IEEE Trans. Electron Devices 58(7), 2122–2126 (2011)

Saurabh, S., Kumar, M.J.: Novel attributes of a dual material gate nanoscale tunnel field-effect transistor. IEEE Trans. Electron Devices 58(2), 404–410 (2011)

Cui, N., Liang, R., Xu, J.: Heteromaterial gate tunnel field effect transistor with lateral energy band profile modulation. Appl. Phys. Lett. 98, 142105 (2011)

Bal, P., Ghosh, B., Mondal, P., Akram, M.W., Tripathi, B.M.M.: Dual material gate junctionless tunnel field effect transistor. J. Comput. Electron 13(1), 230–234 (2014)

Rama, M.S., Abdi, D.B.: Dopingless PNPN tunnel FET with improved performance: design and analysis. Superlattices Microstruct. 82, 430–437 (2015)

Choi, W.Y., Lee, W.: Hetero-gate-dielectric tunneling field-effect transistors. IEEE Trans. Electron Devices 57(9), 2317–2319 (2010)

Mitra, S.K., Goswami, R., Bhowmick, B.: A hetero-dielectric stack gate SOI-TFET with back gate and its application as a digital inverter. Superlattices Microstruct. 92, 37–51 (2016)

Abdi, D.B., Kumar, M.J.: In-built N\(^{+}\) pocket p–n–p–n tunnel field-effect transistor. IEEE Electron Device Lett. 35(12), 1170–1172 (2014)

Boucart, K., Ionescu, A.M.: Double-gate tunnel FET with high-K gate dielectric. IEEE Trans. Electron Devices 54(7), 1725–1733 (2007)

Anghel, C., Chilagani, P., Amara, A., Vladimirescu, A.: Tunnel field effect transistor with increased on current, low-k spacer and high-k dielectric. Appl. Phys. Lett. 96, 122104 (2010)

Ilatikhameneh, H., Ameen, T.A., Klimeck, G., Appenzeller, J., Rahman, R.: Dielectric engineered tunnel field-effect transistor. IEEE Electron Device Lett. 36(10), 1097–1100 (2015)

Abdi, D.B., Kumar, M.J.: Controlling ambipolar current in tunneling FETs using overlapping gate-on-drain. IEEE J. Electron Devices Soc. 2(6), 187–190 (2014)

Sahay, S., Kumar, M.J.: Controlling the drain side tunneling width to reduce ambipolar current in tunnel FETs using heterodielectric BOX. IEEE Trans. Electron Devices 62(11), 3882–3886 (2015)

Leonelli, D., Vandooren, A., Rooyackers, R., Gendt, S.D., Heyns, M.M., Groeseneken, G.: Drive current enhancement in p-tunnel FETs by optimization of the process conditions. Solid State Electron. 66, 28–32 (2011)

Chang, H.Y., Chopra, S., Adams, B., Li, J., Sharma, S., Kim, Y., Moffatt, S., Woo, J.C.S.: Improved subthreshold characteristics in tunnel field-effect transistors using shallow junction technologies. Solid State Electron. 80, 59–62 (2013)

Damrongplasit, N., Shin, C.H., Kim, S.H., Vega, R.A., Liu, T.J.K.: Study of random dopant fluctuation effects in germanium-source tunnel FETs. IEEE Trans. Electron Devices 58(10), 3541–3548 (2011)

Damrongplasit, N., Kim, S.H., Liu, T.J.K.: Study of random dopant fluctuation induced variability in the raised-Ge-source TFET. IEEE Electron Device Lett. 34(2), 184–186 (2013)

Kumar, M.J., Janardhanan, S.: Doping-less tunnel field effect transistor: design and investigation. IEEE Trans. Electron Devices 60(10), 3285–3290 (2013)

Ghosh, B., Akram, M.W.: Junctionless tunnel field effect transistor. IEEE Electron Device Lett. 34(5), 584–586 (2013)

Bal, P., Akram, M.W., Mondal, P., Ghosh, B.: Performance estimation of sub-30 nm junctionless tunnel FET (JLTFET). J. Comput. Electron. 12(4), 782–789 (2013)

Gundapaneni, S., Goswami, A., Badami, O., Cuduvally, R., Konar, A., Bajaj, M., Murali, K.V.R.M.: Tunneling-triggered bipolar action in junctionless tunnel field-effect transistor. Appl. Phys. Express 7, 124302 (2014)

Colinge, J.P., Lee, C.W., Afzalian, A., Akhavan, N.D., Yan, R., Ferain, I., Razavi, P., O’Neill, B., Blake, A., White, M., Kelleher, A.M., McCarthy, B., Murphy, R.: Nanowire transistors without junctions. Nat. Nanotechnol. 5(3), 225–229 (2010)

Gnani, E., Gnudi, A., Reggiani, S., Baccarani, G.: Theory of the junctionless nanowire FET. IEEE Trans. Electron Devices 58(9), 2903–2910 (2011)

Omura, Y., Horiguchi, S., Tabe, M., Kishi, K.: Quantum-mechanical effects on the threshold voltage of ultrathin-SOI nMOSFETs. IEEE Electron Device Lett. 14(12), 569–571 (1993)

Verreck, D., Verhulst, A.S., Kao, K.H., Vandenberghe, W.G., Meyer, K.D., Groeseneken, G.: Quantum mechanical performance predictions of p-n-i-n versus pocketed line tunnel field-effect transistors. IEEE Trans. Electron Devices 60(7), 2128–2134 (2013)

ATLAS device simulation software. Silvaco, Santa Clara (2015)

Kane, E.O.: Theory of tunneling. J. Appl. Phys. 32(1), 83–91 (1961)

Kane, E.O.: Zener tunneling in semiconductors. J. Phys. Chem. Solids 12(2), 181–188 (1960)

Schenk, A.: A model for the field and temperature dependence of SRH lifetimes in silicon. Solid State Electron. 35, 1585–1596 (1992)

Acknowledgments

The authors would like to acknowledge partial support by Nanoelectronic Center of Excellence, department of electrical and computer engineering at University of Tehran.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Rahimian, M., Fathipour, M. Asymmetric junctionless nanowire TFET with built-in \({n}^{+}\) source pocket emphasizing on energy band modification. J Comput Electron 15, 1297–1307 (2016). https://doi.org/10.1007/s10825-016-0895-1

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-016-0895-1