Abstract

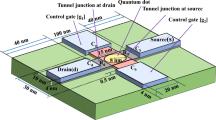

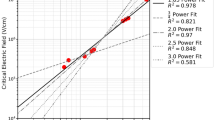

The ongoing trend of device dimension miniaturization is attributed to a large extent by the development of several non-conventional device structures among which tunneling field effect transistors (TFETs) have attracted significant research attention due to its inherent characteristics of carrier conduction by built-in tunneling mechanism which in turn mitigates various short channel effects (SCEs). In this work, we have, incorporated the innovative concept of work function engineering by continuously varying the mole fraction in a binary metal alloy gate electrode along the horizontal direction into a double gate tunneling field effect transistor (DG TFET), thereby presenting a new device structure, a work function engineered double gate tunneling field effect transistor (WFEDG TFET). We have presented an explicit analytical surface potential modeling of the proposed WFEDG TFET by the solving the 2-D Poisson’s equation. From the surface potential expression, the electric field has been derived which has been utilized to formulate the expression of drain current by performing rigorous integration on the band-to-band tunneling generation rate over the tunneling region. Based on this analytical modeling, an overall performance comparison of our proposed WFEDG TFET with its normal DG TFET counterpart has been presented in this work to establish the superiority of our proposed structure in terms of surface potential and drain current characteristics. Analytical results have been compared with SILVACO ATLAS device simulator results to validate our present model.

Similar content being viewed by others

References

Vishnoi, Rajat, Kumar, M.J.: Compact analytical model of dual material gate tunneling field effect transistor using interband tunneling and channel transport. IEEE Trans. Electron Devices 61, 1936–1942 (2014)

Gholizadeh, M., Hosseini, S.E.: A 2-D analytical model for double-gate tunnel FETs. IEEE Trans. Electron Devices 61(5), 1494–1500 (2014)

Yadav, M., Bulusu, A., Dasgupta, S.: Two dimensional analytical modeling for asymmetric 3T and 4T double gate tunnel FET in sub-threshold region: Potential and electric field. Microelectron. J. 44, 1251–1259 (2013)

Boucart, K., Ionescu, A.: Double-gate tunnel FET with high-k gate dielectric. IEEE Trans. Electron Devices 54(7), 1725–1733 (2007)

Mookerjea, S., Mohata, D., Mayer, T., Narayanan, V., Datta, S.: Temperature dependent I–V characteristics of a vertical In0.53Ga0.47As tunnel FET. IEEE Electron Device Lett. 31(6), 564–566 (2010)

Born, M., Bhuwalka, K., Schindler, M., Ubelein, U., Schmidt, M., Sulima, T., Eisele, I.: Tunnel FET: a CMOS device for high temperature application. In: Proceedings of 25th International Conference on Microelectronics (MIEL2006), pp. 14–17 (2006)

Toh, E.-H., Wang, G.H., Samudra, G., Yeo, Y.C.: Device physics and design of germanium tunneling field-effect transistor with source and drain engineering for low power and high performance applications. J. Appl. Phys. 103(10), 104504–104504-5 (2008)

International Technology Roadmap for Semiconductor. http://www.itrs.net/

Vishnoi, R., Kumar, M.J.: A pseudo 2D-analytical model of dual material gate all-around nanowire tunneling FET. IEEE Trans. Electron Devices 61, 2264–2270 (2014)

Verhulst, A.S., Sorée, B., Leonelli, D., Vandenberghe, W.G., Groeseneken, G.: Modeling the single-gate, double-gate, and gate-all-around tunnel field-effect transistor. J. Appl. Phys. 107, 024518 (2010)

Vandenberghe, W.G., Verhulst, A.S., Groeseneken, G., Magnus, W.: Analytical model for a tunnel field-effect transistor. In: Electrotechnical Conference, MELECON, pp. 923–928 (2008)

Shen, C., Ong, S.-L., Heng, C.-H., Samudra, G., Yeo, Y.-C.: A variational approach to the two-dimensional nonlinear Poisson’s equation for the modeling of tunneling transistors. IEEE Electron Device Lett. 29(11), 1252–1255 (2008)

Deb, S., Singh, N.B., Islam, N., Sarkar, S.K.: Work function engineering with linearly graded binary metal alloy gate electrode for short channel SOI MOSFET. IEEE Trans. Nanotechnol. 11(3), 472–478 (2012)

Manna, B., Sarkhel, S., Islam, N., Sarkar, S., Sarkar, Subir Kumar: Spatial composition grading of binary metal alloy gate electrode for short-channel SOI/SON MOSFET application. IEEE Trans. Electron Devices 59(12), 3280–3287 (2012)

Sarkhel, S., Sarkar, S.K.: A comprehensive two dimensional analytical study of a nanoscale linearly graded binary metal alloy gate cylindrical junctionless MOSFET for improved short channel performance. J. Comput. Electron. 13(4), 925–932 (2014)

Sarkhel, S., Manna, B., Sarkar, S.K.: Analytical modeling and simulation of a linearly graded binary metal alloy gate nanoscale cylindrical MOSFET for reduced short channel effects. J. Comput. Electron. 13(3), 599–605 (2014)

Sarkhel, S., Sarkar, S.K.: A compact Quasi 3D threshold voltage modeling and performance analysis of a novel linearly graded binary metal alloy Quadruple gate MOSFET for subdued short channel effects. Superlattices Microstruct. 82, 293–302 (2015). doi:10.1016/j.spmi.2015.01.035

Bhattacharyya, G., Shee, S., Sarkar, S.K.: Comprehensive quantum mechanical modeling of short channel SON MOSFET with spatial composition grading of binary metal alloy gate electrode. Superlattices Microstruct. 83, 676–689 (2015)

Lee, C.K., Kim, J.Y., Hong, S.N., Zhong, H., Chen, B., Mishra, V.: Properties of Ta–Mo alloy gate electrode for n-MOSFET. J. Mater. Sci. 40, 2693–2695 (2005)

Ishii, R., Matsumura, K., Sakai, A., Sakata, T.: Work function of binary alloys. Appl. Surf. Sci. 169–170, 658–661 (2001)

Gelatt, C.D., Ehrenreich, H.: Charge transfer in alloys: AgAu. Phys. Rev. B 10(2), 398 (1974)

Tsui, B.-Y., Huang, C.-F.: Wide range work function modulation of binary alloys for MOSFET application. IEEE Electron Device Lett. 24(3), 153–155 (2003)

Pan, A., Liu, R., Sun, M., Ning, C.-Z.: Spatial composition grading of quaternary ZnCdSSe alloy nanowires with tunable light emission between 350 and 710 nm on a single substrate. ACS Nano 4(2), 671–680 (2010)

Ohkubo, I., Christen, H.M., Khalifah, P., Sathyamurthy, S., Zhai, H.Y., Rouleau, C.M., Mandrus, D.G., Lowndes, D.H.: Continuous composition-spread thin films of transition metal oxides by pulsed-laser deposition. Appl. Surf. Sci. 223, 35–38 (2004)

Christen, H.M., Rouleau, C.M., Ohkubo, I., Zhai, H.Y., Lee, H.N., Sathyamurthy, S., Lowndes, D.H.: An improved continuous compositional-spread technique based on pulsed-laser deposition and applicable to large substrate areas. Rev. Sci. Instrum. 74, 4058–4062 (2003)

Young, K.K.: Short-channel effects in fully depleted SOI MOSFET’s. IEEE Trans. Electron Devices 36, 399–402 (1989)

Narang, R., Saxena, M., Gupta, R.S., Gupta, M.: Drain current model for a gate all around (GAA) p-n-p-n tunnel FET. Microelectron. J. 44, 479–488 (2013)

Kane, E.O.: Theory of tunneling. J. Appl. Phys. 32(1), 83–91 (1961)

Khatami, Y., Banerjee, K.: Steep subthreshold slope n- and p-type tunnel-FET devices for low-power and energy-efficient digital circuits. IEEE Trans. Electron Devices 56(11), 2752–2761 (2009)

Verhuslt, A.S., Leonelli, D., Rooyackers, R., Groeseneke, G.: Drain voltage dependent analytical model of tunnel field effect transistors. J. Appl. Phys. 110, 024510 (2011)

Bagga, N., Sarkar, S.K.: An analytical model for tunnel barrier modulation in triple metal double gate TFET. IEEE Trans. Electron Devices 62(7), 2136–2142 (2015)

ATLAS User’s Manual: Silvaco Inc. Santa Clara, CA (2010)

Arun, T.S., Balamurugan, N.B.: An analytical modeling and simulation of dual material double gate tunnel field effect transistor for low power applications. J. Electr. Eng. Technol. 9(1), 247–253 (2014)

Lee, M.J., Choi, W.Y.: Analytical model of single-gate silicon-on-insulator (SOI) tunneling field-effect transistors (TFETs). Solid-State Electron. 63, 110–114 (2011)

Acknowledgments

Saheli Sarkhel thankfully acknowledges the financial support obtained in the form of State Research Fellowship from the Department of Electronics and Telecommunication Engineering, Jadavpur University.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Sarkhel, S., Bagga, N. & Sarkar, S.K. Compact 2D modeling and drain current performance analysis of a work function engineered double gate tunnel field effect transistor. J Comput Electron 15, 104–114 (2016). https://doi.org/10.1007/s10825-015-0772-3

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-015-0772-3