Abstract

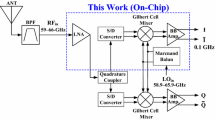

High carrier frequency requirement (Sub 6, 28 GHz) to accomplish the high bandwidth specification for millimeter wave band wireless communication, has reduced the ratio of operating carrier frequency (fc) and unity current gain frequency (ft) of MOSFETs in state of the art RFCMOS technology. This poses a challenge for designing a high gain and low noise receiver with better linearity. In an attempt to realize such receiver, this paper presents a 28 GHz receiver front-end in 40 nm RFCMOS technology. It includes 3-stage low noise amplifier incorporating push pull topology, current bleeding down converting gilbert cell based mixer with common gate transconductance stage followed by a standard Gm-C filter. By incorporating these techniques, the performance of the proposed receiver improved in terms of linearity as compared to the state of the art designs. For a comprehensive analysis, the combined effect of performance parameters has been compiled into a single metric i.e. Figure of Merit (FOM). The proposed receiver exhibits conversion gain of 30.5 dB and 2.15 dB noise figure with linearity parameter IIP3 being −21.7 dBm while consuming 36.7mW power resulting in FOM value of 0.27.

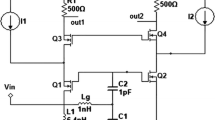

source transconductance stage mixer

Similar content being viewed by others

References

Li, Q. C., et al. (2014). 5G network capacity: Key elements and technologies. IEEE Vehicular Technology Magazine, 9(1), 71–78.

Al-Falahy, N., & Alani, O. Y. (2017). Technologies for 5G networks: Challenges and opportunities. IT Professional, 19(1), 12–20.

Tao, S., et al. (2011). A 60 GHz receiver front-end in 65 nm CMOS. Analog integrated circuits and Signal processing, 67(1), 61–71.

Rappaport, T. S., et al. (2017). Overview of millimeter wave communications for fifth-generation (5G) wireless networks—With a focus on propagation models. IEEE Transactions on Antennas and Propagation, 65(12), 6213–6230.

Narayan, C. P. (2007). Antennas and propagation. Pune: Technical Publications.

Axholt, A., & Sjöland, H. (2014). A 60 GHz receiver front-end with PLL based phase controlled LO generation for phased-arrays. Analog Integrated Circuits and Signal Processing, 80(1), 23–32.

Lin, Y. S., et al. (2012). Design and analysis of a 21–29-GHz ultra-wideband receiver front-end in 0.18 µm CMOS technology. IEEE Transactions on Microwave Theory and Techniques, 60(8), 2590–2604.

Chu CY, et al. "A 24GHz low-power CMOS receiver design." 2008 IEEE International Symposium on Circuits and Systems. IEEE, (2008).

Min, B.-W., & Rebeiz, G. M. (2008). Single-ended and differential Ka-band BiCMOS phased array front-ends. IEEE Journal of Solid-State Circuits, 43(10), 2239–2250.

Chen, Y.-H., Hsieh, H.-H., & Liang-Hung, Lu. (2008). A 24-GHz receiver frontend with an LO signal generator in 0.18 µm CMOS. IEEE Transactions on Microwave Theory and Techniques, 56(5), 1043–1051.

Guan, X., & Hajimiri, A. (2004). A 24-GHz CMOS front-end. IEEE Journal of Solid-State Circuits, 39(2), 368–373.

Garg, R., & Natarajan, A. S. (2017). A 28-GHz low-power phased-array receiver front-end with 360° RTPS phase shift range. IEEE Transactions on Microwave Theory and Techniques, 65(11), 4703–4714.

Razavi, B. (1998). RF microelectronics. ChinnaChokikulam: Prentice Hall PTR.

Douss, S., Touati, F., & Loulou, M. (2008). An RF-LO current-bleeding doubly balanced mixer for IEEE 802.15. 3a UWB MB-OFDM standard receivers. AEU-International Journal of Electronics and Communications, 62(7), 490–495.

Voinigescu, S. (2013). High-frequency integrated circuits. Cambridge: Cambridge University Press.

Khanpour, M., Tang, K. W., Garcia, P., & Voinigescu, S. P. (2008). A wideband W-band receiver front-end in 65-nm CMOS. IEEE Journal of Solid-State Circuits, 43(8), 1717–1730.

Zhenying, L. Z. L., Rustagi, S. C., Li, M. F., & Lian, Y. L. Y. (2003). A 1V, 2.4 GHz fully integrated LNA using 0.18 μm CMOS technology. In ASIC, 2003. Proceedings of 5th international conference on Vol. 2, pp. 1062–1065.

Ankita Verma, et.al. A differential LNA architecture with improved Figure of Merit using 40nm UMC Technology for mm wave band receiver applications [communicated].

Bijari, A., & Zandian, S. (2019). Linearity improvement in a CMOS down-conversion active mixer for WLAN applications. Analog Integrated Circuits and Signal Processing, 100(2), 483–493.

Xuan, Kai, et al. "High-performance current bleeding CMOS mixer." Electronics letters 45.19 (2009): 979–981.

Yang, Jenn-Tzer, et al. (2008) A 2. 4 GHz low power highly linear mixer for direct-conversion receivers. Proceedings of the WSEAS international conference on mathematics and computers in science and engineering. No. 8. World Scientific and Engineering Academy and Society.

Douss, S., Touati, F., & Loulou, M. (2007). Design optimization methodology of CMOS active mixers for multi-standard receivers. Int. J. Electron. Circuits Syst, 1(1), 1–9.

Lee, Wah Ching, and Kim Fung Tsang. (2018) Design of a 2.4 GHz high-performance mixer with current bleeding topology. Proceedings of the 2018 20th International Conference on Advanced Communication Technology (ICACT). IEEE

Allen, P. E., & Holberg, D. R. (2011). CMOS analog circuit design. Cambridge: Oxford University Press.

Kundu, S., & Paramesh, J. (2015). A Transformer-neutralized 0.6 V V DD 17–29 GHz LNA and its application to an RF front-end. Analog Integrated Circuits and Signal Processing, 83(2), 173–186.

Kim, S., Kim, B., Lee, Y., Kim, S., & Shin, H. (2019). A 28GHz direct conversion receiver in 65nm CMOS for 5G mm wave radio. Proceedings of the 2019 International SoC Design Conference (ISOCC) IEEE. pp. 29–30

Wu, C.-Y., Wang, W.-C., Shahroury, F. R., Huang, Z.-D., & Zhan, H.-J. (2009). Current-mode design techniques in low-voltage 24-GHz RF CMOS receiver front-end. Analog Integrated Circuits and Signal Processing, 58(3), 183–195.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Verma, A., Yadav, P.K., Ambulker, S. et al. A 36.7 mW, 28 GHz receiver frontend using 40 nm RFCMOS technology with improved Figure of Merit. Analog Integr Circ Sig Process 107, 135–144 (2021). https://doi.org/10.1007/s10470-020-01792-w

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-020-01792-w