Abstract

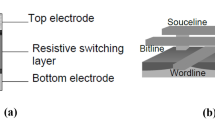

Static Random-Access Memories (SRAMs) have flourished in the memory market relying on their speed, power consumption and compatibility with standard CMOS process technology. Conventional SRAMs are characterized by volatility, limiting their role in applications where non-volatility is essential. Non-Volatile SRAMs (NVSRAMs) represent an appealing solution, where Resistive RAM (RRAM) can act as a non-volatile element for SRAM. RRAM relies on the basic physical phenomenon of operation called resistive switching. This paper presents different NVSRAM structures, while exploring their principle of operation. Also, a comparison in terms of area, speed, power consumption and design complexity is presented for three NVSRAM memory cells implemented in a 130-nm high voltage CMOS technology from STMicroelectronics.

Similar content being viewed by others

References

Lue, H.-T., Hsiao, Y.-H., Hsieh, K.-Y., Wang, S.-Y., Yang, T., Chen, K.-C., & Lu, C.-Y. (2011). Scaling feasibility study of planar thin floating gate (FG) NAND flash devices and size effect challenges beyond 20 nm. In IEDM Tech. Dig. (pp. 203–206).

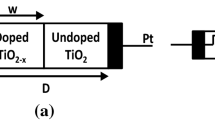

Ielmini, D. (2016). Resistive switching memories based on metal oxides: Mechanisms, reliability and scaling. Semiconductor Science and Technology, 31(6), 063002.

Akerman, J. (2005). Applied physics: Toward a universal memory. Science, 308(5721), 508–510.

Waser, R., & Aono, M. (2007). Nanoionics-based resistive switching memories. Nature Materials, 6(11), 833–840.

Banerjee, A. (2018). Ultra-low-power embedded SRAM design for battery-operated and energy-harvested IoT applications. In C. Ravariu and D. Mihaiescu (Ed.), Green Electronics, Rijeka: IntechOpen. https://doi.org/10.5772/intechopen.76765.

Sterpone, L., et al. (2011). A new reconfigurable clock-gating technique for low power SRAM-based FPGAs. In 2011 design, automation and test in Europe, Grenoble (pp. 1–6)

Singh, P., et al. (2017). Ultra-low power, process-tolerant 10T (PT10T) SRAM with improved read/write ability for internet of things (IoT) applications. Journal of Low Power Electronics and Applications, 7, 24.

Dou, C., et al. (2017) In IEEE 12th international conference on ASIC (ASICON).

Portal, J.-M., et al. (2014). RRAM-based FPGA for “An overview of non-volatile flip-flops based on emerging memory technologies. Journal of Electronic Science and Technology, 12(2), 173–181.

Wong, H. S. P., & Salahuddin, S. (2015). Memory leads the way to better computing. Nature Nanotechnology, 10, 191–194.

Meena, J. S., Sze, S. M., Chand, U., et al. (2014). Overview of emerging nonvolatile memory technologies. Nanoscale Research Letters, 9, 526. https://doi.org/10.1186/1556-276X-9-526.

Bazzi, H., et al. (2018). Novel RRAM CMOS non-volatile memory cells in 130 nm Technology. In 2018 international conference on computer and applications (ICCA), Beirut (pp. 390–393).

Benoist, A., et al. (2014). 28nmadvancedCMOS resistive RAM solution as embedded non-volatile memory. In 2014 IEEE international reliability physics symposium (pp. 2E.6.1–2E.6.5).

Bazzi, H., et al. (2018). Novel RRAM CMOS non-volatile memory cells in 130 nm technology (pp. 390–393). ICCA: Beirut.

Waser, R. (2009). Resistive non-volatile memory devices (Invited Paper). Microelectronic Engineering, 86, 1925–1928.

Clima, S., et al. (2015). Intrinsic tailing of resistive states distributions in amorphous HfOx and TaOx based resistive random access memories. IEEE Electron Device Letters, 36(8), 769–771.

Chen, Y., & Petti, C. (2016). ReRAM technology evolution for storage class memory application. In 2016 46th European solid-state device research conference (ESSDERC), Lausanne (pp. 432–435).

Zhu, L., et al. (2015). An overview of materials issues in resistive random-access memory. Journal of Materiomics, 1(4), 285–295.

Kang, J., et al. (2015). Peking University-Stanford University Resistive Random-Access Memory (RRAM) SPICE Model Version: 2.0Beta. Patent Pending., Copyright Peking University and Stanford University, 2015 All rights reserved.

Hajri, B., et al. (2017). Oxide-based RRAM models for circuit designers: A comparative analysis. In: 2017 12th international conference on design & technology of integrated systems in nanoscale era (DTIS), Palma de Mallorca (pp. 1–6).

Hajri, B., et al. (2019). RRAM device models: a comparative analysis with experimental validation. IEEE Access, 7, 168963–168980.

Guan, X., et al. (2012). A SPICE compact model of metal oxide resistive switching memory with variations. IEEE Electron Device Letters, 33(10), 1405–1407.

Mazreah, A., et al. (2008). A low power SRAM base on novel word-line decoding. World Academy of Science, 2, 149–153.

Bazzi, H., et al. (2018). Design of hybrid CMOS Non-volatile SRAM cells in 130 nm RRAM technology. In 2018 30th international conference on microelectronics (ICM), Sousse, Tunisia (pp. 228–231).

Majumdar, S., et al. (2017). Programming scheme-based optimization of hybrid 4T-2R OxRAM NVSRAM. Semiconductor Science and Technology, 32, 094008.

Wei, W., et al. (2014). Design of a nonvolatile 7T1R SRAM cell for instant-on operation. IEEE Transactions on Nanotechnology, 13(5), 905–916.

Mounica, J., et al. (2016). Design of a nonvolatile 8T1R SRAM Cell for instant-on operation. International Journal of Electrical and Computer Engineering (IJECE), 6(3), 1183–1189.

Birla, S., et al. (2011). Static noise margin analysis of various SRAM topologies. International Journal of Engineering and Technology, 3(3), 304–309.

Pavlov, A., et al. (2008). CMOS SRAM circuit design and parametric test in nano-scaled technologies. Intel Corporation, University of Waterloo (pp. 1–202).

Gurjar, A., et al. (2011). An analytical approach to design VLSI implementation of low power, high speed SRAM cell using sub-micron technology. International Journal of VLSI Design and Communication Systems (VLSICS), 2(4), 143–153.

Le, B. S. et al. (2014). SRAM cell for high noise margin and soft errors tolerance in nanoscale technology. In 2014 international conference on computing, management and telecommunications (ComManTel). https://doi.org/10.1109/commantel.2014.6825586.

Guin, U., et al. (2019). Detecting recycled SoCs by exploiting aging induced biases in memory cells. In IEEE international symposium on hardware oriented security and trust.

Ishibashi, K., & Osada, K. (2011). Low power and reliable SRAM memory cell and array design. Berlin: Springer.

Shin, C., et al. (2012). Advanced MOSFET designs and implications for SRAM scaling. In Electrical engineering and computer sciences University of California at Berkeley (pp. 1–3). Technical Report Number: UCB/EECS-2012-50.

Acknowledgements

I would like to acknowledge the support of the Lebanese International University and Aix-Marseille University, along with the support of Campus France (Eiffel scholarship).

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Bazzi, H., Harb, A., Aziza, H. et al. RRAM-based non-volatile SRAM cell architectures for ultra-low-power applications. Analog Integr Circ Sig Process 106, 351–361 (2021). https://doi.org/10.1007/s10470-020-01587-z

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-020-01587-z