Abstract

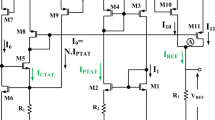

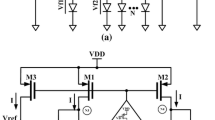

This paper presents a resistor-less high-precision, sub-1 V all-CMOS voltage reference. A curvature-compensation method is used to cancel the logarithmic temperature dependence regardless of mobility temperature exponent \((\upgamma)\). The circuit is simulated in 65 nm CMOS technology and yields an output voltage of 594 mV, temperature coefficient of \(7\frac{\text{ppm}}{{^{ \circ } {\text{C}}}}\) in the range of −40 to 125 °C, a power supply rejection ratio (PSRR) of − 43 dB at of 100 Hz, a line sensitivity of \(\frac{{76\,\upmu{\text{V}}}}{\text{V}}\) in the supply voltage range of 1.2 to 2 V, a power dissipation of \(1.4\,\upmu{\text{W}}\) at 1.2 V supply and an output noise of \(2.8\frac{{\upmu{\text{V}}}}{{\sqrt {\text{Hz}} }}\) at \(100\,{\text{Hz}}\). The total active area of the design is \(0.03\,{\text{mm}}^{2}\). This voltage reference is suitable for low-power, low-voltage applications which also require high precision.

Similar content being viewed by others

References

Rincon-Mora, G. A. (2002). Voltage reference-from diodes to precision high-order bandgap circuits. New York: Wiley.

Banba, H., Shiga, H., Umezawa, A., Miyaba, T., Tanzawa, T., Atsumi, S., et al. (1999). A CMOS bandgapreferencecircuitwithsub-1-Voperation. IEEE Journal of Solid-State Circuits 3, 4(5), 670–674.

Widlar, R. J. (1971). New developments in IC voltage regulators. IEEE Journal of Solid-State Circuits, SSC-6(1), 2–7.

Rich, A. (2005). Voltage reference application and design note. Retrieved June 23, 2005 from http://www.Allelectronics.de/ai/resources/1cfd65da928.pdf.

Neuteboom, H., Kup, B. M. J., & Janssens, M. (1997). A DSP-based hearing instrument IC. IEEE Journal of Solid-State Circuits, 32(11), 1790–1806.

Brokaw, A. P. (1974). A simple three-terminal IC bandgap reference. IEEE Journal of Solid-State Circuits, SSC-9(6), 388–393.

Leung, K. N., & Mok, P. K. T. (2002). A sub-1-V 15 ppm/C CMOS bandgap voltage reference without requiring low threshold voltage device. IEEE Journal of Solid-State Circuits, 37(4), 526–530.

Doyle, J., Lee, Y. J., Kim, Y.-B., Wilsch, H., & Lombardi, F. (2004). A CMOS subbandgap reference circuit with 1-V power supply voltage. IEEE Journal of Solid-State Circuits, 39(1), 252–255.

Leung, K. N., Mok, P. K. T., & Leung, C. Y. (2003). A 2-V 23u A 5.3-ppm/C curvature-compensated CMOS bandgap voltage reference. IEEE Journal of Solid-State Circuits, 38, 561–564.

Rincon-Mora, G. A., & Allen, P. E. (1998). A 1.1-V current-mode and piecewise-linear curvature-corrected bandgap reference. IEEE Journal of Solid-State Circuits, 33(10), 1551–1554.

Li, J.-H., Zhang, X., & Yu, M. (2011). A 1.2-V piecewise curvature-corrected bandgap reference in 0.5 mCMOS process. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 19(6), 1118–1122.

Popa, C. (2009). Logarithmic compensated voltage reference. In Proceedings of the 2009 Spanish conference on electron devices (pp. 215–218). Santiago de Compostela, Spain, February 11–13, 2009.

Duan, Q., & Roh, J. (2014). A 1.2-V 4.2-ppm C high-order curvature-compensated CMOS bandgap reference. IEEE Transactions on Circuits and Systems—I, 62(3), 662–670.

Lee, K., Sverre Lande, T., & Hafliger, P. (2015). A sub-bandgap reference circuit with an inherent curvature-compensation property. IEEE Transactions on Circuits and Systems—I, 62(1), 1–9.

Siqueira Dias, J. A., do Amaral, W. A., & de Moraes, W. B. (2009). A curvature-compensated CMOS voltage reference using V2th characteristics. Microelectronics Journal, 40, 1772–1778.

Rossi, C., Galup-Montoro, C., & Schneider, M. C. (2007). PTAT voltage generator based on an MOS voltage divider. In Proceedings of the IEEE NSIT (pp. 625–628).

Tam, W Sh, Wong, O. Y., Kok, C. W., & Wong, H. (2010). Generating sub/1 V reference voltages from a resistorless CMOS bandgap reference ciecuit by using a piecewise curvature temperature compensation technique. Microelectronics Reliability Journal, 50, 1054–1061.

Zeng, Y., Huang, Y., Luo, Y., & Tan, H. Z. (2013). An ultra-low-power CMOS voltage reference generator based on body bias technique. Microelectronics Journal, 44, 1145–1153.

Chouhan, Sh S, & Halonen, K. (2015). Design and implementation of a micro-power CMOS voltage reference circuit based on thermal compensation of V gs. Microelectronics Journal, 46, 36–42.

Luo, H., Han, Y., Cheung, R. C. C., Liang, G., & Zhu, D. (2012). Subthreshold CMOS voltage reference circuit with body bias compensation for process variation. IET Circuits, Devices & Systems, 6(3), 198–203.

Osaki, Y., Hirose, T., Kuroki, N., & Numa, M. (2013). 1.2-V Supply, 100nW, 1.09-V Bandgap and 0.7-V Supply, 52.2-nW, 0.55-V Subbandgap Reference Circuits for Nanowatt CMOS LSIs. IEEE Journal of Solid-State Circuits, 48(6), 1530–1538.

Ker, M. D., & Chen, J. S. (2006). New curvature compensated technique for CMOS bandgap reference with sub-1-V operation. IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, 53(8), 667–671.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Ghanavati Nejad, T., Farshidi, E., Sjöland, H. et al. A high precision logarithmic-curvature compensated all CMOS voltage reference. Analog Integr Circ Sig Process 99, 383–392 (2019). https://doi.org/10.1007/s10470-018-1296-0

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-018-1296-0