Abstract

The performance requirement of an operational trans-conductance amplifier (OTA) for the high gain and low power neural recording frontend has been addressed in this paper. A novel split differential pair technique is proposed to improve the gain of the OTA without any additional bias current requirements. The design demonstrates a significant performance enhancement when compared to existing techniques, such as gain-boosting and recycling. A qualitative and quantitative treatment is presented to explore the impact of the split ratio on the performance parameters of gain, bandwidth, and linearity. A prototype implemented in TSMC 65 nm CMOS technology achieved 68 dB open loop-gain (13 dB higher than the conventional circuit) and a 17 kHz 3-dB bandwidth. A linearity of − 62 dB has been achieved with 7 mV pk–pk signal at the input. The circuit operates from a 1 V supply and draws 0.6 uA static current. The prototype occupies 3300 um2 silicon area.

Similar content being viewed by others

References

Nicolelis, M. A. L. (2001). Actions from thoughts. Nature, 49, 403–407.

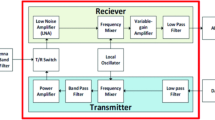

Neihart, N., & Harrison, R. (2005). Micropower circuits for bidirectional wireless telemetry in neural recording applications. IEEE Transactions on Biomedical Engineering, 52(11), 1950–1959.

Chae, M. S., Liu, W., & Sivaprakasham, M. (2008). Design optimization for integrated neural recording systems. IEEE Journal of Solid-State Circuits, 43(9), 1931–1939.

Jochum, T., Denison, T., & Wolf, P. (2009). Integrated circuit amplifiers for multi-electrode intracortical recording. Journal of Neural Engineering, 6, 012001.

Harrison, R.(2003). A low-power integrated circuit for adaptive detection of action potentials in noisy signals. In Proceedings of the IEEE lnternational Conference of the Engineering in Medicine and Biology Society, pp. 3325–3328.

Chaturvedi, V., & Amrutur, B. (2011). An area-efficient noise-adaptive neural amplifier in 130 nm CMOS technology. Journal on Emerging and Selected Topics in Circuits and System, 1(4), 536–545.

Lee, T. H. (1998). The design of CMOS radio-frequency integrated circuits. Cambridge: Cambridge University Press.

Wattanapanitch, W., & Sarpeshkar, R. (2011). A low-power 32-channel digitally programmable neural recording integrated circuit. IEEE Transactions on Biomedical Circuits and Systems, 5(6), 592–602.

Sackinger, E., & Guggenbuhl, W. (1990). A high-swing high-impedance MOS cascode circuit. IEEE Journal of Solid-State Circuits, 25(1), 289–298.

Bult, K., & Geelen, G. J. G. M. (1990). A fast-settling CMOS op amp for SC circuits with 90-dB DC gain. IEEE Journal of Solid-State Circuits, 25, 1379–1384.

Pernici, S., Nicollini, G., & Castello, R. (1993). A CMOS Low-distortion fully differential power amplifier with double nested miller compensation. IEEE Journal of Solid-State Circuits, 28, 758–763.

Assaad, R., & Silva-Martinez, J. (2009). The recycling folded cascode: A general enhancement of the folded cascade amplifier. IEEE Journal of Solid-State Circuits, 44(9), 2535–2542.

Yan, Z., Mak, P. I., & Martins, R. P. (2012). Double recycling technique for folded-cascode OTA. Analog integrated circuits and signal processing, 71, 137. https://doi.org/10.1007/s10470-011-9762-y.

Drennan, P. G., Kniffin, M. L., Locascio, D. R (2006) Implications of proximity effects for analog design. In Proceedings of the IEEE Custom Integrated Circuits Conference (CICC), pp. 169–176.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Nagulapalli, R., Hayatleh, K., Barker, S. et al. An OTA gain enhancement technique for low power biomedical applications. Analog Integr Circ Sig Process 95, 387–394 (2018). https://doi.org/10.1007/s10470-018-1148-y

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-018-1148-y