Abstract

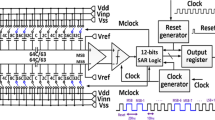

This paper presents a novel comparator being robust to temperature and process variations. The new comparator is confronted to a conventional topology used in most of the Successive Approximations Analog to Digital Converters (SAR ADCs) for biomedical applications. To verify the benefits of the new comparator, it was designed on a CMOS 65 nm process and characterized with post layout simulations under conditions of process and temperature fluctuations. With the proposed circuit, a SAR ADC exhibits 83.11 dB of Signal to Noise Ratio at 1.28 MS/s and \(375\,\upmu\hbox {W}\) of power consumption. The PT variations for critical corners are less than 0.58 bits.

Similar content being viewed by others

References

Xu, J., Büsze, B., Van Hoof, C., Makinwa, K. A. A., & Yazicioglu, R. F. (2015). A 15-channel digital active electrode system for multi-parameter biopotential measurement. IEEE Journal of Solid-State Circuits, 50(9), 2090–2100.

Shu, Y. S., Kuo, L. T., & Lo, T. Y. (2016). 27.2 an oversampling SAR ADC with DAC mismatch error shaping achieving 105dB SFDR and 101dB SNDR over 1 kHz BW in 55nm CMOS. In 2016 IEEE international solid-state circuits conference (ISSCC) (pp. 458–459).

Liang, Y., Zhu, Z., & Ding, R. (2015). A 10-bit 300-MS/s asynchronous SAR ADC with strategy of optimizing settling time for capacitive DAC in 65 nm CMOS. Microelectronics Journal, 46, 988–995.

Chang, H.-W., Huang, H.-Y., Juan, Y.-H., Wang, W.-S., & Luo, C.-H. (2013). Adaptive successive approximation ADC for biomedical acquisition system. Microelectronics Journal, 44, 729–735.

Fitzpatrick, D. (2015). Implantable electronic medical devices (1st ed.). Atlanta: Elsevier.

Ohnhaeuser, F. (2012). A 1.5mW IMSPS 16bit SAR ADC with high performance. In 2012 International on semiconductor conference Dresden–Grenoble (ISCDG) (pp. 9–12).

Chi, Y. (2013). 16-bit 1MS/s 44mW successive approximation register analog-to-digital converter achieving signal-to-noise-and-distortion-ratio of 94.3dB. In 2013 IEEE international conference electron devices and solid-state circuits (EDSSC) (pp. 1–2).

Chen, M. (2013) A low-power Auto-zeroed Comparator for Column paralleled 14b SAR ADCs of 384x288 lRFPA ROlC. In IEEE international conference on electron devices and solid-state circuits (EDSSC) (pp. 1–2).

Figueiredo, P. M., & Vital, J. C. (2009). Offset reduction teqchniques in higspeed analog to digital converters. Berlin: Springer.

Gregorian, R. (1999). Introduction to CMOS OPAMPs and comparators. New York: Wiley.

Goll, B. (2009). A comparator with reduced delay time in 65-nm CMOS for supply voltages down to 0.65 V. IEEE Transactions on Circuits and Systems II: Express Briefs, 56(11), 810–814.

Miki, T. (2015). A 4.2 mW 50 MS/s 13 bit CMOS SAR ADC with SNR and SFDR enhancement techniques. IEEE Journal of Solid-State Circuits, 50(6), 1372–1381.

Osipov, D. (2012). Behavioral model of split capacitor array DAC for use in SAR ADC design. In 8th Conference research in microelectronics and electronics (PRIME) (pp. 127–130).

Rehman, SU (2015) Reference-less SAR ADC for on-chip thermal monitoring in CMOS. In IEEE international symposium on circuits and systems (ISCAS) (pp. 2441–2444).

Aksin, D., Al-Shyoukh, M., & Maloberti, F. (2006). Switch bootstrapping for precise sampling beyond supply voltage. IEEE Journal of Solid-State Circuits, 41(8), 1938–1943.

Acknowledgements

The authors give special thanks to CONACyT Mexico for the financial support of the Project Infra 2013 \(\# 205873\).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

de La Fuente-Cortes, G., Espinosa Flores-Verdad, G., Gonzalez-Diaz, V.R. et al. A new CMOS comparator robust to process and temperature variations for SAR ADC converters. Analog Integr Circ Sig Process 90, 301–308 (2017). https://doi.org/10.1007/s10470-016-0916-9

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-016-0916-9