Abstract

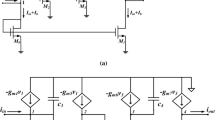

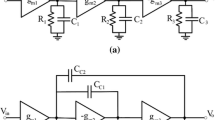

This paper presents a new and compact two stage CMOS structure with enhanced gain-bandwidth product (GBW) and high slew rate. The frequency compensation technique employed here comprises of a negative capacitance cell and a flipped voltage follower (FVF). The use of negative capacitance lowers the parasitic capacitance of preceding stage and thereby achieves significant improvement in GBW. The FVF acts as a voltage buffer and exploits pole-zero cancellation technique. The required compensation capacitor is very small so it can save chip area. The workability of the proposed circuit has been verified by using Mentor Graphics Eldo simulation tool with TSMC CMOS 0.18 µm process parameters. The simulated results show a GBW of 1.2 GHz and average slew rate of 88 V/µs with a power consumption of 6.3 mW.

Similar content being viewed by others

References

Comer, D. J., et al. (2006). Bandwidth extension of high-gain CMOS stages using active negative capacitance. 13th IEEE international conference on electronics, circuits and systems, 2006, ICECS’06. IEEE.

Ghadiri, A., & Moez, K. (2010). Gain-enhanced distributed amplifier using negative capacitance. IEEE Transactions on Circuits and Systems I: Regular Papers, 57(11), 2834–2843.

Kolev, S., Delacressonniere, B., & Gautier, J.-L. (2001). Using a negative capacitance to increase the tuning range of a varactor diode in MMIC technology. IEEE Transactions on Microwave Theory and Techniques, 49(12), 2425–2430.

Shoji, M., & Rolfe, R. M. (1985). Negative capacitance bus terminator for improving the switching speed of a microcomputer databus. IEEE Journal of Solid-State Circuits, 20(4), 828–832.

Tsividis, Y. P., & Gray, P. R. (1976). An integrated NMOS operational amplifier with internal compensation. IEEE Journal of Solid-State Circuits, 11(6), 748–753.

Smarandoiu, G., et al. (1978). CMOS pulse-code-modulation voice codec. IEEE Journal of Solid-State Circuits, 13(4), 504–510.

Ramirez-Angulo, J., et al. (2002). The flipped voltage follower: A useful cell for low-voltage low-power circuit design. IEEE international symposium on circuits and systems, 2002, ISCAS 2002 (Vol. 3). IEEE.

Peng, X., & Sansen, W. (2005). Transconductance with capacitances feedback compensation for multistage amplifiers. IEEE Journal of Solid-State Circuits, 40(7), 1514–1520.

Ho, K.-P., et al. (2003). Reversed nested Miller compensation with voltage buffer and nulling resistor. IEEE Journal of Solid-State Circuits, 38(10), 1735–1738.

Assaad, R. S., & Silva-Martinez, J. (2009). The recycling folded cascode: A general enhancement of the folded cascode amplifier. IEEE Journal of Solid-State Circuits, 44(9), 2535–2542.

Tan, M. T., et al. (2010). AC-boosting frequency compensation with double pole-zero cancellation for multistage amplifiers. Circuits, Systems and Signal Processing, 29(5), 941–951.

Mesri, A., et al. (2015). High gain two-stage amplifier with positive capacitive feedback compensation. Circuits, Devices Systems, 9(3), 181–190.

Biabanifard, S., et al. (2015). High performance reversed nested Miller frequency compensation. Analog Integrated Circuits and Signal Processing, 85(1), 223–233.

Mirvakili, A., & Koomson, V. J. (2014). Passive frequency compensation for high gain-bandwidth and high slew-rate two-stage OTA. Electronics Letters, 50(9), 657–659.

Perez, A. P., et al. (2009). Slew-rate and gain enhancement in two stage operational amplifiers. IEEE international symposium on circuits and systems, 2009, ISCAS 2009. IEEE.

Cannizzaro, S. O., et al. (2008). Single Miller capacitor frequency compensation with nulling resistor for three-stage amplifiers. International Journal of Circuit Theory and Applications, 36(7), 825–837.

Singh, U., & Gupta, M. (2013). High frequency flipped voltage follower with improved performance and its application. Microelectronics, 44(12), 1175–1192.

Singh, U., Gupta, M., & Srivastava, R. (2015). A new wideband regulated cascode amplifier with improved performance and its application. Microelectronics, 46, 758–776.

Gupta, M., & Singh, U. (2012). A new flipped voltage follower with enhanced bandwidth and low output impedance. Analog Integrated Circuits and Signal Processing, 72(1), 279–288.

Aminzadeh, H., Danaie, M., & Serdijn, W. A. (2013). Hybrid cascode feedforward compensation for nano-scale low-power ultra-area-efficient three-stage amplifiers. Microelectronics Journal, 44(12), 1201–1207.

Ahmadi, M. M. (2006). A new modeling and optimization of gain-boosted cascode amplifier for high-speed and low-voltage applications. IEEE Transactions on Circuits and Systems II: Express Briefs, 53(3), 169–173.

Pakala, S. H., et al. (2015). Voltage buffer compensation using flipped voltage follower in a two-stage CMOS op-amp. IEEE 58th international midwest symposium on circuits and systems (MWSCAS). IEEE.

Di Cataldo, G., et al. (2016). Improved single-Miller passive compensation network for three-stage CMOS OTAs. Analog Integrated Circuits and Signal Processing, 86(3), 417–427.

Tan, M., & Ki, W.-H. (2015). A cascode Miller-compensated three-stage amplifier with local impedance attenuation for optimized complex-pole control. IEEE Journal of Solid-State Circuits, 50(2), 440–449.

Mak, K. H., & Leung, K. N. (2014). A signal-and transient-current boosting amplifier for large capacitive load applications. IEEE Transactions on Circuits and Systems I: Regular Papers, 61(10), 2777–2785.

Yan, Z., et al. (2015). Nested-current-mirror rail-to-rail-output single-stage amplifier with enhancements of DC gain, GBW and slew rate. IEEE Journal of Solid-State Circuits, 50(10), 2353–2366.

Grasso, A. D., Palumbo, G., & Pennisi, S. (2008). Comparison of the frequency compensation techniques for CMOS two-stage Miller OTAs. IEEE Transactions on Circuits and Systems II: Express Briefs, 55(11), 1099–1103.

Grasso, A. D., Palumbo, G., & Pennisi, S. (2015). High-performance four-stage CMOS OTA suitable for large capacitive loads. IEEE Transactions on Circuits and Systems I: Regular Papers, 62(10), 2476–2484.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that there is no conflict of interests regarding the publication of this paper.

Rights and permissions

About this article

Cite this article

Bansal, U., Gupta, M. & Singh, U. Frequency compensation of two stage CMOS circuit using negative capacitance and flipped voltage follower. Analog Integr Circ Sig Process 90, 175–188 (2017). https://doi.org/10.1007/s10470-016-0857-3

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-016-0857-3