Abstract

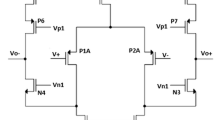

This paper describes a gain enhancement method and also a slew-rate enhancement scheme for folded-cascode amplifiers which uses positive feedback + transconductance increaser method for the sake of gain increment that gives rise to approximately 21 db of increment in the amount of the gain. An approach for increasing the slew-rate has also been employed which has increased the slew-rate of the amplifier approximately 5 times the conventional folded-cascode one as well as the triple folded-cascode one. Also the settling time and consequently the speed of the circuit is improved remarkably i.e. over 6 times the conventional folded-cascode and triple folded cascode ones. The amplifier has been designed in TSMC RF 0.18 μm and consumes 920 µw of power meanwhile provides 67 db for gain, 581 MHz for UGBW, 69° for phase margin, 793 V/µS for slew-rate and 3.2 nS for large-signal settling time as well as the gain-error of the amplifier for large-signal is approximately 0.5 %. The layout of the circuit has also been carried out in Cadence and demonstrates that the op amp occupies 41 µm × 61 µm (0.002 \(\text{mil}^{2}\)) of the die area. The post-layout-simulation of the op amp was also fulfilled and the results are displayed.

Similar content being viewed by others

References

Razavi, B. (2001). Design of analog CMOS integrated circuits. New York: McGraw-Hill.

Gray, P. R., Hurst, P. J., Lewis, S. H., & Meyer, R. G. (2009). Analysis and design of analog integrated circuits (Vol. 5). New York: Wiley.

Carusone, T. C., Johns, D. A., & Martin, K. W. (2011). Analog integrated circuit design (Vol. 2). New York: Wiley.

Baker, R. J. (2010). CMOS circuit design, layout, and simulation (Vol. 3). New York: Wiley.

Assaad, R. S., & Martinez, J. S. (2009). The recycling folded cascode: A general enhancement of the folded cascode amplifier. IEEE Journal of Solid State Circuits, 44(9), 2535–2542.

Bult, K., & Geelen, G. J. G. M. (1990). A fast-settling CMOS op amp for SC circuits with 90-dB DC gain. IEEE Journal of Solid State Circuits, 25(6), 1379–1384.

Degrauwe, M. G., Rijmenants, J., Vittoz, E. A., & Deman, H. J. (1982). Adaptive biasing CMOS amplifiers. IEEE Journal of Solid State Circuits, 17(3), 522–552.

Sakurai, S., Zarabadi, S.R., & Ismail, M. (1990). Folded-cascode operational amplifier with slew enhancement circuit. Proceedings of IEEE International Symposium on Circuits and Systems, New Orleans, May 1990, pp. 3205–3208

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Pourabdollah, M. A new gain-enhanced and slew-rate-enhanced folded-cascode op amp. Analog Integr Circ Sig Process 88, 43–56 (2016). https://doi.org/10.1007/s10470-016-0739-8

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-016-0739-8