Abstract

An adaptive voltage scaling (AVS) DC–DC converter based on embedded pulse skip modulation (PSM) is presented in this paper. As AVS technique developing, the supply voltage of digital circuits can be scaled adaptively with the changing of operation frequency and working environment. The critical path replica (CPR) is widely used in AVS implementation. The worst-case margin is relaxed by probing and tracking the CPR delay time of target applications. Consequently, the energy consumption of digital circuits is decreased significantly with supply voltage reduced. At the same time, in order to improve the efficiency of DC–DC converter especially in light load, the PSM mode has been used in proposed circuit structure. The circuit of AVS DC–DC converter based on embedded PSM has been implemented and fabricated in a standard 0.13 μm CMOS process which occupies 1.2 mm2 active silicon areas. The experimental results show that, the output voltage of the DC–DC converter is well regulated from 0.6 to 1.5 V when the clock frequency varies within the range of 30–150 MHz. The maximum energy saving of 83 % is obtained with the proposed circuit structure compared to the traditional fixed voltage.

Similar content being viewed by others

References

Calhoun, B. H., Wang, A., & Chandrakasan, A. (2005). Model and sizing for minimum energy operation in subthreshold circuits. IEEE Journal of Solid-State Circuits, 40(9), 1778–1786.

Chatterjee, A., Nandakumar, M., & Chen, I. (1996). An investigation of the impact of technology scaling on power wasted as short-circuit current in low voltage static CMOS circuits. IEEE Low Power Electronics and Design, (pp. 145–150).

Dancy, A., Amirtharajah, R., & Chandrakasan, A. (2000). High-efficiency multiple-output DC–DC conversion for low-voltage systems. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 8(3), 252–263.

Elgebaly, M., & Sachdev, M. (2007). Variation-aware adaptive voltage scaling systems. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 15(5), 560–571.

Gelsinger, P. (2004). Gigascale integration for teraops performance: challenges, opportunities, and new frontiers. IEEE Design Automation Conference.

Gu-Yeon, W., & Horowitz, M. (1999). A fully digital, energy-efficient, adaptive power supply regulator. IEEE Journal of Solid-State Circuits, 34(4), 520–528.

Hangbiao, L., Bo, Z., Ping, L., et al. (2014). Adaptive duty ratio modulation technique in switching DC–DC converter operating in discontinuous conduction mode. Analog Integrated Circuits and Signal Processing, 78(2), 361–371.

Ikenaga, Y., Nomura, M., Suenaga, S., et al. (2012). A 27 % active-power-reduced 40-nm CMOS multimedia SoC with adaptive voltage scaling using distributed universal delay lines. IEEE Journal of Solid-State Circuits, 47(4), 832–840.

Kuroda, T., Suzuki, K., Mita, S., et al. (1998). Variable supply-voltage scheme for low-power high-speed CMOS digital design. IEEE Journal of Solid-State Circuits, 33(3), 454–462.

Ping, L., Luyang, L., Zhaoji, L., et al. (2002). Skip cycle modulation in switching DC–DC converter. IEEE International Conference on Communications, Circuits and Systems and West Sino Expositions, (Vol. 2, pp. 1716–1719).

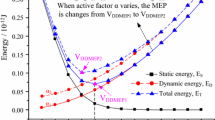

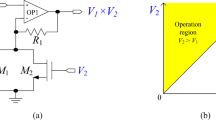

Ping, L., Xiang, G., Ye, Z., et al. (2012). Minimum energy point tracking circuit based on PSM for digital loads. IEEE 11th International Conference on Solid-State and Integrated Circuit Technology (ICSICT), (pp. 1–3).

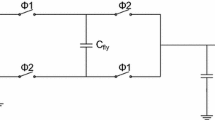

Ping, L., Zhaoji, L., & Bo, Z. (2006). A novel improved PSM model in DCDC converter based on energy balance. IEEE Power Electronics Specialists Conference, (pp. 1–4).

Ramadass, Y. K., & Chandrakasan, A. (2008). Minimum energy tracking loop with embedded DC–DC converter enabling ultra-low-voltage operation down to 250 mV in 65 nm CMOS. IEEE Journal of Solid-State Circuits, 43(1), 256–265.

Sakurai, T. (2003). Perspectives on power-aware electronics. IEEE International of Solid-State Circuits Conference (ISSCC), 1, 26–29.

Shaowei, Z., Ping, L., & Bo, Z. (2014). Design of highly integrated power management unit with dual DVS-enabled regulators. Analog Integrated Circuits and Signal Processing, 80, 209–220.

Sinha, A., & Chandrakasan, A. (2001). Dynamic power management in wireless sensor networks. IEEE Design and Test of Computers, 18(2), 62–74.

Stratakos, A., Sanders, S., & Broderson, R. (1994). A low- voltage CMOS DC-DC converter for a portable battery- operated system. IEEE Power Electron Specialists Conference, (pp. 619–626).

Wang, A., & Chandrakasan, A. (2005). A 180-mV subthreshold FFT processor using a minimum energy design methodology. IEEE Journal of Solid-State Circuits, 40(1), 310–319.

Wirnshofer, M., Heiss, L., Georgakos, G., et al. (2011). A variation-aware adaptive voltage scaling technique based on in-siut delay monitoring. IEEE 14th International Symposium on Design and Diagnostics of Electronic Circuits & Systems (DDECS), (pp. 261–266).

Acknowledgments

This work was supported in part by the National Natural Science Foundation of China under Grant 61274027 and Doctoral Program Foundation of Institutions of Higher Education of China under Grant 20120185110005.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Wang, D., Luo, P., Zhen, S. et al. An adaptive voltage scaling DC–DC converter based on embedded pulse skip modulation. Analog Integr Circ Sig Process 84, 445–453 (2015). https://doi.org/10.1007/s10470-015-0603-2

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-015-0603-2