Abstract

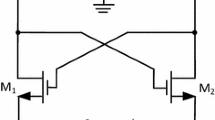

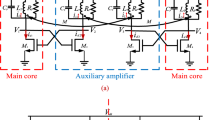

According to the discussion of noise sources and up-conversion mechanisms of flicker noise, an LC oscillator with improved self-switched biasing and decoupling capacitor is presented. To minimize the 1/f 3 phase noise, both source noise and conversion gain of flicker noise are desirable to reduce, rather than only one way in previous works. Flicker noise from tail-biasing transistors is reduced by self-switched biasing technology, and the up-conversion of flicker noise from cross-coupled pair is suppressed by decoupling capacitor at the same time. Phase noise and key parameters influencing phase noise are analyzed in detail. To guide the design, simple way to get optimum values of key parameters is also presented. This oscillator can work at low supply voltage to reduce power consumption considerably compared to conventional self-switched biasing. The proposed oscillator is fabricated in 0.18 μm CMOS process, and exhibits a low phase noise of −77.5 dBc/Hz (FoM = 181) and −122.8 dBc/Hz (FoM = 186) at 10 kHz and 1 MHz offset, respectively, from oscillation frequency of 2.55 GHz while dissipating 2.7 mA with 1.2 V supply voltage.

Similar content being viewed by others

References

Levantino, S., Samori, C., Bonfanti, A., Gierkink, S. L., Lacaita, A. L., & Boccuzzi, V. (2002). Frequency dependence on bias current in 5 GHz CMOS VCOs: Impact on tuning range and flicker noise upconversion. IEEE Journal of Solid-State Circuits, 37(8), 1003–1011.

Hegazi, E., Sjoland, H., & Abidi, A. A. (2001). A filtering technique to lower LC oscillator phase noise. IEEE Journal of Solid-State Circuits, 36(12), 1921–1930.

Boon, C. C., Do, M. A., Yeo, K. S., Ma, J., & Zhang, X. L. (2004). RF CMOS low-phase-noise LC oscillator through memory reduction tail transistor. IEEE Transactions on Circuits and Systems II: Express Briefs, 51(2), 85–90.

Huang, G., & Kim, B.-S. (2009). Low phase noise self-switched biasing CMOS LC quadrature VCO. IEEE Transactions on Microwave Theory and Techniques, 57(2), 344–351.

Bloom, I., & Nemirovsky, Y. (1991). 1/f noise reduction of metal-oxide-semiconductor transistors by cycling from inversion to accumulation. Applied Physics Letters, 58(15), 1664–1666.

Klumperink, E. A., Gierkink, S. L., van der Wel, A. P., & Nauta, B. (2000). Reducing MOSFET 1/f noise and power consumption by switched biasing. IEEE Journal of Solid-State Circuits, 35(7), 994–1001.

Demir, A. (2006). Computing timing jitter from phase noise spectra for oscillators and phase-locked loops with white and 1/f3 noise. IEEE Transactions on Circuits and Systems I: Regular Papers, 53(9), 1869–1884.

Groszkowski, J. (1933). The interdependence of frequency variation and harmonic content, and the problem of constant-frequency oscillators. Proceedings of the Institute of Radio Engineers, 21(7), 958–981.

Bevilacqua, A., & Andreani, P. (2012). An analysis of 1/f noise to phase noise conversion in CMOS harmonic oscillators. IEEE Transactions on Circuits and Systems I: Regular Papers, 59(5), 938–945.

Levantino, S., Samori, C., Zanchi, A., & Lacaita, A. L. (2002). AM-to-PM conversion in varactor-tuned oscillators. IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, 49(7), 509–513.

Hegazi, E., & Abidi, A. A. (2003). Varactor characteristics, oscillator tuning curves, and AM-FM conversion. IEEE Journal of Solid-State Circuits, 38(6), 1033–1039.

Hegazi, E., Rael, J., & Abidi, A. (2004). The designer’s guide to high-purity oscillators. Berlin: Springer.

Ismail, A., & Abidi, A. (2003). A CMOS differential LC oscillator with suppressed up-converted flicker noise. In Proceedings of IEEE international solid-state circuits conference (pp. 98–99). San Francisco.

Jerng, A., & Sodini, C. G. (2005). The impact of device type and sizing on phase noise mechanisms. IEEE Journal of Solid-State Circuits, 40(2), 360–369.

Pepe, F., Bonfanti, A., Levantino, S., Samori, C., & Lacaita, A. L. (2013). Analysis and minimization of flicker noise up-conversion in voltage-biased oscillators. IEEE Transactions on Microwave Theory and Techniques, 61(6), 2382–2394.

Chen, N., Huang, L., Wang, C., Yan, Y., & Lin, F. (2011). Low phase noise and linear gain VCO using self-switched biasing. In Proceedings of IEEE international symposium on radio-frequency integration technology (pp. 137–140).

Mira, J., Divel, T., Ramet, S., Begueret, J.-B., & Deval, Y. (2004). Distributed MOS varactor biasing for VCO gain equalization in 0.13 μm CMOS technology. In Digest of IEEE radio frequency integrated circuits symposium (pp. 131–134).

Jung, J., Upadyaya, P., Liu, P., & Heo, D. (2011). Compact sub-1 mW low phase noise CMOS LC-VCO based on power reduction technique. In Digest of IEEE MTT-S international microwave symposium (pp. 1–4).

Tong, H., Cheng, S., Lo, Y.-C., Karsilayan, A., & Silva-Martinez, J. (2012). An LC quadrature VCO using capacitive source degeneration coupling to eliminate bi-modal oscillation. IEEE Transactions on Circuits and Systems I: Regular Papers, 59(9), 1871–1879.

Yang, X., Uchida, Y., Xu, K., Wang, W., & Yoshimasu, T. (2014). A 0.3-V power supply 2.4-GHz-band class-C VCO IC with amplitude feedback loop in 65-nm CMOS. Analog Integrated Circuits and Signal Processing, 81(3), 583–591.

Acknowledgments

This work was supported by the National Science and Technology Major Project, China (No. 2008ZX03006 009), and partially supported by the USTC and IMECAS jointed lab Micro-/Nano-electronic System Integration R&D Center (MESIC) under Grant MESIC No. 2100230011. The authors would like to thank Prof. Chun-Hua Heng of National University of Singapore for helpful technical discussions.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Chen, N., Diao, S., Huang, L. et al. Reduction of 1/f 3 phase noise in LC oscillator with improved self-switched biasing. Analog Integr Circ Sig Process 84, 19–27 (2015). https://doi.org/10.1007/s10470-015-0560-9

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-015-0560-9