Abstract

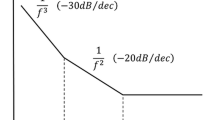

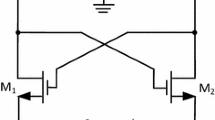

A way of analytical calculation in the phase noise modeling of the LC-VCO topology without tail current resource is proposed. The noise current imported by the MOS channel is modeled to give approximate evaluation, and the period of the transistor noise is included in the model. Phase noise introduced by the tank loss resistance is also modeled to evaluate the circuit phase noise performance. The circuit has been implemented in a 65 nm CMOS technology. The chip occupies 951 × 705 um2 areas with the buffer and pads. The test result indicates that the VCO core consumes 1.125 mW with a 1.2 V power supply, the frequency of the VCO baseband is from 1.258 to 1.37 GHz, and the multiband frequency is from 0.86 to 1.37 GHz. The best performance of the LC-VCO shows a phase noise of −129.57 dBc/Hz at 1 MHz offset frequency from a 1.3 GHz carrier, resulting in an excellent FoM of −191.27 dBc/Hz.

Similar content being viewed by others

References

Hajimiri, A., & Lee, T. H. (1998). A general theory of phase noise in electrical oscillators. IEEE Journal of Solid-State Circuits, 33(2), 179–194.

Hajimiri, A., & Lee, T. H. (1999). Design issues in CMOS differential LC Oscillators. IEEE Journal of Solid-State Circuits, 34(5), 717–724.

Hajimiri, A., & Lee, T. H. (2000). Oscillate phase noise: A tutorial. IEEE Journal of Solid-State Circuits, 35(3), 326–336.

Abidi, A. A. (1986). High-frequency noise measurements on FET’s with small dimensions. IEEE Transactions on Electron Devices, 33(11), 1801–1805.

Fiorelli, et al. (2011). LC-VCO Design Optimization Methodology Based on the gm/ID Ratio for Nanometer CMOS Technologies. IEEE Transactions on Microwave Theory and Techniques, 59(7), 1822–1831.

Andreani, P., et al. (2005). A study of phase noise in Colpitts and LC-tank CMOS oscillators. IEEE Journal of Solid-State Circuits, 40(5), 1107–1118.

Andreani, P., & Fard, A. (2006). More on the phase noise performance of CMOS differential-pair LC-tank oscillators. IEEE Journal of Solid-State Circuits, 41(12), 2703–2712.

Xuefeng, G., & Zhigong, W. (2008). Wideband CMOS VCO design and phase noise analysis. Journal of Southeast University (English Edition), 24(4), 433–436.

Zhou, M. (2012). A low phase noise wideband VCO in 65 nm RF CMOS for low power applications. International Conference on Microwave and Millimeter Wave Technology, 405–408.

Tsividis, Y. (2000). Operation and Modeling of the MOS Transistor (2nd ed., pp. 410–426). Oxford: Oxford University Press.

Andreani, P., et al. (2011). A TX VCO for WCDMA/EDGE in 90 nm RF CMOS. IEEE Journal of Solid-State Circuits, 46(7), 1618–1626.

Li, G., et al. (2012). A low-phase-noise wide-tuning-range oscillator based on resonant mode switching. IEEE Journal of Solid-State Circuits., 47(6), 1295–1308.

Tapio, A., et al. (2012). A Darlington-enhanced CMOS oscillator architecture. IEEE Transactions on Circuits and Systems II: Express Briefs, 59(1), 11–15.

Zhao, B., Lian, Y., Lian, Y., & Yang, H. (2013). A Low-Power Fast-Settling Bond-Wire Frequency Synthesizer with a Dynamic-Bandwidth Scheme. IEEE Transactions on Circuits and Systems-I: Regular Papers, 60((5), 1188–1199.

Acknowledgements

This work was supported in part by the National Science Foundation of China under Grant No. 61102027, the Major State Basic Research Development Program of China (973 Program) under Grant 2010CB327403, and the Zhejiang Provincial Natural Science Foundation of China under Grant No. LY13F040005.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Zhou, M., Sun, L., Jun, L. et al. LC-VCO design optimization at 1/f 2 phase noise performance in 65 nm CMOS technology. Analog Integr Circ Sig Process 80, 499–506 (2014). https://doi.org/10.1007/s10470-014-0339-4

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-014-0339-4