Abstract

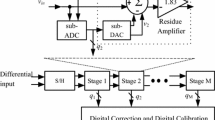

This paper presents the first aggressively calibrated 14-b 32 MS/s pipelined ADC. The design uses a comprehensive digital background calibration engine that compensates for linear and nonlinear errors as well as capacitor mismatch in multi-bit DAC. Background calibration techniques that estimate the errors by correlating the output of ADC with the calibration signal have a very slow convergence rate. This paper also presents a fully digital technique to speed up the convergence in the error estimation procedure. By digitally filtering the input signal during the error estimation, the convergence rate of the calibration has been improved significantly. Implemented in TSMC 0.25 μm technology, the pipelined ADC consumes 75 mA from 2.5 V and occupies 2.8 mm2 of active area. Measurement results show that calibration significantly improved dynamic (SNDR, SFDR) as well as static (DNL, INL) performance of the ADC.

Similar content being viewed by others

Notes

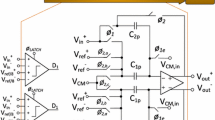

In this design, the multi-bit stages have two bits effective resolution with one full bit redundancy used for calibration. Therefore, eight comparators per stage are used although the gain of each stage is only four.

In this design, each stage has an effective resolution of two bits and one full bit redundancy is considered for calibration purposes.

References

Keane, J. P., Hurst, P. J., & Lewis, S. H. (2005). Background interstage gain calibration technique for pipelined ADCs. IEEE Transactions on Circuits and Systems I: Regular Papers, 52(1), 32–43.

Panigada, A., & Galton, I. (2006). Digital background correction of harmonic distortion in pipelined ADCs. IEEE Transactions on Circuits and Systems I: Regular Papers, 53(9), 1885–1895.

Meruva, A., & Jalali, B. (2007). Digital background calibration of higher order nonlinearities in pipelined ADCs. IEEE international symposium on circuits and systems (ISCAS), New Oreleans, LA, May 2007, pp. 1233–1236.

Keane, J. P., Hurst, P. J., & Lewis, S. H. (2006). Digital background calibration for memory effects in pipelined analog-to-digital converters. IEEE Transactions on Circuits and Systems I: Regular Papers, 53(3), 511–525.

Galton, I. (2000) Digital cancellation of D/A converter noise in pipelined A/D converters. IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, 47(3), 185–196.

Siragusa, E., & Galton, I. (2004) A digitally enhanced 1.8-V 15-bit 40-Msample/s CMOS pipelined ADC. IEEE Journal of Solid State Circuits, 39(12), 2126–2138.

Mehr, I., & Singer, L. (2000) A 55-mw, 10-bit, 40-Msample/s Nyquist-rate CMOS ADC. IEEE Journal of Solid State Circuits, 35(3), 318–325.

Murmann, B., & Boser, B. E. (2003). A 12 b 75 MS/s pipelined ADC using open-loop residue amplification. IEEE Journal of Solid State Circuits, 38(12), 2040–2050.

Acknowledgement

The authors thank Dana Price and Doug Garrity from Freescale, Tempe, AZ for useful suggestions and help with the testing and Connection One Center at ASU for supporting this project.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Jalali-Farahani, B., Meruva, A. A 14-b 32 MS/s pipelined ADC with fast convergence comprehensive background calibration. Analog Integr Circ Sig Process 61, 65–74 (2009). https://doi.org/10.1007/s10470-008-9278-2

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-008-9278-2