Abstract

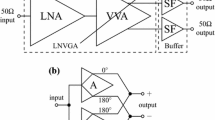

This paper describes a 2 GHz active variable gain low noise amplifier (VGLNA) in a 0.18-μm CMOS process. The VGLNA provides a 50-Ω input impedance and utilizes a tuned load to provide high selectivity. The VGLNA achieves a maximum small signal gain of 16.8 dB and a minimum gain of 4.6 dB with good input return loss. In the high gain and the low gain modes, the NFs are 0.83 dB and 2.8 dB, respectively. The VGLNA’s IIP3 in the high gain mode is 2.13 dBm. The LNA consumes approximately 4 mA of current from a 1.8-V power supply.

Similar content being viewed by others

References

Aoki, Y., Fujii, M., Ohkubo, S., Yoshida, S., Niwa, T., Miyoshi, Y., Dodo, H., Goto, N., & Hida, H. (2001). A 1.4-dB-NF variable-gain LNA with continuous control for 2-GHz-band mobile phones using InGaP emitter HBTs. In RFIC Symposium, Digest of Technological Papers, pp. 231−234.

Park, S., & Kim, W. (2001). Design of a 1.8 GHz low noise amplifier for RF front-end in a 0.8-μm. IEEE Transactions on Consumer Electronics, 47, 10–15.

Ray, B., Manku, T., Beards, R. D., Nisbet, J. J., & Kung, W. (1999). A highly linear bipolar 1V folded cascode 1.9 GHz low noise. In Bipolar/BiCMOS Circuits and Technology Meeting, 1999.

Leroux, P., Jassens, J., & Steyaert, M. (2002). A 0.8 dB NF ESD protected 9 mW CMOS LNA operating at 1.23 GHz. IEEE Journal of Solid-State Circuits, 37, 760–765.

Floyd, B. A., Meheta, J., Gamero, C., & Kenneth, K. O. (1999). A 900 MHz 0.8-μm CMOS low noise amplifier with 1.2 dB noise figure. In IEEE Custom Integrated Circuits Conference, Digest of Technological Papers, 661–664.

Lee, T. H. (2000). The design of cmos radio frequency integrated circuits. Cambridge, UK: Cambridge University Press.

Gonzalez, G. (1996). Microwave transistor amplifiers analysis and design. New Jersey: Prentice Hall.

Acknowledgments

The authors would like to thank Texas Instruments Inc. for their support in conducting this project. The authors also would like to thank Steve Bibyk and Patrick Roblin for their suggestion on this work. The authors also would like to thank the anonymous referees for their valuable comments in improving the contents of this paper.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Alam, S.K., DeGroat, J. A 2 GHz variable gain low noise amplifier in 0.18-μm CMOS . Analog Integr Circ Sig Process 56, 37–42 (2008). https://doi.org/10.1007/s10470-007-9080-6

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-007-9080-6