Abstract

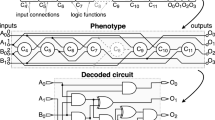

Scalability is a main and urgent problem in evolvable hardware (EHW) field. For the design of large circuits, an EHW method with a decomposition strategy is able to successfully find a solution, but requires a large complexity and evolution time. This study aims to optimize the decomposition on large-scale circuits so that it provides a solution for the EHW method to scalability and improves the efficiency. This paper proposes a projection-based decomposition (PD), together with Cartesian genetic programming (CGP) as an EHW system namely PD-CGP, to design relatively large circuits. PD gradually decomposes a Boolean function by adaptively projecting it onto the property of variables, which makes the complexity and number of sub-logic blocks minimized. CGP employs an evolutionary strategy to search for the simple and compact solutions of these sub-blocks. The benchmark circuits from the MCNC library, \(n\)-parity circuits, and arithmetic circuits are used in the experiment to prove the ability of PD-CGP in solving scalability and efficiency. The results illustrate that PD-CGP is superior to 3SD-ES in evolving large circuits in terms of complexity reduction. PD-CGP also outperforms GDD+GA in evolving relatively large arithmetic circuits. Additionally, PD-CGP successfully evolves larger \(n\)-even-parity and arithmetic circuits, which have not done by other approaches.

Similar content being viewed by others

References

Ali B, Almaini AEA, Kalganova T (2004) Evolutionary algorithms and their use in the design of sequential logic circuits. Genet Program Evol Mach 5:11–29

Angeline PJ, Pollack J (1993) Evolutionary module acquisition. In: Proceedings of the 2nd annual conference on evolutionary programming, San Diego, pp 154–163

Bernasconi A, Ciriani V, Cordone R (2008) On projecting sums of products, In: Proceedings of the 11th EUROMICRO conference on digital system design architectures, methods and tools (DSD ’08), pp 787–794

Bernasconi A, Ciriani V, Luccio F (2010) Compact DSOP forms derived from SOP expressions. Universit‘a di Pisa. Technical report: TR-10-21, 1 Dec 2010

Coello CAC, Luna EH, Aguirre AH (2003) Use of particle swarm optimization to design combinational logic circuits. In: Proceedings ICES, LNCS, vol 2606, pp 398–409

Djupdal A, Haddow PC (2007) Evolving redundant structures for reliable circuits–lessons learned. In: Proceedings of adaptive hardware and systems, pp 455–462

Garvie M, Thompson A (2003) Evolution of self-diagnosing hardware. In: Proceedings of international conference on evolvable systems: from biology to hardware (ICES2003), 17–20 March, Trondheim, Norway, pp 238–248

Gordon TGW, Bentley PJ (2005) Development brings scalability to hardware evolution. In: Proceedings of the 2005 NASA/DoD conference of evolution hardware, 29 June–1 July, Washington DC, USA, pp 272–279

Greenwood GW (2009) Is it time to stop evolving digital systems?. In: Proceedings of IEEE workshop on evolvable and adaptive hardware, (WEAH’09). Nashville, Tennessee, April 30–March 2, pp 54–58

Greenwood G, Joshi M (2009) Evolving fault tolerant digital circuitry: comparing population-based and correlation-based methods. In: Proceedings of IEEE congress on evolutionary computation, CEC’09. Trondheim, Norway, May 18–21, pp 2796–2801

Haddow PC, Tyrrell AM (2011) Challenges of evolvable hardware: past, present, and the path to a promising future. Genet Program Evolvable Mach 12:183–215

Kalganova T (2000) An extrinsic function-level evolvable hardware approach. In: Poli R, Banzhaf W, Langdon WB, Miller J, Nordin P, Fogarty TC (eds) Proceedings of the 3rd European conference on genetic programming (EuroGP2000), Edinburgh. Lecture notes in computer science, vol 1802. Springer, Berlin, pp 60–75

Koza JR (1994) Genetic programming II: automatic discovery of reusable subprograms. MIT Press, Cambridge

Kung CK, Liu FT, Chen YJ (2010) Logic circuit design by neural network and PSO algorithm. In: Proceedings of 2010 first international conference on pervasive computing signal processing and applications (PCSPA), Harbin, China, 17–19 Sept 2010

Li ZF, Luo WJ, Wang XF (2008) A stepwise dimension reduction approach to evolutionary design of relative large combinational logic circuits. In: Proceedings of ICES 2008, LNCS, vol 5216, pp 47–58

Liang HJ, Luo WJ, Wang XF (2009) A three-step decomposition method for the evolutionary design of sequential logic circuits. Genet Program Evol Mach 10:231–262

Miller JF, Thomson P (2000) Cartesian genetic programming. In: Proceedings of Europe genetic programming, 15–16 April, Edinburgh, Scotland, UK, pp 121–132

Saeidinezhad H (2012) Reversible circuit optimization using PSO algorithm. In: Proceedings of international conference on computer science, engineering and technology (ICCSET 2012), 7–8 June 2012

Santini CC, José FM, Amaral MAC (2004) Pacheco, evolvability and reconfigurability. In: Proceedings of 2004 IEEE international conference on field-programmable technology, 6–8 December, Brisbane, Australia, pp 105–122

Sekanina L (2002) Image filter design with evolvable hardware. In: Proceedings of Evo workshops 2002, LNCS 2279, pp 255–266

Sekanina L (2012) Two-step evolution of polymorphic circuits for image multi-filtering. In: Proceedings of IEEE world congress on computational intelligence (WCCI 2012), Brisbane, Australia, 10–15 June 2012

Sekanina L, Vasicek Z (2012) A SAT-based fitness function for evolutionary optimization of polymorphic circuits. In: Proceedings of 2012 Design, automation and test in Europe conference and exhibition (DATE), pp 715–720

Shanthi AP, Parthasarathi R (2009) Practical and scalable evolution of digital circuits. Appl Soft Comput 9:618–624

Shanthi AP, Singaram LK, Parthasarathi R (2005) Evolution of asynchronous sequential circuits. In: Proceedings of the 2005 NASA/DoD conference of evolution hardware, 29 June–1 July, Washington DC, USA, pp 238–248

Stoica A, Zebulum RS, Keymeulen D (2002) On two new trends in evolvable hardware: employment of HDL-based structuring, and design of multi-functional circuits. In: Proceedings of 2002 NASA/DoD conference on evolvable hardware, pp 56–59

Stomeo E, Kalganova T (2004) Improving EHW performance introducing a new decomposition strategy. In: Proceedings of the 2004 IEEE conference on cybernetics and intelligent systems, Singapore, 1–3 December, pp 439–44

Stomeo E, Kalganova T (2006) Cyrille lambert generalized disjunction decomposition for the evolution of programmable logic array structures. In: Proceedings of the first NASA/ESA conference on adaptive hardware and systems (AHS’06)

Stomeo E, Kalganova T, Lambert C (2006) Generalized disjunction decomposition for evolvable hardware. IEEE Trans Syst Man Cybern Part B 36(5):1024–1043

Tao YY, Cao J, Zhang YZ (2012) Using module-level evolvable hardware approach in design of sequential logic circuits. In: Proceedings of 2012 IEEE world congress on computational intelligence, Springer, New York, pp 1604–1611

Tao YY, Zhang YZ, Cao J (2013) A module-level three-stage approach to the evolutionary design of sequential logic circuits. Genet Program Evol Mach 14(2):1–29

Torresen J (1998) A divide-and-conquer approach to evolvable hardware. In: Proceedings of evolvable systems: from biology to hardware, pp 57–65

Vasicek Z, Sekanina L (2011) Formal verification of candidate solutions for post-synthesis evolutionary optimization in evolvable hardware. Genet Program Evol Mach 12(3):305–327

Walker JA, Miller JF (2005) Investigating the performance of module acquisition in cartesian genetic programming. In: Proceedings of Genetic and evolutionary computation conference, Washington, pp 1649–1656

Walker JA, Hilder JA, Tyrrell AM (2008) Evolving variability-tolerant CMOS designs. In: Proceedings of the international conference on evolvable systems: from biology to hardware, pp 308–319

Yao X, Higuch T (1996) Promises and challenges of evolvable hardware. In: Proceedings of international conference on evolvable systems: from biology to hardware (ICES96) (Tsukuba, 1996), pp 55–78

Zhang J, Shi Y, Zhan ZH (2008) Power electronic circuits design: a particle swarm optimization approach. In: Li X et al (eds) The seventh international conference on simulated evolution and learning, SEAL 2008, LNCS 5361, pp 605–614

Acknowledgments

This research is supported by the National Science Fund of China(Grant No. 61272105), the Science Fund of the JiangSu Higher Education of China (Grant No. 13KJB520023), and the Youth Teacher Science Fund of Soochow University (Grant No. SD2013A16).

Author information

Authors and Affiliations

Corresponding author

Additional information

Communicated by R. Cerulli.

Rights and permissions

About this article

Cite this article

Tao, Y., Zhang, L. & Zhang, Y. A projection-based decomposition for the scalability of evolvable hardware. Soft Comput 20, 2205–2218 (2016). https://doi.org/10.1007/s00500-015-1636-2

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00500-015-1636-2