Abstract

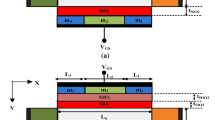

To remove simultaneously the ambipolar conduction and enhance HF performances, we propose a promising configuration of DG-TFET with asymmetric gate–drain overlap (ASGDO DG-TFET) in which only back gate is overlapped with drain region. This proposed structure of DG-TFET removes the trade-off between ambipolarity and HF performances by taking the merit of gate–drain overlap in terms of reduction in ambipolarity and suppressing its demerit with reduced gate–drain parasitic capacitance. Using 2-D simulation, it is observed that ambipolar conduction can be suppressed to a large extent in DG-TFET with only 20 nm of back gate–drain overlap, thus not limiting the scaling of drain region compared to symmetric gate–drain overlap DG-TFET (SGDO DG-TFET). Due to the presence of enhanced depletion layer in the drain region caused by a large vertical electrical field, tunneling width at drain–channel interface is found to be maximum in the proposed device, which eventually prevents the charge carriers to tunnel. Furthermore, ASGDO improves the HF performance parameters such as cutoff frequency and gain–bandwidth product compared to SGDO due to reduction in gate–drain parasitic capacitance, and this improvement is found to be consistent while scaling down the channel length.

Similar content being viewed by others

References

M.J. Kumar, S. Janardhanan, Doping-less tunnel field effect transistor: design and investigation. IEEE Trans. Electron Devices 60(10), 3285–3290 (2013)

K.K. Bhuwalka, S. Sedlmaier, A.K. Ludsteck, C. Toksdorf, J. Schulz, I. Eisele, Vertical tunnel field effect transistor. IEEE Trans. Electron Devices 51(2), 279–282 (2004)

J. Appenzeller, Y.M. Lin, J. Knoch, P. Avouris, Band-to-band tunneling in carbon nanotube field effect transistors. Phys. Rev. Lett. 93(19), 196805-1–196805-4 (2004)

W.Y. Choi, B.-G. Park, J.D. Lee, T.-J.K. Liu, Tunneling field effect transistors (TFETs) with subthreshold swing (SS) less than 60 mv/dec. IEEE Electron Device Lett. 28(8), 743–745 (2007)

V. Nagavarapu, R. Jhaveri, J.C.S. Woo, The tunnel source (PNPN) n-MOSFET: a novel high performance transistor. IEEE Trans. Electron Devices 55(4), 1013–1019 (2008)

A.M. Ionescu, H. Riel, Tunnel field-effect transistors as energy-efficient electronic switches. Nature 479(73), 329–337 (2011)

M.L. Lee et al., Strained Si, SiGe, and Ge channels for high-mobility metal-oxide-semiconductor field-effect transistors. Appl. Phys. Rev. 97(1), 011101 (2005)

S.K. Mitra, R. Goswami, B. Bhowmick, A hetero-dielectric stack gate SOI-TFET with back gate and its application as a digital inverter. Superlattices Microstruct. 92, 37–51 (2016)

S. Blaeser et al., Novel SiGe/Si line tunneling TFET with high Ion at low VDD and constant SS, in Proceedings of IEDM (2015), pp. 22.3.1–22.3.4

S.H. Kim, H. Kam, C. Hu, T.-J.K. Liu, Germanium-source tunnel field effect transistors with record high ION/IOFF, in VLSI Technical Digest (2009), pp. 178–179

C. Wu, Q. Huang, Y. Zhao, J. Wang, Y. Wang, R. Huang, A novel tunnel FET design with stacked source configuration for average sub-threshold swing reduction. IEEE Trans. Electron Devices 63(1), 5072–5076 (2016)

K.-H. Kao et al., Optimization of gate-on-source-only tunnel FETs with counter-doped pockets. IEEE Trans. Electron Devices 59(8), 2070–2077 (2012)

K. Boucart, W. Riess, A.M. Ionescu, Lateral strain profile as key technology booster for all-silicon tunnel FETs. IEEE Electron Device Lett. 30(6), 656–658 (2009)

S. Chander, B. Bhowmick, S. Baishya, Heterojunction fully depleted SOI-TFET with oxide/source overlap. Superlattices Microstruct. 86, 43–50 (2015)

K. Boucart, A.M. Ionescu, Double-gate tunnel FET with high-κ gate dielectric. IEEE Trans. Electron Devices 54(7), 1725–1733 (2007)

S. Ahish, D. Sharma, Y.B.N. Kumar, M.H. Vasantha, Performance enhancement of novel InAs/Si hetero double-gate tunnel FET using Gaussian doping. IEEE Trans. Electron Devices 63(1), 288–295 (2016)

S. Saurabh, M.J. Kumar, Novel attributes of a dual material gate nanoscale tunnel field-effect transistor. IEEE Trans. Electron Devices 58(2), 404–410 (2011)

C.K. Pandey, S. Chaudhury, A novel structure of double-gate tunnel FET with extended back gate for improved device performances, in 2nd International Conference on Innovations in Electronics, Signal Processing and Communication (IESC) 2019 (2019), pp. 72–75

A.S. Verhulst, W.G. Vandenberghe, K. Maex, G. Groeseneken, Tunnel field-effect transistor without gate–drain overlap. Appl. Phys. Lett. 91(5), 053102 (2007)

D.B. Abdi, M.J. Kumar, Controlling ambipolar current in tunneling FETs using overlapping gate-on-drain. IEEE J. Electron Devices Soc. 2(6), 187–190 (2014)

C.K. Pandey, D. Dash, S. Chaudhury, Impact of dielectric pocket on analog and high-frequency performances of cylindrical gate-all-around tunnel FETs. ECS J. Solid State Sci. 7(5), 59–66 (2018)

S. Garg, S. Saurabh, Suppression of ambipolar current in tunnel FETs using drain pocket: proposal and analysis. Superlattices Microstruct. 113, 261–270 (2018)

C.K. Pandey, D. Dash, S. Chaudhury, Approach to suppress ambipolar conduction in tunnel FET using dielectric pocket. Micro Nano Lett. 14(1), 86–90 (2019)

A. Shaker, M. Sabbagh, M.M. El-Banna, Influence of drain doping engineering on the ambipolar conduction and high-frequency performance of TFETs. IEEE Trans. Electron Devices 64(9), 3541–3547 (2017)

S. Sahay, M. Kumar, Controlling the drain side tunneling width to reduce ambipolar current in tunnel FETs using heterodielectric BOX. IEEE Trans. Electron Devices 62(11), 3882–3886 (2015)

TCAD Sentaurus Device Version J-2014.09, http://www.synopsys.com

J. Colinge, J.C. Alderman, W. Xiong, C.R. Cleavelin, Quantummechanical effects in trigate SOI MOSFETs. IEEE Trans. Electron Devices 53(45), 1131–1136 (2006)

S. Zhang, R. Han, J.K.O. Sin, M. Chan, Implementation and characterization of self-aligned double-gate TFT with thin channel and thick source/drain. IEEE Trans. Electron Devices 49(5), 718–724 (2002)

H.S. Wong, K. Chan, Y. Taur, Self-aligned (top and bottom) double-gate MOSFET with a 25 nm thick silicon channel, in IEDM Technical Digest (1997), pp. 427–430

C. Jahan, O. Faynot, L. Tosti, J.M. Hartmann, Agglomeration control during the selective epitaxial growth of Si raised sources and drains on ultra-thin silicon-on-insulator substrates. J. Cryst. Growth 280(3–4), 530–538 (2005)

M. Kumar, S. Sahay, Controlling BTBT-induced parasitic BJT action in junctionless FETs using a hybrid channel. IEEE Trans. Electron Devices 63(8), 3350–3353 (2016)

V. Vijayvargiya, S.K. Vishvakarma, Effect of drain doping profile on double-gate tunnel field-effect transistor and its influence on device RF performance. IEEE Trans. Nanotechnol. 13(5), 974–981 (2014)

S. Mookerjea, R. Krishnan, S. Datta, V. Narayanan, Effective capacitance and drive current for tunnel FET (TFET) CV/I estimation. IEEE Trans. Electron Devices 56(9), 2092–2098 (2009)

Y. Yang, X. Tong, L.-T. Yang, P.-F. Guo, L. Fan, Y.-C. Yeo, Tunneling field-effect transistor: capacitance components and modeling. IEEE Electron Device Lett. 31(7), 752–754 (2010)

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Pandey, C.K., Singh, A. & Chaudhury, S. Effect of asymmetric gate–drain overlap on ambipolar behavior of double-gate TFET and its impact on HF performances. Appl. Phys. A 126, 225 (2020). https://doi.org/10.1007/s00339-020-3402-2

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s00339-020-3402-2