Abstract

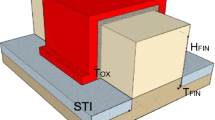

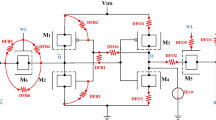

In this paper, we report a junctionless FinFET-based capacitor less dynamic memory by using three-dimensional technology computer-aided design simulations. To realize the 1T-DRAM, the proposed device has been designed as a structure in which a poly-si layer is deposited on the fins of a typical junctionless FinFET. Poly-si has one or more grain boundaries (GB). A GB contains multiple traps, and these traps generally degrade device performance. Also, when poly-si is grown and utilized in semiconductor devices, non-uniform GB is formed across the entire wafer. Therefore, devices manufactured using poly-si have different GBs for each device and the performance of devices fabricated on the same wafer is different. Therefore, it is essential to design a device that can operate normally regardless of GB. The 1T-DRAM proposed in this study was simulated with the existence of GB and the direction of GB differently. Finally, a device that operates normal memory regardless of GB was designed. According to the simulation results, the retention time of the proposed 1T-DRAM has a margin of more than 10 uA/um and a retention time of more than 64 ms, regardless of the presence or absence of GBs.

Similar content being viewed by others

References

M.R. Tack, M. Gao, G.L. Claeys, G.J. Declerck, The Multistable charge-controlled memory effect in SOI MOS transistors at low temperatures. IEEE Trans. Electron Devices 37(5), 1373–1382 (1990)

A. Biswas, N. Dagekin, W. Grabinski, A. Bazigos, C.L. Royer, J.M. Hartmann, C. Tabone, M. Vinet, A.M. Lonescu, Investigation of tunnel field-effect transistors as a capacitor-less memory cell. Appl. Phys. Lett. 104(9), 092108 (2014)

A. Biswas, A.M. Lonescu, 1T capacitor-less DRAM cell based on asymmetric tunnel FET design. IEEE J. Electron Devices Soc. 3(3), 217–222 (2015)

S. Okhonin, M. Nagoga, J.M. Sallese, P. Fazan, A capacitor-less 1T-DRAM cell. IEEE Electron Device Lett. 23(2), 85–87 (2002)

H. J. Wann, C. Hu (eds) A capacitorless DRAM cell on SOI substrate, in Proceedings of IEEE International Electron Device Meeting, Washington DC, USA, 1993, pp 26.4.1–26.4.4

S. Okhonin, M. Nagoga, J. M. Sallese, P. Fazan (eds) A SOI Capacitor-less 1T-DRAM Concept, in Proceedings of IEEE International SOI Conference, Durango, CO, USA, 2001, pp 153–154

E. Yoshida, T. Tanaka, A capacitorless 1T-DRAM technology using gate-induced drain-leakage (GIDL) current for low-power and high-speed embedded memory. IEEE Trans. Electron Devices 53(4), 692–697 (2006)

G. Guegan, P. Touret, G. Molas, C. Raynaud, J. Pretet, A Novel Capacitor-less 1T-DRAM on Partially Depleted SOI pMOSFET Based on Direct-tunneling Current in the Partial n+ Poly Gate, in Proceedings of Extended Abstracts on Solid State Devices and Materials, Miyagi, Japan, 2009, pp 446–447

I. M. Kang, Y. J. Yoon, Semiconductor device and method for manufacturing the same, South Korea Patent 10-1922936-0000, filed November 9, 2018, and issued November 22, 2018

E.O. Kane, Theory of tunneling. J. Appl. Phys. 32(1), 83–91 (1961)

K.H. Kao, A.S. Verhulst, W.G. Vandenberghe, B. Soree, G. Groeseneken, K.D. Meyer, Direct and indirect band-to-band tunneling in germanium-based TFETs. IEEE Trans. Electron Devices 59(2), 292–301 (2012)

C. Rivas, R. Lake, G. Klimeck, W.R. Frensley, M.V. Fischetti, P.E. Thompson, S.L. Rommel, P.R. Berger, Full-band simulation of indirect phonon assisted tunneling in a silicon tunnel diode with delta-doped contact. Appl. Phys. Lett. 78(6), 814–816 (2001)

C. Rivas, Full bandstructure modeling of indirect phonon assisted trans-port in tunnel devices with silicon contacts. Ph. D. dissertation, Dept. Elect. Eng, Univ. Texas, Dallas, TX, (2003)

International Technology Roadmap for Devices and Systems (IRDS) (https://irds.ieee.org)

M.S. Ram, D.B. Abdi, Performance investigation of single grain boundary junctionless field effect transistor. J. Electron Devices Soc 4(6), 480–484 (2016)

C.L. Wang, I.C. Lee, C.Y. Wu, C.H. Chou, P.Y. Yang, Y.T. Cheng, H.C. Cheng, High-performance polycrystalline-silicon nanowire thin-film transistors with location-controlled grain boundary via excimer laser crystallization. IEEE Electron Device Lett. 33(11), 1562–1564 (2012)

P. F. Chou, The case study of poly-silicon grain size and resistance, in IEEE International Reliability Physics Symposium (IRPS), Anaheim, CA, USA, 2012, pp. FA. 1

M. Kimura, T. Yoshino, K. Harada, Complete extraction of trap densities in poly-si thin-film transistors. IEEE Trans. Electron Devices 57(12), 3426–3433 (2010)

P.M. Walker, H. Mizuta, S. Uno, Y. Furuta, D.G. Hasko, Improved off-current and subthreshold slope in aggressively scaled poly-si TFTs with a single grain boundary in the channel. IEEE Trans. Electron Devices 51(2), 212–219 (2004)

C.A. Dimitriadis, Grain boundary trap distribution in polycrystalline silicon thin-film transistors. J. Appl. Phys. 73(8), 4086–4088 (1998)

I. Yamamoto, H. Kuwano, Determination of the energy distribution of grain boundary traps in polycrystalline silicon films. Jpn. J. Appl. Phys. 31(10A), 1381–1383 (1992)

W.D. Jang, Y.J. Yoon, M.S. Cho, J.H. Jung, S.H. Lee, J. Jang, J.-H. Bae, I.M. Kang, Polycrystalline silicon metal-oxide-semiconductor field-effect transistor-based stacked multi-layer one-transistor dynamic random-access memory with double-gate structure for the embedded systems. Jpn. J. Appl. Phys. 59, SGGB01 (2020)

Y.J. Yoon, M.S. Cho, B.G. Kim, J.H. Seo, I.M. Kang, Capacitorless one-transistor dynamic random-access memory based on double-gate metal-oxide-semiconductor field-effect transistor with Si/SiGe heterojunction and underlap structure for improvement of sensing margin and retention time. J. Nanosci. Nanotechnol. 19(10), 6023–6030 (2019)

Y.J. Yoon, J.H. Seo, I.M. Kang, Cpacitorless one-transistor dynamic random-access memory based on asymmetric double-gate Ge/GaAs-heterojunction tunneling field-effect transistor with n-doped boosting layer and drain-underlap structure. Jpn. J. Appl. Phys. 57(4S), 04FG03 (2018)

M.H.R. Ansari, N. Navlakha, J.-T. Lin, A. Kranti, 1T-DRAM with shell-doped architecture. IEEE Trans. Electron Devices 66(1), 428–435 (2019)

Md.H.R. Ansari, N. Navlakha, J.Y. Lee, S. Cho, Double-gate junctionless 1T DRAM with physical barriers for retention improvement. IEEE Trans. Electron Devices 67(4), 1471–1479 (2020)

J.-T. Lin, W.-H. Lee, S.W. Haga, Y.-R. Chen, A. Kranti, A new electron bridge channel 1T-DRAM employing underlap region charge storage. IEEE J Electron Devices Soc 5(1), 59–63 (2017)

Acknowledgements

This work was supported in part by the National Research Foundation of Korea (NRF) funded by the Korea Government Ministry of Science and ICT (MSIT) under Grant NRF-2020R1A2C1005087, in part by Samsung Electronics Company Ltd., in part by the BK21 Plus Project funded by the Ministry of Education, South Korea, under Grant 21A20131600011, in part by the Ministry of Trade, Industry, and Energy (MOTIE) under Grant 10080513, in part by the Korea Semiconductor Research Consortium (KSRC) Support Program for developing the future semiconductor devices, in part by the NRF funded by the Korean Government, through the Global Ph.D. Fellowship Program, under Grant NRF-2018H1A2A1063117, and in part by the IC Design Education Center (IDEC), South Korea

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Cho, M.S., Mun, H.J., Lee, S.H. et al. Simulation of capacitorless dynamic random access memory based on junctionless FinFETs using grain boundary of polycrystalline silicon. Appl. Phys. A 126, 943 (2020). https://doi.org/10.1007/s00339-020-04125-w

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s00339-020-04125-w